- Page 1: SERWIS ELEKTRONIKI1/2003 Styczeñ 2

- Page 9 and 10: Naprawy dla dociekliwychOTVC Philip

- Page 11 and 12: Cyfrowy odbiornik satelitarny Humax

- Page 13 and 14: [[[Cyfrowy odbiornik satelitarny Hu

- Page 15 and 16: [[[Cyfrowy odbiornik satelitarny Hu

- Page 17 and 18: Wykaz g³owic laserowych (mechanizm

- Page 19 and 20: OTVC Telestar 4055TSchemat ideowy O

- Page 21 and 22: OTVC Telestar 4055TPLEASE LOOK AT T

- Page 23 and 24: Chassis NEI CE25/CE28 - uwagi serwi

- Page 25 and 26: Chassis NEI CE25/CE28 - uwagi serwi

- Page 27 and 28: Z³¹cza odbiorników samochodowych

- Page 29 and 30: Odpowiadamy na listy CzytelnikówOd

- Page 31 and 32: W powy¿szej poradzie ograniczy³em

- Page 33 and 34: Uk³ad TA8751AN firmy Toshiban.15 -

- Page 35 and 36: !!!!!!!!!!Naprawa zasilacza magneto

- Page 37 and 38: Zasilacz OTVC Thomson chassis ICC17

- Page 39 and 40: Zasilacz OTVC Thomson chassis ICC17

- Page 41 and 42: BU... - wysokonapiêciowe tranzysto

- Page 43 and 44: Stereofoniczny zestaw RCD-750 firmy

- Page 45 and 46: correction (RA2)).n.49 - wyjœcie u

- Page 47 and 48: Odtwarzacze CD Philips CD604 i CD61

- Page 49 and 50: Opis magistrali szeregowej 1-wireOp

- Page 51 and 52: Opis magistrali szeregowej 1-wire1k

- Page 53 and 54:

Opis magistrali szeregowej 1-wireda

- Page 55 and 56:

Opis magistrali szeregowej 1-wireJe

- Page 57 and 58:

Chassis NEI CE25/CE28 - uwagi serwi

- Page 59 and 60:

Chassis NEI CE25/CE28 - uwagi serwi

- Page 61 and 62:

Uk³ad TA1276AFG firmy ToshibaMaria

- Page 63 and 64:

Uk³ad TA1276AFG firmy Toshiban.7 -

- Page 65 and 66:

Opis aparatu telefonicznego C-803 f

- Page 67 and 68:

Spis treœci „Serwisu Elektroniki

- Page 69 and 70:

Spis treœci „Serwisu Elektroniki

- Page 71 and 72:

[[[[[[Cyfrowy odbiornik satelitarny

- Page 73 and 74:

[[[Cyfrowy odbiornik satelitarny Hu

- Page 75 and 76:

[[[Cyfrowy odbiornik satelitarny Hu

- Page 77 and 78:

Odpowiadamy na listy Czytelnikówst

- Page 79 and 80:

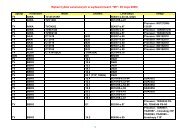

SERWIS ELEKTRONIKI 2/2003 43ModelLa

- Page 81 and 82:

Monitor CMC1414BA(E) firmy DaewooMo

- Page 83 and 84:

Odtwarzacze CD Philips CD604 i CD61

- Page 85 and 86:

iegi: TL (Track loss output signal)

- Page 87 and 88:

OTVC Samsung z chassis S15A - napra

- Page 89 and 90:

Z³¹cza odbiorników samochodowych

- Page 91 and 92:

Serwis wybranych magnetowidów firm

- Page 93 and 94:

Zasilacz chassis ICC17Zasilacz chas

- Page 95 and 96:

Zasilacz chassis ICC173.8.2. Uk³ad

- Page 97 and 98:

SERWIS ELEKTRONIKI3/2003 Marzec 200

- Page 99 and 100:

Wyjœcie z trybu serwisowego nastê

- Page 101 and 102:

Opis magistrali szeregowej 1-wire (

- Page 103 and 104:

Opis magistrali szeregowej 1-wire8.

- Page 105 and 106:

Opis magistrali szeregowej 1-wirere

- Page 107 and 108:

Monitor Mag MX17SNa wyjœciu przetw

- Page 109 and 110:

[[[[Cyfrowy odbiornik satelitarny H

- Page 111 and 112:

Cyfrowy odbiornik satelitarny Humax

- Page 113 and 114:

Cyfrowy odbiornik satelitarny Humax

- Page 115 and 116:

OTVC Royal 3735a OTVC Royal 3735a34

- Page 117 and 118:

Zasilacz chassis ICC17Zasilacz chas

- Page 119 and 120:

Odbiornik samochodowy Pioneer KEX-M

- Page 121 and 122:

Odbiornik samochodowy Pioneer KEX-M

- Page 123 and 124:

Odbiornik samochodowy Pioneer KEX-M

- Page 125 and 126:

Przetwornica OTVC Samsung z uk³ada

- Page 127 and 128:

Wykaz g³owic laserowych (mechanizm

- Page 129 and 130:

Przegl¹d scalonych wzmacniaczy wiz

- Page 131 and 132:

!P1101VJS3306AC INLETC111647µ35V+F

- Page 133 and 134:

OTVC Grundig jako dodatkowy monitor

- Page 135 and 136:

Odpowiadamy na listy CzytelnikówOd

- Page 137 and 138:

pracy. Mniejsze s¹ w trybie czuwan

- Page 139 and 140:

Tryb serwisowy OTVC Loewe z chassis

- Page 141 and 142:

Tabela 4.Type Art. nr VAR EAROM Typ

- Page 143 and 144:

Opis magistrali szeregowej 1-wireOp

- Page 145 and 146:

Opis magistrali szeregowej 1-wire64

- Page 147 and 148:

gramuj¹cego. Ten algorytm ma zasto

- Page 149 and 150:

Naprawy dla dociekliwych - OTVC Pal

- Page 151 and 152:

Cyfrowy odbiornik satelitarny Humax

- Page 153 and 154:

Cyfrowy odbiornik satelitarny Humax

- Page 155 and 156:

Dobór trafopowielacza w telewizora

- Page 157 and 158:

Dobór trafopowielacza w telewizora

- Page 159 and 160:

Wykaz g³owic laserowych (mechanizm

- Page 161 and 162:

32 SERWIS ELEKTRONIKI 4/2003Schemat

- Page 163 and 164:

++Schemat ideowy monitora Daewoo CM

- Page 165 and 166:

Odbiornik samochodowy Pioneer KEX-M

- Page 167 and 168:

Uk³ad TDA2595 firmy PhilipsSchemat

- Page 169 and 170:

Procedury u³atwiaj¹ce naprawê ze

- Page 171 and 172:

Naprawa mechanizmu prowadzenia taœ

- Page 173 and 174:

Odpowiadamy na listy CzytelnikówW

- Page 175 and 176:

Odpowiadamy na listy Czytelnikówi

- Page 177 and 178:

Monitor Daewoo CMC531XMonitor Daewo

- Page 179 and 180:

Monitor Daewoo CMC531X- tak - niepr

- Page 181 and 182:

MIP0221SY ÷ MIP0227SY - uk³ady fi

- Page 183 and 184:

Tryb serwisowy magnetowidów Thomso

- Page 185 and 186:

Uk³ady odchylania chassis ICC17 -

- Page 187 and 188:

Uk³ady odchylania chassis ICC17 -

- Page 189 and 190:

Uk³ady odchylania chassis ICC17 -

- Page 191 and 192:

nowego. Podczas startu na wyprowadz

- Page 193 and 194:

Opis magistrali szeregowej 1-wireOp

- Page 195 and 196:

Opis magistrali szeregowej 1-wireel

- Page 197 and 198:

Opis magistrali szeregowej 1-wireuk

- Page 199 and 200:

Naprawa chassis Sony FE-1Napiêcie

- Page 201 and 202:

Naprawa chassis Sony FE-1Tablica 1.

- Page 203 and 204:

Naprawy dla dociekliwychOTVC Panaso

- Page 205 and 206:

Naprawy dla dociekliwych - OTVC Pan

- Page 207 and 208:

Procedury testowe i informacje serw

- Page 209 and 210:

1N5395GP. Nale¿y równie¿ zmieni

- Page 211 and 212:

Schemat ideowy radiobudzika z odtwa

- Page 213 and 214:

***----*****Schemat ideowy radiobud

- Page 215 and 216:

Cyfrowy odbiornik SAT Mediabox TS2

- Page 217 and 218:

Cyfrowy odbiornik SAT Mediabox TS2

- Page 219 and 220:

Cyfrowy odbiornik SAT Mediabox TS2

- Page 221 and 222:

Naprawa i przeróbka wzmacniacza De

- Page 223 and 224:

Odpowiadamy na listy CzytelnikówOd

- Page 225 and 226:

Odpowiadamy na listy Czytelnikówko

- Page 227 and 228:

Zestawienie parametrów uk³adów M

- Page 229 and 230:

Czym zast¹piæ uk³ad TDA8175?Czym

- Page 231 and 232:

++Czym zast¹piæ uk³ad TDA8175?V

- Page 233 and 234:

Uk³ad TDA3566(A) zamiast TDA3562Ad

- Page 235 and 236:

Przegl¹d chassis stosowanych w OTV

- Page 237 and 238:

Przegl¹d chassis stosowanych w OTV

- Page 239 and 240:

SERWIS ELEKTRONIKI6/2003 Czerwiec 2

- Page 241 and 242:

Zasilacz OTVC Panasonic z chassis M

- Page 243 and 244:

Zasilacz OTVC Panasonic z chassis M

- Page 245 and 246:

Zasilacz OTVC Panasonic z chassis M

- Page 247 and 248:

Analogowo - cyfrowy odbiornik satel

- Page 249 and 250:

cyfrowy, w innym przypadku, nale¿y

- Page 251 and 252:

Uk³ad TA1270BF firmy ToshibaUk³ad

- Page 253 and 254:

Zestawienie chassis firm Siemens i

- Page 255 and 256:

Schemat blokowy radiotelefonu Icom

- Page 257 and 258:

Schemat blokowy radiotelefonu Icom

- Page 259 and 260:

Radiotelefon IC-2800H firmy Icomwyc

- Page 261 and 262:

Radiotelefon IC-2800H firmy IcomSyg

- Page 263 and 264:

40 SERWIS ELEKTRONIKI 6/2003TypZami

- Page 265 and 266:

Miara decybelowaDzielniknapiêciaWz

- Page 267 and 268:

Program testowy zestawów audio AS4

- Page 269 and 270:

Naprawa silnika przesuwu taœmy w o

- Page 271 and 272:

Wymiana pamiêci w OTVC AV-21FT fir

- Page 273 and 274:

Uk³ad odchylania pionowego OTVC Sc

- Page 275 and 276:

Wielofunkcyjny monitorowy procesor

- Page 277 and 278:

Monitorowy procesor wizji i odchyla

- Page 279 and 280:

Monitorowy procesor wizji i odchyla

- Page 281 and 282:

Odpowiadamy na listy CzytelnikówOd

- Page 283 and 284:

Odpowiadamy na listy Czytelnikówzm

- Page 285 and 286:

SERWIS ELEKTRONIKI7/2003 Lipiec 200

- Page 287 and 288:

+++Zasada dzia³ania i metodologia

- Page 289 and 290:

Zasada dzia³ania i metodologia nap

- Page 291 and 292:

Zasada dzia³ania ekranu plazmowego

- Page 293 and 294:

Zasada dzia³ania ekranu plazmowego

- Page 295 and 296:

Zamienne piloty zdalnego sterowania

- Page 297 and 298:

Analogowo - cyfrowy odbiornik satel

- Page 299 and 300:

Analogowo - cyfrowy odbiornik satel

- Page 301 and 302:

Schemat OTVC GoldStar CKT4822 chass

- Page 303 and 304:

Naprawy dla dociekliwychOTVC Sharp

- Page 305 and 306:

Odpowiadamy na listy CzytelnikówOd

- Page 307 and 308:

Odpowiadamy na listy Czytelnikówna

- Page 309 and 310:

„Baza Porad Serwisowych” - 2003

- Page 311 and 312:

Tryb i opcje serwisowe OTVC Sony z

- Page 313 and 314:

Tryb i opcje serwisowe OTVC Sony z

- Page 315 and 316:

Tryb i opcje serwisowe OTVC Sony z

- Page 317 and 318:

SERWIS ELEKTRONIKI 7/2003 47TypZami

- Page 319 and 320:

Opis kamery CCD-VX1/VX3 firmy Sony5

- Page 321 and 322:

Opis kamery CCD-VX1/VX3 firmy SonyS

- Page 323 and 324:

R760, na którym ustalany jest pozi

- Page 325 and 326:

Radiotelefon IC-2800H firmy IcomRad

- Page 327 and 328:

Radiotelefon IC-2800H firmy Icomk)

- Page 329 and 330:

Zestawienie chassis firm Siemens i

- Page 331 and 332:

SERWIS ELEKTRONIKI8/2003 Sierpieñ

- Page 333 and 334:

Zasada dzia³ania i metodologia nap

- Page 335 and 336:

Zasada dzia³ania i metodologia nap

- Page 337 and 338:

Zasada dzia³ania i metodologia nap

- Page 339 and 340:

TDA9365(7) - mikrokontroler, dekode

- Page 341 and 342:

TDA9365(7) - mikrokontroler, dekode

- Page 343 and 344:

TDA9365(7) - mikrokontroler, dekode

- Page 345 and 346:

Tryb serwisowy OTVC Loewe z chassis

- Page 347 and 348:

Schemat ideowy telefonu Atlantel 45

- Page 349 and 350:

Schemat ideowy telefonu Connex BT-9

- Page 351 and 352:

Opis kamery CCD-VX1/VX3 firmy SonyO

- Page 353 and 354:

Opis kamery CCD-VX1/VX3 firmy SonyO

- Page 355 and 356:

Opis kamery CCD-VX1/VX3 firmy SonyJ

- Page 357 and 358:

Procesory dŸwiêku MSP34xx firmy M

- Page 359 and 360:

Procesory dŸwiêku MSP34xx firmy M

- Page 361 and 362:

Odpowiadamy na listy Czytelnikówl

- Page 363 and 364:

SERWIS ELEKTRONIKI 8/2003 45TypZami

- Page 365 and 366:

Chassis Z8 firmy PanasonicChassis Z

- Page 367 and 368:

+Chassis Z8 firmy PanasonicR812C802

- Page 369 and 370:

Chassis Z8 firmy Panasonic1.7. G³

- Page 371 and 372:

Analogowo - cyfrowy odbiornik satel

- Page 373 and 374:

Analogowo - cyfrowy odbiornik satel

- Page 375 and 376:

Zasada dzia³ania i metodologia nap

- Page 377 and 378:

Zasada dzia³ania i metodologia nap

- Page 379 and 380:

Zasada dzia³ania i metodologia nap

- Page 381 and 382:

Uk³ady zasilania w cyfrowych odbio

- Page 383 and 384:

Uk³ady zasilania w cyfrowych odbio

- Page 385 and 386:

Opis procesora TB1238BN firmy Toshi

- Page 387 and 388:

Opis procesora TB1238BN firmy Toshi

- Page 389 and 390:

18 SERWIS ELEKTRONIKI 9/2003TypZami

- Page 391 and 392:

Porady serwisowenie w samym monta¿

- Page 393 and 394:

Porady serwisowedo lokalizacji uszk

- Page 395 and 396:

Porady serwisowe19 uk³adu IC7280 T

- Page 397 and 398:

Porady serwisoweoko³o 3÷4V) odbio

- Page 399 and 400:

Porady serwisoweMonitoryIBM 2124Bra

- Page 401 and 402:

Schemat zasilacza OTVC Samsung chas

- Page 403 and 404:

Chassis Z8 firmy Panasonicra w przy

- Page 405 and 406:

Odpowiadamy na listy Czytelnikówpo

- Page 407 and 408:

Zasilacz chassis GP2D firmy Panason

- Page 409 and 410:

Zasilacz chassis GP2D firmy Panason

- Page 411 and 412:

Zasilacz chassis GP2D firmy Panason

- Page 413 and 414:

Regulacje w trybie serwisowym proje

- Page 415 and 416:

Regulacje w trybie serwisowym proje

- Page 417 and 418:

Uk³ad IPSALO w OTVC Telefunken z c

- Page 419 and 420:

Uk³ad IPSALO w OTVC Telefunken z c

- Page 421 and 422:

Uk³ad scalony TDA6812œciowe,• d

- Page 423 and 424:

Czym zast¹piæ procesor M52309SP?C

- Page 425 and 426:

ReklamaSCHEMATYI CZÊŒCIWSZYSTKOZ

- Page 427 and 428:

InformacjeINFO-NET bêdzie dostêpn

- Page 429 and 430:

Zasady doboru kondensatorów elektr

- Page 431 and 432:

Zasady doboru kondensatorów elektr

- Page 433 and 434:

Zasady doboru kondensatorów elektr

- Page 435 and 436:

Opis chassis 11AK19Opis chassis 11A

- Page 437 and 438:

Opis chassis 11AK19Tabela . O is w

- Page 439 and 440:

Zasilacz komputerowyZasilacz komput

- Page 441 and 442:

Zasilacz komputerowykomputera odpow

- Page 443 and 444:

SERWIS ELEKTRONIKI 10/2003 2932 SER

- Page 445 and 446:

Uk³ady zasilania w cyfrowych odbio

- Page 447 and 448:

Uk³ady zasilania w cyfrowych odbio

- Page 449 and 450:

Opis procesora TB1238BN firmy Toshi

- Page 451 and 452:

SERWIS ELEKTRONIKI 10/2003 39TypZam

- Page 453 and 454:

Uszkodzenia w chassis AE-1 firmy So

- Page 455 and 456:

Uszkodzenia w chassis AE-1 firmy So

- Page 457 and 458:

Montujemy wielosystemow¹ p³ytkê

- Page 459 and 460:

Odpowiadamy na listy Czytelnikówra

- Page 461 and 462:

Opis procesora sygna³owego VSP2860

- Page 463 and 464:

Chassis Z8 firmy PanasonicChassis Z

- Page 465 and 466:

Chassis Z8 firmy Panasonic+8VProtec

- Page 467 and 468:

Naprawy dla dociekliwychOTVC Grundi

- Page 469 and 470:

Uk³ad TDA4505E zamiast TDA4505M-N3

- Page 471 and 472:

Zasady doboru kondensatorów elektr

- Page 473 and 474:

Zasady doboru kondensatorów elektr

- Page 475 and 476:

Zasady doboru kondensatorów elektr

- Page 477 and 478:

Sposób oznaczania diod Zenera firm

- Page 479 and 480:

Opis uk³adu DDP3300A firmy Microna

- Page 481 and 482:

Opis uk³adu DDP3300A firmy Microna

- Page 483 and 484:

Tryb serwisowy OTVC Sony chassis AE

- Page 485 and 486:

Tryb serwisowy OTVC Sony chassis AE

- Page 487 and 488:

Schemat ideowy zasilacza OTVC Phili

- Page 489 and 490:

Uk³ady zabezpieczeñ cyfrowych odb

- Page 491 and 492:

Uk³ady zabezpieczeñ cyfrowych odb

- Page 493 and 494:

Uk³ady zabezpieczeñ cyfrowych odb

- Page 495 and 496:

Regulacje chassis MG5.1E AA firmy P

- Page 497 and 498:

Regulacje chassis MG5.1E AA firmy P

- Page 499 and 500:

Naprawy dla dociekliwych - OTVC Sam

- Page 501 and 502:

korekcja mia³a sens kondensator mu

- Page 503 and 504:

Opis OTVC z chassis MC-84A firmy LG

- Page 505 and 506:

Opis OTVC z chassis MC-84A firmy LG

- Page 507 and 508:

VINWp³yw obci¹¿enia na napiêcie

- Page 509 and 510:

Odpowiadamy na listy Czytelników³

- Page 511 and 512:

SERWIS ELEKTRONIKI12/2003 Grudzieñ

- Page 513 and 514:

Przetwornice napiêcia pracuj¹ce w

- Page 515 and 516:

Przetwornice napiêcia pracuj¹ce w

- Page 517 and 518:

Chassis 11 AK33 firmy VestelChassis

- Page 519 and 520:

Chassis 11 AK33 firmy VestelTablica

- Page 521 and 522:

Tablica . O is w rowadze uk³adu T

- Page 523 and 524:

Opis chassis A10E firmy PhilipsChas

- Page 525 and 526:

Opis chassis A10E firmy Philipsn.49

- Page 527 and 528:

Spis treœci „Serwisu Elektroniki

- Page 529 and 530:

Spis treœci „Serwisu Elektroniki

- Page 531 and 532:

Opis uk³adów rodziny STV223xD i S

- Page 533 and 534:

Opis uk³adów rodziny STV223xD i S

- Page 535 and 536:

SERWIS ELEKTRONIKI 12/2003 37Przegl

- Page 537 and 538:

Fonia równoleg³a na uk³adzie TDA

- Page 539 and 540:

· maksymalny sygna³ wejœæ 1 i 2

- Page 541 and 542:

Zamiana uk³adu TDA8361(62)E/N4 na

- Page 543 and 544:

Naprawy dla dociekliwych - OTVC Sch

- Page 545 and 546:

SDA0SDA1SCL0SCL1ADJPWM0 to PWM5PWMP

- Page 547 and 548:

Opis OTVC z chassis MC-84A firmy LG

- Page 549 and 550:

EEPROM IC02 24C16 wystêpuje koniec

- Page 551 and 552:

Sygnalizacja b³êdów i uszkodzeñ

- Page 553 and 554:

Odpowiadamy na listy CzytelnikówOT