SP - UMEL - Vysoké uÄÂenàtechnické v Brně

SP - UMEL - Vysoké uÄÂenàtechnické v Brně SP - UMEL - Vysoké uÄÂenàtechnické v Brně

Návrh analogových integrovaných obvodů (BNAO) 37technologii rezervováno několik vrstev metalů jen pro routování.). Zpravidla platí, že globálnísignály v jedné metalové vrstvě bývají orientovány ve stejném směru. Další routovací vrstvamá preferovanou orientaci otočenou o 90° a orientace se pravidelně vrstvu od vrstvypravidelně střídá. Toto pravidlo o shodné orientaci signálů neplatí na nejnižší jednu či dvěmetalové vrstvy, protože těchto vrstev se využívá hlavně na lokální úrovni (v rámci bloku čibuňky). Router většinou překrývá samotný layout sítí hypotetických vodičů minimální šířky avzdáleností mezi sebou tak, aby bylo možné umístit na vodiče via či kontakt. Každý z těchtohypotetických vodičů bývá označován jako track.Kritickou částí při tvorbě floorplanu je rozhodnutí o rezervaci jednotlivých signálovýchcest (track) a také o jejich délkách. Pokud signál prochází nad celou buňkou, aniž by došlo knutnosti tento signál kontaktovat, je výhodné v layoutu samotné buňky nepoužívat vyššímetalové vrstvy a pak v takovýchto buňkách nemusí být vůbec obsažen layout tohoto signálu.Signál bude řešen na vyšší úrovni. V případě, kdy potřebujeme takový signál kontaktovat,musí být tento samozřejmě obsažen i v buňce. Může se také stát, že signálový trackkoresponduje na opačných hranicích buňky s různými signály. Občas je potřeba pro potřebylokálního propojování využít i vyšších metalových vrstev běžně používaných pro routing. Vtakových případech je potřeba minimalizovat počet tracků, které tímto budou zasaženy(komplikace při globálním routování). Nesmí se zapomenout na rozvod VSS a VDD, kterémusí být nad každou buňkou!Pokud signály vedou v sousedních buňkách přes celou jejich šířku a na hranici jsou vestejných pozicích, je možné přesunout propojování do vyšší hierarchie. V takovém případě jeeliminován nutný ruční zásah a úpravy routování sousedních buněk. Je ovšem nutné zajistit,aby po umístění buněk vedle sebe byl následný layout vpořádku i z pohledu návrhovýchpravidel.Nejefektivnější opatření, které zaručí, že budou splněna všechna návrhová pravidlauvnitř buněk samotných a i při jejich následném skládání je navrhovat struktury u hranic tak,aby jejich vzdálenost od hranice buňky byla rovna polovině vzdálenosti určené návrhovýmpravidlem. Neplatí to samozřejmě o strukturách, které se sdílejí přes více buněk (nwell oblastiapod.). Pokud je návrhové pravidlo rovno lichému násobku lambda, zavede se pravidlo o tom,ke které hranici bude vzdálenost lichým násobkem. Např. je-li minimální vzdálenost mezidvěma M1 rovna 3 lambda: určíme, že M1 bude od horní a levé hranice 2 lambda a od pravéa spodní hranice 2 lambda. Toto se samozřejmě musí potom dodržovat u všech buněk. Tímtopravidlem zajistíme, že jakákoliv kombinace buněk vedle sebe neporuší toto pravidlo(výjimkou může být případ, kdy je buňka nevhodně rotována nebo zrcadlena). Pokud některébuňky mohou být rotovány, je lepší dodržet u těchto buněk vzdálenost M1 od hranice 2lambda.Dobře připravený floorplan značně zjednoduší a urychlí ručně vytvářený layout, alenesmí se zapomínat, že jde vpodstatě o iterační proces. Tzn., že floorplan se s velkoupravděpodobností několikrát změní ještě i po dokončení layoutu základních funkčních bloků.Změny mohou nastat hlavně v umístění jednotlivých bloků, rezervovaní tracků pro vodiče čipřechody signálů přes hranice různých buněk. Příkladem může být situace, kdy jenaplánováno že signál povede v x-tém tracku, ale toto způsobuje velké problémy v layoutu nalokální úrovni. Většinou je potom jednodušší změnit částečně floorplan než předělávat layoutcelé buňky. Z uvedené situace je vidět, že při návrhu floorplanu bychom měli mít představu ojednotlivých buňkách a jejich obsahu abychom se pokud možno vyhnuli podobným situacím.Nakonec rada: nelitujte času navíc, který strávíte při sestavování floorplanu, protože dobřeudělaný floorplan nakonec znamená velkou úsporu času a námahy při tvorbě samotnéholayoutu

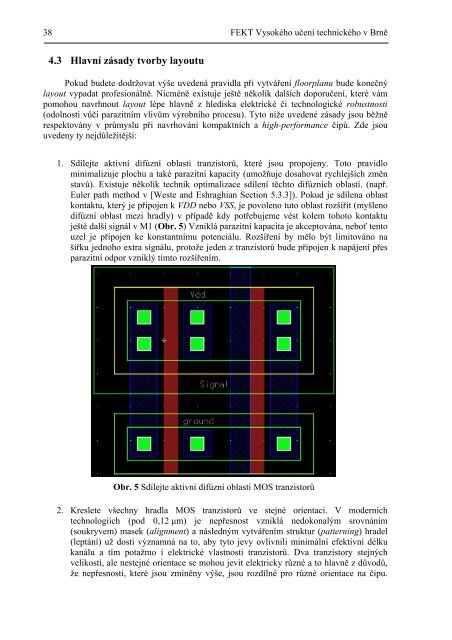

38 FEKT Vysokého učení technického v Brně4.3 Hlavní zásady tvorby layoutuPokud budete dodržovat výše uvedená pravidla při vytváření floorplanu bude konečnýlayout vypadat profesionálně. Nicméně existuje ještě několik dalších doporučení, které vámpomohou navrhnout layout lépe hlavně z hlediska elektrické či technologické robustnosti(odolnosti vůči parazitním vlivům výrobního procesu). Tyto níže uvedené zásady jsou běžněrespektovány v průmyslu při navrhování kompaktních a high-performance čipů. Zde jsouuvedeny ty nejdůležitější:1. Sdílejte aktivní difúzní oblasti tranzistorů, které jsou propojeny. Toto pravidlominimalizuje plochu a také parazitní kapacity (umožňuje dosahovat rychlejších změnstavů). Existuje několik technik optimalizace sdílení těchto difúzních oblastí. (např.Euler path method v [Weste and Eshraghian Section 5.3.3]). Pokud je sdílena oblastkontaktu, který je připojen k VDD nebo VSS, je povoleno tuto oblast rozšířit (myšlenodifúzní oblast mezi hradly) v případě kdy potřebujeme vést kolem tohoto kontaktuještě další signál v M1 (Obr. 5) Vzniklá parazitní kapacita je akceptována, neboť tentouzel je připojen ke konstantnímu potenciálu. Rozšíření by mělo být limitováno našířku jednoho extra signálu, protože jeden z tranzistorů bude připojen k napájení přesparazitní odpor vzniklý tímto rozšířením.Obr. 5 Sdílejte aktivní difúzní oblasti MOS tranzistorů2. Kreslete všechny hradla MOS tranzistorů ve stejné orientaci. V moderníchtechnologiích (pod 0,12 µm) je nepřesnost vzniklá nedokonalým srovnáním(soukryvem) masek (alignment) a následným vytvářením struktur (patterning) hradel(leptání) už dosti významná na to, aby tyto jevy ovlivnili minimální efektivní délkukanálu a tím potažmo i elektrické vlastnosti tranzistorů. Dva tranzistory stejnýchvelikostí, ale nestejné orientace se mohou jevit elektricky různé a to hlavně z důvodů,že nepřesnosti, které jsou zmíněny výše, jsou rozdílné pro různé orientace na čipu.

- Page 1 and 2: Ing. Daniel Bečvář, Ph.D.Ing. Ji

- Page 3 and 4: 2 FEKT Vysokého učení technické

- Page 5 and 6: 4 FEKT Vysokého učení technické

- Page 7 and 8: 6 FEKT Vysokého učení technické

- Page 9 and 10: 8 FEKT Vysokého učení technické

- Page 11 and 12: 10 FEKT Vysokého učení technick

- Page 13 and 14: 12 FEKT Vysokého učení technick

- Page 15 and 16: 14 FEKT Vysokého učení technick

- Page 17 and 18: 16 FEKT Vysokého učení technick

- Page 19 and 20: 18 FEKT Vysokého učení technick

- Page 21 and 22: 20 FEKT Vysokého učení technick

- Page 23 and 24: 22 FEKT Vysokého učení technick

- Page 25 and 26: 24 FEKT Vysokého učení technick

- Page 27 and 28: 26 FEKT Vysokého učení technick

- Page 29 and 30: 28 FEKT Vysokého učení technick

- Page 31 and 32: 30 FEKT Vysokého učení technick

- Page 33 and 34: 32 FEKT Vysokého učení technick

- Page 35 and 36: 34 FEKT Vysokého učení technick

- Page 37: 36 FEKT Vysokého učení technick

- Page 41 and 42: 40 FEKT Vysokého učení technick

- Page 43 and 44: 42 FEKT Vysokého učení technick

- Page 45 and 46: 44 FEKT Vysokého učení technick

- Page 47 and 48: 46 FEKT Vysokého učení technick

- Page 49 and 50: 48 FEKT Vysokého učení technick

- Page 51 and 52: 50 FEKT Vysokého učení technick

- Page 53 and 54: 52 FEKT Vysokého učení technick

- Page 55 and 56: 54 FEKT Vysokého učení technick

- Page 57 and 58: 56 FEKT Vysokého učení technick

- Page 59 and 60: 58 FEKT Vysokého učení technick

- Page 61 and 62: 60 FEKT Vysokého učení technick

- Page 63 and 64: 62 FEKT Vysokého učení technick

- Page 65 and 66: 64 FEKT Vysokého učení technick

- Page 67 and 68: 66 FEKT Vysokého učení technick

- Page 69 and 70: 68 FEKT Vysokého učení technick

- Page 71 and 72: 70 FEKT Vysokého učení technick

- Page 73 and 74: 72 FEKT Vysokého učení technick

- Page 75 and 76: 74 FEKT Vysokého učení technick

- Page 77 and 78: 76 FEKT Vysokého učení technick

- Page 79 and 80: 78 FEKT Vysokého učení technick

- Page 81 and 82: 80 FEKT Vysokého učení technick

- Page 83 and 84: 82 FEKT Vysokého učení technick

- Page 85 and 86: 84 FEKT Vysokého učení technick

- Page 87 and 88: 86 FEKT Vysokého učení technick

38 FEKT Vysokého učení technického v Brně4.3 Hlavní zásady tvorby layoutuPokud budete dodržovat výše uvedená pravidla při vytváření floorplanu bude konečnýlayout vypadat profesionálně. Nicméně existuje ještě několik dalších doporučení, které vámpomohou navrhnout layout lépe hlavně z hlediska elektrické či technologické robustnosti(odolnosti vůči parazitním vlivům výrobního procesu). Tyto níže uvedené zásady jsou běžněrespektovány v průmyslu při navrhování kompaktních a high-performance čipů. Zde jsouuvedeny ty nejdůležitější:1. Sdílejte aktivní difúzní oblasti tranzistorů, které jsou propojeny. Toto pravidlominimalizuje plochu a také parazitní kapacity (umožňuje dosahovat rychlejších změnstavů). Existuje několik technik optimalizace sdílení těchto difúzních oblastí. (např.Euler path method v [Weste and Eshraghian Section 5.3.3]). Pokud je sdílena oblastkontaktu, který je připojen k VDD nebo VSS, je povoleno tuto oblast rozšířit (myšlenodifúzní oblast mezi hradly) v případě kdy potřebujeme vést kolem tohoto kontaktuještě další signál v M1 (Obr. 5) Vzniklá parazitní kapacita je akceptována, neboť tentouzel je připojen ke konstantnímu potenciálu. Rozšíření by mělo být limitováno našířku jednoho extra signálu, protože jeden z tranzistorů bude připojen k napájení přesparazitní odpor vzniklý tímto rozšířením.Obr. 5 Sdílejte aktivní difúzní oblasti MOS tranzistorů2. Kreslete všechny hradla MOS tranzistorů ve stejné orientaci. V moderníchtechnologiích (pod 0,12 µm) je nepřesnost vzniklá nedokonalým srovnáním(soukryvem) masek (alignment) a následným vytvářením struktur (patterning) hradel(leptání) už dosti významná na to, aby tyto jevy ovlivnili minimální efektivní délkukanálu a tím potažmo i elektrické vlastnosti tranzistorů. Dva tranzistory stejnýchvelikostí, ale nestejné orientace se mohou jevit elektricky různé a to hlavně z důvodů,že nepřesnosti, které jsou zmíněny výše, jsou rozdílné pro různé orientace na čipu.