SP - UMEL - Vysoké uÄÂenàtechnické v Brně

SP - UMEL - Vysoké uÄÂenàtechnické v Brně SP - UMEL - Vysoké uÄÂenàtechnické v Brně

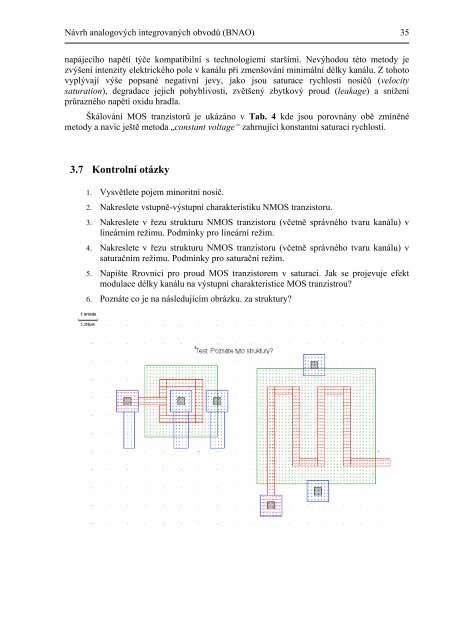

Návrh analogových integrovaných obvodů (BNAO) 35napájecího napětí týče kompatibilní s technologiemi staršími. Nevýhodou této metody jezvýšení intenzity elektrického pole v kanálu při zmenšování minimální délky kanálu. Z tohotovyplývají výše popsané negativní jevy, jako jsou saturace rychlosti nosičů (velocitysaturation), degradace jejich pohyblivosti, zvětšený zbytkový proud (leakage) a sníženíprůrazného napětí oxidu hradla.Škálování MOS tranzistorů je ukázáno v Tab. 4 kde jsou porovnány obě zmíněnémetody a navíc ještě metoda „constant voltage“ zahrnující konstantní saturaci rychlosti.3.7 Kontrolní otázky1. Vysvětlete pojem minoritní nosič.2. Nakreslete vstupně-výstupní charakteristiku NMOS tranzistoru.3. Nakreslete v řezu strukturu NMOS tranzistoru (včetně správného tvaru kanálu) vlineárním režimu. Podmínky pro lineární režim.4. Nakreslete v řezu strukturu NMOS tranzistoru (včetně správného tvaru kanálu) vsaturačním režimu. Podmínky pro saturační režim.5. Napište Rrovnici pro proud MOS tranzistorem v saturaci. Jak se projevuje efektmodulace délky kanálu na výstupní charakteristice MOS tranzistrou?6. Poznáte co je na následujícím obrázku. za struktury?

36 FEKT Vysokého učení technického v Brně4 Layout – tipy a techniky4.1 ÚvodV této kapitole se budeme zabývat vytvářením topologie čipu. Uvedeme několik technika tipů pro vytvoření konzistentního layoutu, který bude zabírat minimální místo na čipu azároveň nebude omezovat výkonnost funkčních bloků a obvodů. Obvykle převod návrhuelektrického obvodu do formy layoutu (fyzického obvodu) dělá layout inženýr (maskdesigner). Samozřejmě je nutné, aby podstatu a principy návrhu topologie chápal i návrhářobvodu a to hlavně z důvodu znalosti kritických míst převodu obvodového návrhu do layoutu.4.2 PlánováníPři vytváření layoutu komplexního obvodu je nutné vytvořit předběžný plán (rozvrh)rozmístění částí systému, podobvodů a propojení mezi nimi. Tento proces se nazýváplánování topologie čipu (layout planning, floorplannig). Pravděpodobně v průběhu projektuzjistíte, že nikoliv počet tranzistorů či jejich velikosti, ale spíše propojovací cesty (routing)mezi funkčními bloky určují plošnou náročnost layoutu. Dobře připravený plán topologie čipuminimalizuje plochu potřebnou pro vedení sběrnic a propojování bloků a také zjednodušujekomplexnost propojování.Jedno z prvních a nejdůležitějších rozhodnutí při vytváření plánu topologie čipu jerozhodnutí ohledně využití vrstev metalů (propojovacích vrstev). Máme konečný početmetalových vrstev a každá vrstva má své specifické vlastnosti (charakteristiky). Příklademmůže být polykrystalický křemík (polySi), který má poměrně vysoký elektrický odpor, alepřesto může být v některých případech využit pro krátké propojky, hlavně pokud jde opropojení hradel jednotlivých MOS tranzistorů. Metal 1 (M1) je poměrně tenkou vrstvous dobrou vodivostí a je poměrně snadno dosažitelný od povrchu wafferu. Z těchto důvodů jevýhodný zvláště pro lokální propojování. Metal 2 (M2) má často ještě nižší rezistivitu(obvykle je tlustší nebo širší) než M1, ale je hůře dostupný a vyžaduje větší minimálnívzdálenosti (spacing). Např. připojení M2 na hradlo MOS tranzistoru vyžaduje prostor procontact, via a dále potřebuje „kontaktní“ plochy vrstev M1, M2 a polySi (tyto kontaktníplochy musí obklopovat vias a kontakty a jsou vždy širší než minimální velikosti šířekpříslušných vrstev). Z těchto důvodů je v technologii s 2 metalovými vrstvami M2 využita proglobální propojovací síť. Vyšší vrstvy metalů, které jsou běžné v dnešních moderníchtechnologiích, jsou často rezervovány pro propojky na větší vzdálenosti a globální signály,které vyžadují cesty s velmi nízkou rezistivitou (rozvod hodinových signálů, síť napájení).Při plánování globálních routovacích cest se často používá pojmů kanál (channel) acesta, spoj (track). Kanály jsou na čipu volná místa mezi funkčními jednotkami systému nebofunkčními bloky (v případě jednodušších čipů), které se využívají pouze pro rozvod signálů,sběrnic a napájecích vodičů. Často mají z důvodů vedení dlouhých sběrnic velmi protáhlýobdélníkový tvar. Protože je v kanále velmi mnoho metalových vrstev využito pro vedenísignálů, je prakticky nemožné umístit do těchto oblastí jiné struktury (MOS tranzistoryapod.). Návrh vedení signálů a sběrnic v kanálech je prováděn zpravidla automaticky.Routovací cesty jsou používány pro organizaci a zjednodušení vedení a propojování signálů vrámci topologické buňky (layout cell, funkční blok) a nad ní (pokud je ve vícemetalové

- Page 1 and 2: Ing. Daniel Bečvář, Ph.D.Ing. Ji

- Page 3 and 4: 2 FEKT Vysokého učení technické

- Page 5 and 6: 4 FEKT Vysokého učení technické

- Page 7 and 8: 6 FEKT Vysokého učení technické

- Page 9 and 10: 8 FEKT Vysokého učení technické

- Page 11 and 12: 10 FEKT Vysokého učení technick

- Page 13 and 14: 12 FEKT Vysokého učení technick

- Page 15 and 16: 14 FEKT Vysokého učení technick

- Page 17 and 18: 16 FEKT Vysokého učení technick

- Page 19 and 20: 18 FEKT Vysokého učení technick

- Page 21 and 22: 20 FEKT Vysokého učení technick

- Page 23 and 24: 22 FEKT Vysokého učení technick

- Page 25 and 26: 24 FEKT Vysokého učení technick

- Page 27 and 28: 26 FEKT Vysokého učení technick

- Page 29 and 30: 28 FEKT Vysokého učení technick

- Page 31 and 32: 30 FEKT Vysokého učení technick

- Page 33 and 34: 32 FEKT Vysokého učení technick

- Page 35: 34 FEKT Vysokého učení technick

- Page 39 and 40: 38 FEKT Vysokého učení technick

- Page 41 and 42: 40 FEKT Vysokého učení technick

- Page 43 and 44: 42 FEKT Vysokého učení technick

- Page 45 and 46: 44 FEKT Vysokého učení technick

- Page 47 and 48: 46 FEKT Vysokého učení technick

- Page 49 and 50: 48 FEKT Vysokého učení technick

- Page 51 and 52: 50 FEKT Vysokého učení technick

- Page 53 and 54: 52 FEKT Vysokého učení technick

- Page 55 and 56: 54 FEKT Vysokého učení technick

- Page 57 and 58: 56 FEKT Vysokého učení technick

- Page 59 and 60: 58 FEKT Vysokého učení technick

- Page 61 and 62: 60 FEKT Vysokého učení technick

- Page 63 and 64: 62 FEKT Vysokého učení technick

- Page 65 and 66: 64 FEKT Vysokého učení technick

- Page 67 and 68: 66 FEKT Vysokého učení technick

- Page 69 and 70: 68 FEKT Vysokého učení technick

- Page 71 and 72: 70 FEKT Vysokého učení technick

- Page 73 and 74: 72 FEKT Vysokého učení technick

- Page 75 and 76: 74 FEKT Vysokého učení technick

- Page 77 and 78: 76 FEKT Vysokého učení technick

- Page 79 and 80: 78 FEKT Vysokého učení technick

- Page 81 and 82: 80 FEKT Vysokého učení technick

- Page 83 and 84: 82 FEKT Vysokého učení technick

- Page 85 and 86: 84 FEKT Vysokého učení technick

Návrh analogových integrovaných obvodů (BNAO) 35napájecího napětí týče kompatibilní s technologiemi staršími. Nevýhodou této metody jezvýšení intenzity elektrického pole v kanálu při zmenšování minimální délky kanálu. Z tohotovyplývají výše popsané negativní jevy, jako jsou saturace rychlosti nosičů (velocitysaturation), degradace jejich pohyblivosti, zvětšený zbytkový proud (leakage) a sníženíprůrazného napětí oxidu hradla.Škálování MOS tranzistorů je ukázáno v Tab. 4 kde jsou porovnány obě zmíněnémetody a navíc ještě metoda „constant voltage“ zahrnující konstantní saturaci rychlosti.3.7 Kontrolní otázky1. Vysvětlete pojem minoritní nosič.2. Nakreslete vstupně-výstupní charakteristiku NMOS tranzistoru.3. Nakreslete v řezu strukturu NMOS tranzistoru (včetně správného tvaru kanálu) vlineárním režimu. Podmínky pro lineární režim.4. Nakreslete v řezu strukturu NMOS tranzistoru (včetně správného tvaru kanálu) vsaturačním režimu. Podmínky pro saturační režim.5. Napište Rrovnici pro proud MOS tranzistorem v saturaci. Jak se projevuje efektmodulace délky kanálu na výstupní charakteristice MOS tranzistrou?6. Poznáte co je na následujícím obrázku. za struktury?