SP - UMEL - Vysoké uÄÂenàtechnické v Brně

SP - UMEL - Vysoké uÄÂenàtechnické v Brně SP - UMEL - Vysoké uÄÂenàtechnické v Brně

Návrh analogových integrovaných obvodů (BNAO) 29Tab. 3: Změny v MOS technologických procesechParametry prvních výrobních procesůParametry současných výrobníchprocesůDélka kanálu 10 µm Délka kanálu 0,1 µmRozměr wafferu 1 inchPlocha čipů 2x2 mmTeplotní oxidaceIzolace oxidemIontová difúzePMOSOdporová zátěžHliníková hradlaHliníkové cesty s 2% dotací mědiRozměr wafferu 300 mmPlocha čipů 1x2 cmDepozice CVDIzolace LOCOS, izolační příkopyIontová implantaceNMOS, CMOSDepletiční zátěž, komplementárnízátěžPolySi/Silicidová, samočinněsoukryvná hradlaMěděné cesty2 hladiny metalových cest bez planarizace Až 6 hladin s planarizací awolframovými spojiNapařování kovuNaprašování kovu2Žíhaní v: H 2 Deuteriu ( H)Namísto klasické tepelné oxidace je dnes využíváno pro vytváření izolačních vrstevchemické napařování (Chemical vapor deposition, CVD). Hlavní výhodou je, ženespotřebovává pro vytvoření oxidové vrstvy křemík, na kterém má být oxidová vrstvavytvořena. Není zde tedy omezení tloušťky této vrstvy a mohou se napařovat i jiné materiálynež SiO 2 (např. Si 3 N 4 ). CVD se také často využívá pro napařování těžko tavitelných kovů jakoje wolfram.Iontová implantace nahradila difúzní proces hlavně díky své přesnosti a homogenitědotace ve vytvářené oblasti. Suché leptání zahrnující reaktivní iontové leptání (RIE) a leptáníiontovým paprskem je náhradou mokrého leptání. Tyto leptací procesy nechávají vícehomogenizované okraje a lépe se kontrolují, stejně jako velmi často využívané anisotropníleptání. Selektivita (tj. odleptávání pouze určitého materiálu) mokrého leptání není s těmitotechnikami dosažitelná, ale je vyvážena dosaženou homogenitou okraje leptaného materiálu.Naprašování plně nahradilo napařování při vytváření metalových struktur. Naprašovánívykazuje lepší přilnavost (adhezi) a také se lépe řídí tloušťka vytvářené vrstvy. Je to takévhodnější technika pro nanášení těžko tavitelných kovů a silicidaci. Silicidace je procespřípravy silicidu kovu. U obvodů VLSI je limitujícím faktorem relativně vysoká hodnotaodporu dopovaného poly-Si a kontaktních odporů. Možnost řešit uvedený problém spočívá vnáhradě polySi vrstvy silicidy těžkých kovů. Zvláště disilicidy WSi 2 , MoSi 2 , TiSi 2 a TaSi 2jsou pro tento účel velmi vhodné, protože mají dostatečně nízký měrný odpor, dobrou teplotnístabilitu, lze je oxidovat a mají nízký kontaktní odpor na hliníkovou metalizaci. Silicidy sedříve připravovali simultánním napařováním obou komponentů ve vakuu.

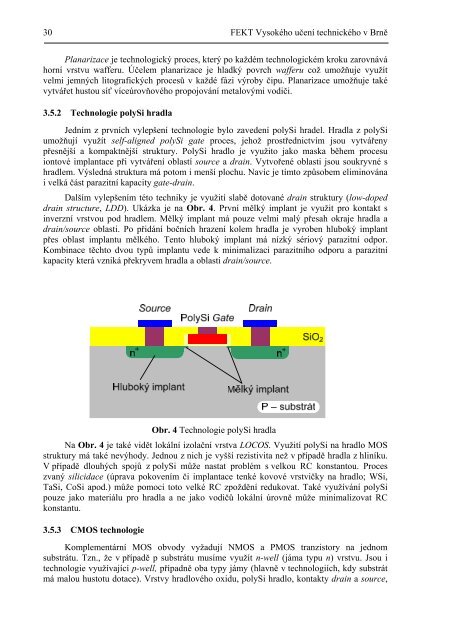

30 FEKT Vysokého učení technického v BrněPlanarizace je technologický proces, který po každém technologickém kroku zarovnáváhorní vrstvu wafferu. Účelem planarizace je hladký povrch wafferu což umožňuje využítvelmi jemných litografických procesů v každé fázi výroby čipu. Planarizace umožňuje takévytvářet hustou síť víceúrovňového propojování metalovými vodiči.3.5.2 Technologie polySi hradlaJedním z prvních vylepšení technologie bylo zavedení polySi hradel. Hradla z polySiumožňují využít self-aligned polySi gate proces, jehož prostřednictvím jsou vytvářenypřesnější a kompaktnější struktury. PolySi hradlo je využito jako maska během procesuiontové implantace při vytváření oblastí source a drain. Vytvořené oblasti jsou soukryvné shradlem. Výsledná struktura má potom i menší plochu. Navíc je tímto způsobem eliminovánai velká část parazitní kapacity gate-drain.Dalším vylepšením této techniky je využití slabě dotované drain struktury (low-dopeddrain structure, LDD). Ukázka je na Obr. 4. První mělký implant je využit pro kontakt sinverzní vrstvou pod hradlem. Mělký implant má pouze velmi malý přesah okraje hradla adrain/source oblasti. Po přidání bočních hrazení kolem hradla je vyroben hluboký implantpřes oblast implantu mělkého. Tento hluboký implant má nízký sériový parazitní odpor.Kombinace těchto dvou typů implantu vede k minimalizaci parazitního odporu a parazitníkapacity která vzniká překryvem hradla a oblasti drain/source.Obr. 4 Technologie polySi hradlaNa Obr. 4 je také vidět lokální izolační vrstva LOCOS. Využití polySi na hradlo MOSstruktury má také nevýhody. Jednou z nich je vyšší rezistivita než v případě hradla z hliníku.V případě dlouhých spojů z polySi může nastat problém s velkou RC konstantou. Proceszvaný silicidace (úprava pokovením či implantace tenké kovové vrstvičky na hradlo; WSi,TaSi, CoSi apod.) může pomoci toto velké RC zpoždění redukovat. Také využívání polySipouze jako materiálu pro hradla a ne jako vodičů lokální úrovně může minimalizovat RCkonstantu.3.5.3 CMOS technologieKomplementární MOS obvody vyžadují NMOS a PMOS tranzistory na jednomsubstrátu. Tzn., že v případě p substrátu musíme využít n-well (jáma typu n) vrstvu. Jsou itechnologie využívající p-well, případně oba typy jámy (hlavně v technologiích, kdy substrátmá malou hustotu dotace). Vrstvy hradlového oxidu, polySi hradlo, kontakty drain a source,

- Page 1 and 2: Ing. Daniel Bečvář, Ph.D.Ing. Ji

- Page 3 and 4: 2 FEKT Vysokého učení technické

- Page 5 and 6: 4 FEKT Vysokého učení technické

- Page 7 and 8: 6 FEKT Vysokého učení technické

- Page 9 and 10: 8 FEKT Vysokého učení technické

- Page 11 and 12: 10 FEKT Vysokého učení technick

- Page 13 and 14: 12 FEKT Vysokého učení technick

- Page 15 and 16: 14 FEKT Vysokého učení technick

- Page 17 and 18: 16 FEKT Vysokého učení technick

- Page 19 and 20: 18 FEKT Vysokého učení technick

- Page 21 and 22: 20 FEKT Vysokého učení technick

- Page 23 and 24: 22 FEKT Vysokého učení technick

- Page 25 and 26: 24 FEKT Vysokého učení technick

- Page 27 and 28: 26 FEKT Vysokého učení technick

- Page 29: 28 FEKT Vysokého učení technick

- Page 33 and 34: 32 FEKT Vysokého učení technick

- Page 35 and 36: 34 FEKT Vysokého učení technick

- Page 37 and 38: 36 FEKT Vysokého učení technick

- Page 39 and 40: 38 FEKT Vysokého učení technick

- Page 41 and 42: 40 FEKT Vysokého učení technick

- Page 43 and 44: 42 FEKT Vysokého učení technick

- Page 45 and 46: 44 FEKT Vysokého učení technick

- Page 47 and 48: 46 FEKT Vysokého učení technick

- Page 49 and 50: 48 FEKT Vysokého učení technick

- Page 51 and 52: 50 FEKT Vysokého učení technick

- Page 53 and 54: 52 FEKT Vysokého učení technick

- Page 55 and 56: 54 FEKT Vysokého učení technick

- Page 57 and 58: 56 FEKT Vysokého učení technick

- Page 59 and 60: 58 FEKT Vysokého učení technick

- Page 61 and 62: 60 FEKT Vysokého učení technick

- Page 63 and 64: 62 FEKT Vysokého učení technick

- Page 65 and 66: 64 FEKT Vysokého učení technick

- Page 67 and 68: 66 FEKT Vysokého učení technick

- Page 69 and 70: 68 FEKT Vysokého učení technick

- Page 71 and 72: 70 FEKT Vysokého učení technick

- Page 73 and 74: 72 FEKT Vysokého učení technick

- Page 75 and 76: 74 FEKT Vysokého učení technick

- Page 77 and 78: 76 FEKT Vysokého učení technick

- Page 79 and 80: 78 FEKT Vysokého učení technick

30 FEKT Vysokého učení technického v BrněPlanarizace je technologický proces, který po každém technologickém kroku zarovnáváhorní vrstvu wafferu. Účelem planarizace je hladký povrch wafferu což umožňuje využítvelmi jemných litografických procesů v každé fázi výroby čipu. Planarizace umožňuje takévytvářet hustou síť víceúrovňového propojování metalovými vodiči.3.5.2 Technologie polySi hradlaJedním z prvních vylepšení technologie bylo zavedení polySi hradel. Hradla z polySiumožňují využít self-aligned polySi gate proces, jehož prostřednictvím jsou vytvářenypřesnější a kompaktnější struktury. PolySi hradlo je využito jako maska během procesuiontové implantace při vytváření oblastí source a drain. Vytvořené oblasti jsou soukryvné shradlem. Výsledná struktura má potom i menší plochu. Navíc je tímto způsobem eliminovánai velká část parazitní kapacity gate-drain.Dalším vylepšením této techniky je využití slabě dotované drain struktury (low-dopeddrain structure, LDD). Ukázka je na Obr. 4. První mělký implant je využit pro kontakt sinverzní vrstvou pod hradlem. Mělký implant má pouze velmi malý přesah okraje hradla adrain/source oblasti. Po přidání bočních hrazení kolem hradla je vyroben hluboký implantpřes oblast implantu mělkého. Tento hluboký implant má nízký sériový parazitní odpor.Kombinace těchto dvou typů implantu vede k minimalizaci parazitního odporu a parazitníkapacity která vzniká překryvem hradla a oblasti drain/source.Obr. 4 Technologie polySi hradlaNa Obr. 4 je také vidět lokální izolační vrstva LOCOS. Využití polySi na hradlo MOSstruktury má také nevýhody. Jednou z nich je vyšší rezistivita než v případě hradla z hliníku.V případě dlouhých spojů z polySi může nastat problém s velkou RC konstantou. Proceszvaný silicidace (úprava pokovením či implantace tenké kovové vrstvičky na hradlo; WSi,TaSi, CoSi apod.) může pomoci toto velké RC zpoždění redukovat. Také využívání polySipouze jako materiálu pro hradla a ne jako vodičů lokální úrovně může minimalizovat RCkonstantu.3.5.3 CMOS technologieKomplementární MOS obvody vyžadují NMOS a PMOS tranzistory na jednomsubstrátu. Tzn., že v případě p substrátu musíme využít n-well (jáma typu n) vrstvu. Jsou itechnologie využívající p-well, případně oba typy jámy (hlavně v technologiích, kdy substrátmá malou hustotu dotace). Vrstvy hradlového oxidu, polySi hradlo, kontakty drain a source,