Osnovi elektronike

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

gde je I<br />

DDmax<br />

maksimalna nekapacitivna struja tokom promene stanja.<br />

Pošto sva tri izraza za dinamičku disipaciju pokazuju linearnu zavisnost disipacije od<br />

učestanosti f, u praksi je uobičajeno da se dinamička disipacija prikazuje izrazom:<br />

P = f( C + C ) V<br />

(11.61)<br />

2<br />

D p pD DD<br />

gde je C<br />

pD<br />

ekvivalentna kapacitivnost, kojom se aproksimiraju teško merljivi uticaji dispacije<br />

usled parazitnih kapacitivnosti i promene stanja. Iz prethodnih izraza sledi:<br />

C = C + 0.5( V − 2 V ) I ( t + t ) V<br />

(11.62)<br />

2<br />

pD T DD T DD max LH HL DD<br />

Kapacitivnost C<br />

pD<br />

se obično određuje eksperimentalno, merenjem disipacije kola bez<br />

opterećenja. Interesantno je da se metod izražavanja dinamičke disipacije pomoću izraza za P<br />

D<br />

može generalizovati i primenjivati čak kod vrlo složenih CMOS kola. Tipične vrednosti<br />

kapacitivnosti C<br />

pD<br />

su reda 10 - 30 pF, što zavisi od složenosti i karakteristika CMOS kola.<br />

Tipična vrednost proizvoda snage i kašnjenja CMOS kola niskog stepena integracije je<br />

oko 10 pJ. Interesantno je primetiti da kod CMOS kola parametar PDP linearno zavisi od<br />

učestanosti promena logičkih stanja. Kod složenih logičkih mreža samo mali broj logičkih kola<br />

menja stanje u jednom takt ciklusu. Uzimajući ovu činjenicu u obzir, može se zaključiti da<br />

CMOS kola visokog stepena integracije imaju znatno manju prosečnu disipaciju po logičkom<br />

kolu. Kod CMOS kola u VLSI tehnici, parametar PDP može biti i manji od 1 pJ čak i pri<br />

učestanostima od nekoliko desetina MHz.<br />

11.5 Logička kola sa MOS tranzistorima<br />

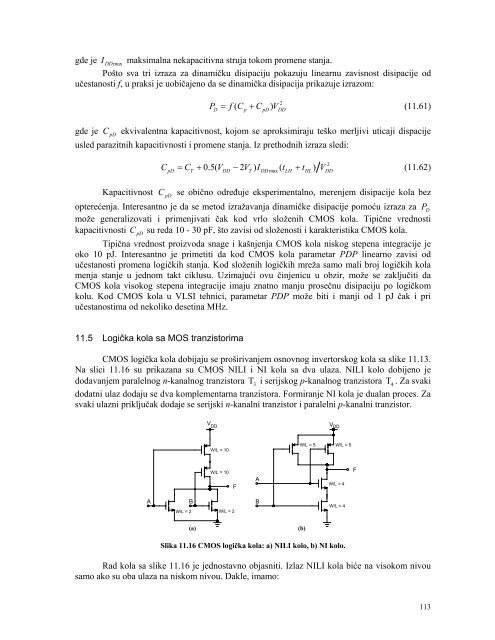

CMOS logička kola dobijaju se proširivanjem osnovnog invertorskog kola sa slike 11.13.<br />

Na slici 11.16 su prikazana su CMOS NILI i NI kola sa dva ulaza. NILI kolo dobijeno je<br />

dodavanjem paralelnog n-kanalnog tranzistora T<br />

3<br />

i serijskog p-kanalnog tranzistora T<br />

4<br />

. Za svaki<br />

dodatni ulaz dodaju se dva komplementarna tranzistora. Formiranje NI kola je dualan proces. Za<br />

svaki ulazni priključak dodaje se serijski n-kanalni tranzistor i paralelni p-kanalni tranzistor.<br />

VDD<br />

VDD<br />

W/L = 10<br />

W/L = 5<br />

W/L = 5<br />

W/L = 10<br />

F<br />

A<br />

W/L = 4<br />

F<br />

A<br />

B<br />

W/L = 2 W/L = 2<br />

B<br />

W/L = 4<br />

(a) (b)<br />

Slika 11.16 CMOS logička kola: a) NILI kolo, b) NI kolo.<br />

Rad kola sa slike 11.16 je jednostavno objasniti. Izlaz NILI kola biće na visokom nivou<br />

samo ako su oba ulaza na niskom nivou. Dakle, imamo:<br />

113