Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

34<br />

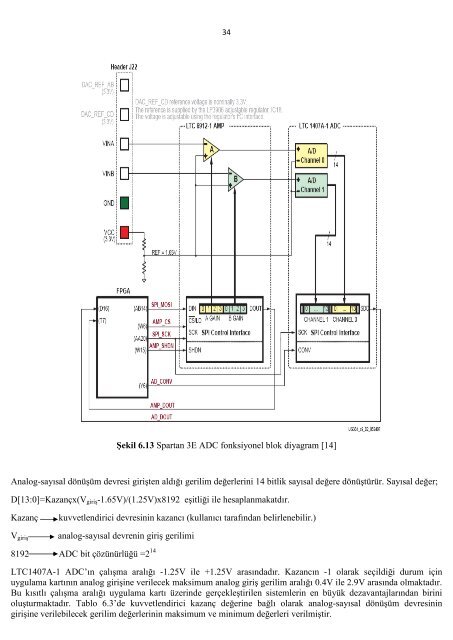

Şekil 6.13 Spartan 3E ADC fonksiyonel blok diyagram [14]<br />

Analog-sayısal dönüşüm devresi girişten aldığı gerilim değerlerini 14 bitlik sayısal değere dönüştürür. Sayısal değer;<br />

D[13:0]=Kazançx(V giriş -1.65V)/(1.25V)x8192 eşitliği ile hesaplanmakatdır.<br />

Kazanç<br />

V giriş<br />

kuvvetlendirici devresinin kazancı (kullanıcı tarafından belirlenebilir.)<br />

analog-sayısal devrenin giriş gerilimi<br />

8192 ADC bit çözünürlüğü =2 14<br />

LTC1407A-1 ADC’ın çalışma aralığı -1.25V ile +1.25V arasındadır. Kazancın -1 olarak seçildiği durum için<br />

uygulama kartının analog girişine verilecek maksimum analog giriş gerilim aralığı 0.4V ile 2.9V arasında olmaktadır.<br />

Bu kısıtlı çalışma aralığı uygulama kartı üzerinde gerçekleştirilen sistemlerin en büyük dezavantajlarından birini<br />

oluşturmaktadır. Tablo 6.3’de kuvvetlendirici kazanç değerine bağlı olarak analog-sayısal dönüşüm devresinin<br />

girişine verilebilecek gerilim değerlerinin maksimum ve minimum değerleri verilmiştir.