Kompendium - Datorteknik

Kompendium - Datorteknik Kompendium - Datorteknik

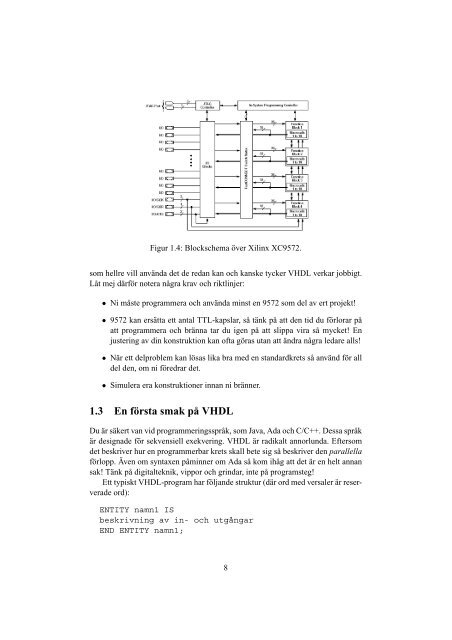

Figur 1.3: Makrocellen i 22V10.D-vippa. Värdet 0 anger att D-vippa skall användas. Värdet 1 anger att signalenskall passera förbi vippan, dvs att cellen används för kombinatoriskt nätC 1 anger om signal eller inverterad signal skall användas. Man har många möjligheteratt invertera signaler, både i makrocellerna och på ingångarna till grindnäten.Detta gör att de flesta någorlunda enkla kombinatoriska uttryck som manbehöver kan implementeras i grindnätet vid varje makrocell. Med bara 10 vipporär 22V10 ganska begränsad. Bokstaven V i 22V10 står för att grindnäten är avvariabel storlek, dvs att de tio näten är olika stora. Detta framgår av figuren. Grindnätenkallas för produkttermer, eftersom de är ett tvålagers nät av AND-grindarföljt av en OR-grind. Ingångarna till dessa kallas produkter resp. termer, analogtmed multiplikation och addition. I industrin bygger man ofta sina konstruktionermed bara en enda programmerbar krets. Man tar helt enkelt till en som är så stor attden räcker. 22V10 rymmer uppenbart inte ett DK-projekt, och det är inte meningenheller. Räkna med att använda flera, och ett antal specialiserade kretsar dessutom,i synnerhet minnen. En lämplig användning för en 22V10 är att implementera ettkombinatoriskt nät eller ett sekvensnät. Du ersätter ett antal grindar och vippor meden krets.1.2.3 CPLD Xilinx 9572Vi går vidare ytterligare ett steg och tittar på en CPLD (Complex PLD). Det visarsig att det effektivaste sättet att bygga större PLD-er är att kombinera flerastycken mindre PLD-er mha av ett förbindningsnät. Anledningen till detta är attAND-planet annars tenderar att bli underutnyttjat. Figur 1.4 visar en XC9572, 72makroceller, uppbyggd som 4 st 36V18 med ett förbindningsnät, som gör att endel signaler i en 36V18 kan göras tillgängliga globalt. Denna krets kommer att användasi kursen från och med VT2004. I samma kretsfamilj finns också 9536 och95108 att tillgå hos oss.1.2.4 Minimikrav och goda rådNu hoppas vi förstås att du är nyfiken och sugen på att använda programmerbarakretsar för att göra eleganta konstruktionslösningar, men vi inser att det finns de7

Figur 1.4: Blockschema över Xilinx XC9572.som hellre vill använda det de redan kan och kanske tycker VHDL verkar jobbigt.Låt mej därför notera några krav och riktlinjer:• Ni måste programmera och använda minst en 9572 som del av ert projekt!• 9572 kan ersätta ett antal TTL-kapslar, så tänk på att den tid du förlorar påatt programmera och bränna tar du igen på att slippa vira så mycket! Enjustering av din konstruktion kan ofta göras utan att ändra några ledare alls!• När ett delproblem kan lösas lika bra med en standardkrets så använd för alldel den, om ni föredrar det.• Simulera era konstruktioner innan ni bränner.1.3 En första smak på VHDLDu är säkert van vid programmeringsspråk, som Java, Ada och C/C++. Dessa språkär designade för sekvensiell exekvering. VHDL är radikalt annorlunda. Eftersomdet beskriver hur en programmerbar krets skall bete sig så beskriver den parallellaförlopp. Även om syntaxen påminner om Ada så kom ihåg att det är en helt annansak! Tänk på digitalteknik, vippor och grindar, inte på programsteg!Ett typiskt VHDL-program har följande struktur (där ord med versaler är reserveradeord):ENTITY namn1 ISbeskrivning av in- och utgångarEND ENTITY namn1;8

- Page 1 and 2: Digital Konstruktion TSEA43Ingemar

- Page 3 and 4: 2.2.1 COMPONENT-satsen . . . . . .

- Page 5 and 6: Kapitel 1Introduktion till VHDL1.1

- Page 7: När man ansluter lodräta ledare m

- Page 11 and 12: x

- Page 13 and 14: Exempel: Vi vill bygga ett sekvensn

- Page 15 and 16: u

- Page 17 and 18: 1.6.2 Signaler och variablerVHDL sk

- Page 19 and 20: Sedan kan man deklarera signaler so

- Page 21 and 22: WITH sel SELECTy

- Page 23 and 24: ELSE -- x är 1!CASE q ISWHEN "00"

- Page 25 and 26: • klockan får inte förekomma n

- Page 27 and 28: Kapitel 2Utvecklingsverktyget ISEVi

- Page 29 and 30: Tryck därefter next och sedan på

- Page 31 and 32: TIE | 739 | TIETIE | 838 | countTIE

- Page 33 and 34: END testbench;ARCHITECTURE behavior

- Page 35 and 36: uut: counter PORT MAP(clk => clk,co

- Page 37 and 38: esetHexa−decimalttangentbord4PNR4

- Page 39 and 40: clkrstKBstrobekbSEPREG1X2dvar210-r

- Page 41 and 42: p

- Page 43 and 44: 3.5 SimuleringVi avslutar detta exe

- Page 45 and 46: Kapitel 4Laborationsuppgift:IR-mott

- Page 47 and 48: IR−mottagareCPLDKlock−modulFigu

- Page 49: Bilaga AKopplingsschemanA.1 Blocksc

- Page 52 and 53: knapp

- Page 54 and 55: u : OUT std_logic_vector(3 downto 0

- Page 56 and 57: Bilaga CProjektkatalog för DK/IT 2

Figur 1.4: Blockschema över Xilinx XC9572.som hellre vill använda det de redan kan och kanske tycker VHDL verkar jobbigt.Låt mej därför notera några krav och riktlinjer:• Ni måste programmera och använda minst en 9572 som del av ert projekt!• 9572 kan ersätta ett antal TTL-kapslar, så tänk på att den tid du förlorar påatt programmera och bränna tar du igen på att slippa vira så mycket! Enjustering av din konstruktion kan ofta göras utan att ändra några ledare alls!• När ett delproblem kan lösas lika bra med en standardkrets så använd för alldel den, om ni föredrar det.• Simulera era konstruktioner innan ni bränner.1.3 En första smak på VHDLDu är säkert van vid programmeringsspråk, som Java, Ada och C/C++. Dessa språkär designade för sekvensiell exekvering. VHDL är radikalt annorlunda. Eftersomdet beskriver hur en programmerbar krets skall bete sig så beskriver den parallellaförlopp. Även om syntaxen påminner om Ada så kom ihåg att det är en helt annansak! Tänk på digitalteknik, vippor och grindar, inte på programsteg!Ett typiskt VHDL-program har följande struktur (där ord med versaler är reserveradeord):ENTITY namn1 ISbeskrivning av in- och utgångarEND ENTITY namn1;8