Ãvningsuppgifter i dig.sys v.49-50 1. Rita tillstÃ¥ndsgraf för en ...

Ãvningsuppgifter i dig.sys v.49-50 1. Rita tillstÃ¥ndsgraf för en ...

Ãvningsuppgifter i dig.sys v.49-50 1. Rita tillstÃ¥ndsgraf för en ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

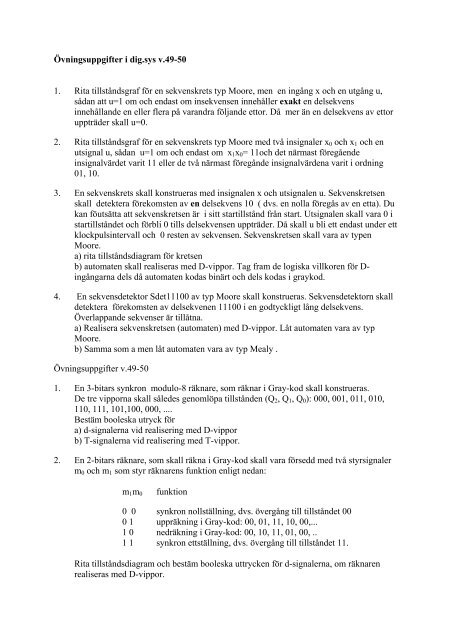

Övningsuppgifter i <strong>dig</strong>.<strong>sys</strong> <strong>v.49</strong>-<strong>50</strong><strong>1.</strong> <strong>Rita</strong> tillståndsgraf för <strong>en</strong> sekv<strong>en</strong>skrets typ Moore, m<strong>en</strong> <strong>en</strong> ingång x och <strong>en</strong> utgång u,sådan att u=1 om och <strong>en</strong>dast om insekv<strong>en</strong>s<strong>en</strong> innehåller exakt <strong>en</strong> delsekv<strong>en</strong>sinnehållande <strong>en</strong> eller flera på varandra följande ettor. Då mer än <strong>en</strong> delsekv<strong>en</strong>s av ettoruppträder skall u=0.2. <strong>Rita</strong> tillståndsgraf för <strong>en</strong> sekv<strong>en</strong>skrets typ Moore med två insignaler x 0 och x 1 och <strong>en</strong>utsignal u, sådan u=1 om och <strong>en</strong>dast om x 1 x 0 = 11och det närmast föregå<strong>en</strong>deinsignalvärdet varit 11 eller de två närmast föregånde insignalvärd<strong>en</strong>a varit i ordning01, 10.3. En sekv<strong>en</strong>skrets skall konstrueras med insignal<strong>en</strong> x och utsignal<strong>en</strong> u. Sekv<strong>en</strong>skrets<strong>en</strong>skall detektera förekomst<strong>en</strong> av <strong>en</strong> delsekv<strong>en</strong>s 10 ( dvs. <strong>en</strong> nolla föregås av <strong>en</strong> etta). Dukan föutsätta att sekv<strong>en</strong>skrets<strong>en</strong> är i sitt startillstånd från start. Utsignal<strong>en</strong> skall vara 0 istartillståndet och förbli 0 tills delsekv<strong>en</strong>s<strong>en</strong> uppträder. Då skall u bli ett <strong>en</strong>dast under ettklockpulsintervall och 0 rest<strong>en</strong> av sekv<strong>en</strong>s<strong>en</strong>. Sekv<strong>en</strong>skrets<strong>en</strong> skall vara av typ<strong>en</strong>Moore.a) rita tillståndsdiagram för krets<strong>en</strong>b) automat<strong>en</strong> skall realiseras med D-vippor. Tag fram de logiska villkor<strong>en</strong> för D-ingångarna dels då automat<strong>en</strong> kodas binärt och dels kodas i graykod.4. En sekv<strong>en</strong>sdetektor Sdet11100 av typ Moore skall konstrueras. Sekv<strong>en</strong>sdetektorn skalldetektera förekomst<strong>en</strong> av delsekv<strong>en</strong><strong>en</strong> 11100 i <strong>en</strong> godtyckligt lång delsekv<strong>en</strong>s.Överlappande sekv<strong>en</strong>ser är tillåtna.a) Realisera sekv<strong>en</strong>skrets<strong>en</strong> (automat<strong>en</strong>) med D-vippor. Låt automat<strong>en</strong> vara av typMoore.b) Samma som a m<strong>en</strong> låt automat<strong>en</strong> vara av typ Mealy .Övningsuppgifter <strong>v.49</strong>-<strong>50</strong><strong>1.</strong> En 3-bitars synkron modulo-8 räknare, som räknar i Gray-kod skall konstrueras.De tre vipporna skall således g<strong>en</strong>omlöpa tillstånd<strong>en</strong> (Q 2 , Q 1 , Q 0 ): 000, 001, 011, 010,110, 111, 101,100, 000, ....Bestäm booleska utryck föra) d-signalerna vid realisering med D-vipporb) T-signalerna vid realisering med T-vippor.2. En 2-bitars räknare, som skall räkna i Gray-kod skall vara försedd med två styrsignalerm 0 och m 1 som styr räknar<strong>en</strong>s funktion <strong>en</strong>ligt nedan:m 1 m 0funktion0 0 synkron nollställning, dvs. övergång till tillståndet 000 1 uppräkning i Gray-kod: 00, 01, 11, 10, 00,...1 0 nedräkning i Gray-kod: 00, 10, 11, 01, 00, ..1 1 synkron ettställning, dvs. övergång till tillståndet 1<strong>1.</strong><strong>Rita</strong> tillståndsdiagram och bestäm booleska uttryck<strong>en</strong> för d-signalerna, om räknar<strong>en</strong>realiseras med D-vippor.

3. a) Beskriv räknar<strong>en</strong> i uppgift 1 i VHDL.b) komplettera räknar<strong>en</strong> med <strong>en</strong> Enable funktion (aktivt hög, dvs. då Enable = 1, såräknar d<strong>en</strong> <strong>en</strong>ligt specifikation<strong>en</strong> och då Enable = 0 , så vilar d<strong>en</strong>.)c) Komplettera dessutom med <strong>en</strong> Reset, aktivt hög och givetvis synkron. Dessutomskall Enable-funktion<strong>en</strong> dominera över Reset-funktion<strong>en</strong>. Detta innebär att då båda ärett, så 'vinner' Enable-funktion<strong>en</strong> och räknar<strong>en</strong> nollställes ej.4. En 4-bitars räknare skall beskrivas i VHDL. D<strong>en</strong> skall ha två räknemoder, som skallstyras av <strong>en</strong> kontrollsignal b_d. Då b_d= fungerar räknar<strong>en</strong>, som <strong>en</strong> modulo 16 räknare (dvs. räknar 0, 1, 2.....15, 0..) och då b_d= 0 skall räknar<strong>en</strong> fungera, som <strong>en</strong>dekadräknare. Om b_d går från 1 till 0 då räknar<strong>en</strong> befinner sig i tillstånd<strong>en</strong> 10 till 15skall räkner<strong>en</strong> först räkna till och med 15 innan d<strong>en</strong> går över till att fungera, somdekadräknare.