Verilog

Verilog

Verilog

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

第三章<br />

第三章<br />

第三章<br />

第三章 基础知识<br />

基础知识<br />

基础知识<br />

基础知识<br />

本章学习目标<br />

本章学习目标<br />

本章学习目标<br />

本章学习目标<br />

理解操作符<br />

理解操作符<br />

理解操作符<br />

理解操作符、注释<br />

注释<br />

注释<br />

注释、空白符<br />

空白符<br />

空白符<br />

空白符、数字<br />

数字<br />

数字<br />

数字、字符串和标识符<br />

字符串和标识符<br />

字符串和标识符<br />

字符串和标识符<br />

的词法约定<br />

的词法约定<br />

的词法约定<br />

的词法约定。<br />

陈国平<br />

上海理工<br />

定义逻辑值集合和数据类型<br />

定义逻辑值集合和数据类型<br />

定义逻辑值集合和数据类型<br />

定义逻辑值集合和数据类型,包括线网<br />

包括线网<br />

包括线网<br />

包括线网、寄存器<br />

寄存器<br />

寄存器<br />

寄存器、向<br />

量、数字<br />

数字<br />

数字<br />

数字、仿真时间<br />

仿真时间<br />

仿真时间<br />

仿真时间、数组<br />

数组<br />

数组<br />

数组、参数<br />

参数<br />

参数<br />

参数、存储器和字符串<br />

存储器和字符串<br />

存储器和字符串<br />

存储器和字符串。<br />

学习使用用于显示和监视信息<br />

学习使用用于显示和监视信息<br />

学习使用用于显示和监视信息<br />

学习使用用于显示和监视信息、暂停和结束仿真的系<br />

暂停和结束仿真的系<br />

暂停和结束仿真的系<br />

暂停和结束仿真的系<br />

统任务<br />

统任务<br />

统任务<br />

统任务。<br />

学习用于宏定义<br />

学习用于宏定义<br />

学习用于宏定义<br />

学习用于宏定义、文件包含的基本编译指令<br />

文件包含的基本编译指令<br />

文件包含的基本编译指令<br />

文件包含的基本编译指令。

3.1 词法约定<br />

词法约定<br />

<strong>Verilog</strong>中的基本词法约定与<br />

中的基本词法约定与<br />

中的基本词法约定与C语言类似<br />

中的基本词法约定与 语言类似 语言类似。<br />

语言类似<br />

<strong>Verilog</strong>是大小写相关的<br />

是大小写相关的<br />

是大小写相关的,其中的关键字全部为小写<br />

是大小写相关的 其中的关键字全部为小写<br />

其中的关键字全部为小写。<br />

其中的关键字全部为小写<br />

注释<br />

注释<br />

上海理工<br />

单行注释以<br />

单行注释以“// 单行注释以 ”开始 开始 开始,<strong>Verilog</strong>将忽略从此处到行尾的内容<br />

开始 将忽略从此处到行尾的内容<br />

将忽略从此处到行尾的内容。<br />

将忽略从此处到行尾的内容<br />

多行注释以<br />

多行注释以“/*”开始<br />

多行注释以 开始 开始,结束于<br />

开始 结束于 结束于“*/”。<br />

结束于<br />

多行注释不允许嵌套<br />

多行注释不允许嵌套,但是单行注释可以嵌套在多行注释中<br />

多行注释不允许嵌套 但是单行注释可以嵌套在多行注释中<br />

但是单行注释可以嵌套在多行注释中。<br />

但是单行注释可以嵌套在多行注释中<br />

操作符<br />

操作符<br />

操作符有三种类型<br />

操作符有三种类型:单目操作符<br />

操作符有三种类型 单目操作符<br />

单目操作符、双目操作符和三目操作符<br />

单目操作符 双目操作符和三目操作符<br />

双目操作符和三目操作符,<br />

双目操作符和三目操作符<br />

单目操作符的优先级高于操作数<br />

单目操作符的优先级高于操作数。三目操作符包括两个单独的<br />

单目操作符的优先级高于操作数 三目操作符包括两个单独的<br />

操作符 操作符,用来分隔三个操作数<br />

操作符 用来分隔三个操作数<br />

用来分隔三个操作数。<br />

用来分隔三个操作数<br />

a = ~ b;<br />

a = b && c;<br />

a = b ? c : d;<br />

陈国平

上海理工<br />

表1 <strong>Verilog</strong>中的操作符 中的操作符<br />

优先级 优先级<br />

名称 名称<br />

优先级 优先级 名称<br />

名称<br />

+ 一元加 一元加<br />

>> 右移 右移<br />

右移<br />

- 一元减 < 小于<br />

小于<br />

! 一元逻辑非 一元逻辑非<br />

大于<br />

大于<br />

& 归约与 归约与<br />

>= 大于等于<br />

大于等于<br />

~& 归约与非 归约与非<br />

== 逻辑相等<br />

逻辑相等<br />

^ 归约异或 归约异或<br />

!= 逻辑不等<br />

逻辑不等<br />

^~或~^ 归约异或非 归约异或非<br />

=== 全等<br />

全等<br />

| 归约或 归约或<br />

!== 非全等<br />

非全等<br />

~| 归约或非 归约或非<br />

& 按位与<br />

按位与<br />

* 乘 ^ 按位异或<br />

按位异或<br />

/ 除 ^~或~^ 按位异或非<br />

按位异或非<br />

% 取模 取模<br />

| 按位或<br />

按位或<br />

+ 二元加 二元加<br />

&& 逻辑与 逻辑与<br />

逻辑与<br />

- 二元减 || 逻辑或<br />

逻辑或<br />

数字声明<br />

数字声明<br />

数字声明<br />

数字声明<br />

两种数字声明<br />

两种数字声明<br />

两种数字声明<br />

两种数字声明:指明位数的数字和不指明位数的数字<br />

指明位数的数字和不指明位数的数字<br />

指明位数的数字和不指明位数的数字<br />

指明位数的数字和不指明位数的数字<br />

指明位数的数字<br />

指明位数的数字<br />

指明位数的数字<br />

指明位数的数字:<br />

'<br />

用于指明数字的位宽度<br />

用于指明数字的位宽度<br />

用于指明数字的位宽度<br />

用于指明数字的位宽度,只能用十进制数表<br />

只能用十进制数表<br />

只能用十进制数表<br />

只能用十进制数表<br />

示。合法的基数格式包括十进制<br />

合法的基数格式包括十进制<br />

合法的基数格式包括十进制<br />

合法的基数格式包括十进制(‘d或’D)、<br />

)、<br />

)、<br />

)、十六进<br />

十六进<br />

十六进<br />

十六进<br />

陈国平<br />

上海理工<br />

示。合法的基数格式包括十进制<br />

合法的基数格式包括十进制<br />

合法的基数格式包括十进制<br />

合法的基数格式包括十进制(‘d或’D)、<br />

)、<br />

)、<br />

)、十六进<br />

十六进<br />

十六进<br />

十六进<br />

制(‘h或’H)、<br />

)、<br />

)、<br />

)、二进制<br />

二进制<br />

二进制<br />

二进制(‘b或’B)和八进制<br />

和八进制<br />

和八进制<br />

和八进制(‘o<br />

或’O)。<br />

)。<br />

)。<br />

)。<br />

例如<br />

例如<br />

例如<br />

例如:4'b1111,16'h3a6f等<br />

如果没有指定位宽度<br />

如果没有指定位宽度<br />

如果没有指定位宽度<br />

如果没有指定位宽度,则默认的位宽度与仿真器和使<br />

则默认的位宽度与仿真器和使<br />

则默认的位宽度与仿真器和使<br />

则默认的位宽度与仿真器和使<br />

用的计算机有关<br />

用的计算机有关<br />

用的计算机有关<br />

用的计算机有关(最小为<br />

最小为<br />

最小为<br />

最小为32位)<br />

'o21 //32位八进制数<br />

位八进制数<br />

位八进制数<br />

位八进制数

X和Z值<br />

x表示不确定值<br />

表示不确定值<br />

表示不确定值<br />

表示不确定值, z表示高阻值<br />

表示高阻值<br />

表示高阻值<br />

表示高阻值。<br />

在以十六进制为基数的表示中<br />

在以十六进制为基数的表示中<br />

在以十六进制为基数的表示中<br />

在以十六进制为基数的表示中x或z代表<br />

代表<br />

代表<br />

代表4位,在八进制<br />

在八进制<br />

在八进制<br />

在八进制<br />

的情况下<br />

的情况下<br />

的情况下<br />

的情况下x或z代表<br />

代表<br />

代表<br />

代表3位,在二进制的情况下<br />

在二进制的情况下<br />

在二进制的情况下<br />

在二进制的情况下x或z代表<br />

代表<br />

代表<br />

代表1<br />

位。<br />

12'h13x //12位十六进制数<br />

位十六进制数<br />

位十六进制数<br />

位十六进制数,低四位不确定<br />

低四位不确定<br />

低四位不确定<br />

低四位不确定<br />

下划线符号和问号<br />

下划线符号和问号<br />

下划线符号和问号<br />

下划线符号和问号<br />

陈国平<br />

上海理工<br />

下划线符号和问号<br />

下划线符号和问号<br />

下划线符号和问号<br />

下划线符号和问号<br />

除了第一个字符<br />

除了第一个字符<br />

除了第一个字符<br />

除了第一个字符,下划线<br />

下划线<br />

下划线<br />

下划线“_”可以出现在数字中的任<br />

可以出现在数字中的任<br />

可以出现在数字中的任<br />

可以出现在数字中的任<br />

何位置<br />

何位置<br />

何位置<br />

何位置,它的作用只是提高可读性<br />

它的作用只是提高可读性<br />

它的作用只是提高可读性<br />

它的作用只是提高可读性,在编译阶段将被忽<br />

在编译阶段将被忽<br />

在编译阶段将被忽<br />

在编译阶段将被忽<br />

略掉<br />

略掉<br />

略掉<br />

略掉。如8'b1101_1010<br />

问号<br />

问号<br />

问号<br />

问号“?”是z的另一种表示<br />

的另一种表示<br />

的另一种表示<br />

的另一种表示。在casex和casez语句<br />

语句<br />

语句<br />

语句<br />

中,?”(即高阻抗<br />

即高阻抗<br />

即高阻抗<br />

即高阻抗)表示<br />

表示<br />

表示<br />

表示“不必关心<br />

不必关心<br />

不必关心<br />

不必关心”的情况<br />

的情况<br />

的情况<br />

的情况。如:<br />

4'b10?? //相当于<br />

相当于<br />

相当于<br />

相当于4'b10zz

3.2 数据类型<br />

数据类型<br />

3.2.1 值的种类<br />

值的种类<br />

<strong>Verilog</strong>使用四值逻辑和八种信号强度来对实际的硬<br />

使用四值逻辑和八种信号强度来对实际的硬<br />

件电路建模<br />

件电路建模。<br />

件电路建模<br />

上海理工<br />

陈国平

3.2.1 值的种类 值的种类(续)<br />

值的种类<br />

逻辑值 逻辑值 逻辑值0和1可以拥有下表中列出的<br />

逻辑值 可以拥有下表中列出的<br />

可以拥有下表中列出的8种强度值<br />

可以拥有下表中列出的 种强度值<br />

上海理工<br />

陈国平

3.2.1 值的种类<br />

值的种类<br />

值的种类<br />

值的种类(续)<br />

如果两个具有不同强度的信号驱动同一个线网<br />

如果两个具有不同强度的信号驱动同一个线网<br />

如果两个具有不同强度的信号驱动同一个线网<br />

如果两个具有不同强度的信号驱动同一个线网,则竞<br />

则竞<br />

则竞<br />

则竞<br />

争结果值为高强度信号的值<br />

争结果值为高强度信号的值<br />

争结果值为高强度信号的值<br />

争结果值为高强度信号的值。例如<br />

例如<br />

例如<br />

例如,如果在两个强度<br />

如果在两个强度<br />

如果在两个强度<br />

如果在两个强度<br />

分别为<br />

分别为<br />

分别为<br />

分别为strong1和weak0的信号之间发生竞争<br />

的信号之间发生竞争<br />

的信号之间发生竞争<br />

的信号之间发生竞争,则结<br />

则结<br />

则结<br />

则结<br />

果值服从<br />

果值服从<br />

果值服从<br />

果值服从strong1<br />

如果两个强度相同的信号之间发生竞争<br />

如果两个强度相同的信号之间发生竞争<br />

如果两个强度相同的信号之间发生竞争<br />

如果两个强度相同的信号之间发生竞争,则结果为不<br />

则结果为不<br />

则结果为不<br />

则结果为不<br />

确定值<br />

确定值<br />

确定值<br />

确定值。例如两个强度为<br />

例如两个强度为<br />

例如两个强度为<br />

例如两个强度为strong1和strong0的信号之<br />

的信号之<br />

的信号之<br />

的信号之<br />

陈国平<br />

上海理工<br />

确定值<br />

确定值<br />

确定值<br />

确定值。例如两个强度为<br />

例如两个强度为<br />

例如两个强度为<br />

例如两个强度为strong1和strong0的信号之<br />

的信号之<br />

的信号之<br />

的信号之<br />

间发生竞争<br />

间发生竞争<br />

间发生竞争<br />

间发生竞争,则结果为<br />

则结果为<br />

则结果为<br />

则结果为x。<br />

对于信号竞争<br />

对于信号竞争<br />

对于信号竞争<br />

对于信号竞争、MOS器件<br />

器件<br />

器件<br />

器件、动态<br />

动态<br />

动态<br />

动态MOS和其他底层器<br />

和其他底层器<br />

和其他底层器<br />

和其他底层器<br />

件的精确建模<br />

件的精确建模<br />

件的精确建模<br />

件的精确建模,强度等级具有很大的作用<br />

强度等级具有很大的作用<br />

强度等级具有很大的作用<br />

强度等级具有很大的作用。在各种类<br />

在各种类<br />

在各种类<br />

在各种类<br />

型的线网中<br />

型的线网中<br />

型的线网中<br />

型的线网中,只有<br />

只有<br />

只有<br />

只有trireg类型的线网可以具有存储强<br />

类型的线网可以具有存储强<br />

类型的线网可以具有存储强<br />

类型的线网可以具有存储强<br />

度,强度分为<br />

强度分为<br />

强度分为<br />

强度分为large,medium和small三个等级<br />

三个等级<br />

三个等级<br />

三个等级。

3.2.2 线网<br />

线网<br />

线网<br />

线网<br />

线网<br />

线网<br />

线网<br />

线网(net)表示硬件单元之间的连接<br />

表示硬件单元之间的连接<br />

表示硬件单元之间的连接<br />

表示硬件单元之间的连接。线网由其连接<br />

线网由其连接<br />

线网由其连接<br />

线网由其连接<br />

器件的输出端连续驱动<br />

器件的输出端连续驱动<br />

器件的输出端连续驱动<br />

器件的输出端连续驱动。如下图所示<br />

如下图所示<br />

如下图所示<br />

如下图所示,线网<br />

线网<br />

线网<br />

线网a连接到<br />

连接到<br />

连接到<br />

连接到<br />

与门<br />

与门<br />

与门<br />

与门g1的输出端<br />

的输出端<br />

的输出端<br />

的输出端,它将连续地拥有与门<br />

它将连续地拥有与门<br />

它将连续地拥有与门<br />

它将连续地拥有与门g1的输出值<br />

的输出值<br />

的输出值<br />

的输出值:<br />

b & c<br />

陈国平<br />

上海理工<br />

wire a;<br />

默认线网的位宽为<br />

默认线网的位宽为<br />

默认线网的位宽为<br />

默认线网的位宽为1。线网的默认值为<br />

线网的默认值为<br />

线网的默认值为<br />

线网的默认值为z(trireg类型<br />

类型<br />

类型<br />

类型<br />

的线网例外<br />

的线网例外<br />

的线网例外<br />

的线网例外,其默认值为<br />

其默认值为<br />

其默认值为<br />

其默认值为x)。<br />

)。<br />

)。<br />

)。线网的值由其驱动源<br />

线网的值由其驱动源<br />

线网的值由其驱动源<br />

线网的值由其驱动源<br />

确定<br />

确定<br />

确定<br />

确定,如果没有驱动源<br />

如果没有驱动源<br />

如果没有驱动源<br />

如果没有驱动源,则线网的值为<br />

则线网的值为<br />

则线网的值为<br />

则线网的值为z。

3.2.3 寄存器<br />

寄存器<br />

寄存器数据类型一般通过使用关键字<br />

寄存器数据类型一般通过使用关键字<br />

寄存器数据类型一般通过使用关键字reg来声明<br />

寄存器数据类型一般通过使用关键字 来声明 来声明,默认<br />

来声明 默认<br />

值为 值为x。 值为 值为<br />

例3.1 寄存器的声明和使用<br />

寄存器的声明和使用<br />

例3.2 带符号寄存器的声明<br />

带符号寄存器的声明<br />

上海理工<br />

陈国平

3.2.4 向量<br />

向量<br />

线网和寄存器类型的数据均可以声明为向量<br />

线网和寄存器类型的数据均可以声明为向量(位宽大于<br />

线网和寄存器类型的数据均可以声明为向量 位宽大于 位宽大于1)。<br />

位宽大于 )。 )。如 )。<br />

果在声明中没有指定位宽<br />

果在声明中没有指定位宽,则默认为标量<br />

果在声明中没有指定位宽 则默认为标量<br />

则默认为标量(1位)。<br />

则默认为标量 )。<br />

向量通过 向量通过[high# 向量通过 : low#]或[low# : high#]进行说明 进行说明 进行说明,方括号中<br />

进行说明 方括号中<br />

左边的数总是代表向量的最高有效位<br />

左边的数总是代表向量的最高有效位。<br />

左边的数总是代表向量的最高有效位<br />

对向量 对向量,我们可以指定其中的一位或几位<br />

对向量 我们可以指定其中的一位或几位<br />

我们可以指定其中的一位或几位,如:<br />

我们可以指定其中的一位或几位<br />

上海理工<br />

陈国平

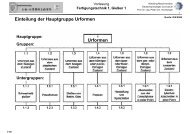

1. 1.电路模块 电路模块<br />

电路模块<br />

双向<br />

端口<br />

向量<br />

inout<br />

[n: m]<br />

双向<br />

端口<br />

网络连线 net<br />

网络连线 net<br />

连线<br />

向量<br />

inout<br />

[n: m]<br />

连<br />

线<br />

输入端口向量 input[n: m] 输入端口 input<br />

寄存器向量<br />

reg[n:m]<br />

连线向量 wire[n: m] 连线 wire<br />

组合逻辑<br />

寄存器 reg<br />

连线向量 wire[n: m] 连线 wire<br />

输出端口向量 output[n: m] 输出端口 output

3.2.5 整数 整数、实数和时间寄存器数据类型<br />

整数 实数和时间寄存器数据类型<br />

<strong>Verilog</strong>还支持 还支持 还支持integer,real和time寄存器数据类型<br />

还支持<br />

寄存器数据类型<br />

寄存器数据类型。<br />

寄存器数据类型<br />

声明为 声明为 声明为reg类型的寄存器变量为无符号数<br />

声明为 类型的寄存器变量为无符号数<br />

类型的寄存器变量为无符号数,而整数类<br />

类型的寄存器变量为无符号数 而整数类<br />

型的变量则为有符号数<br />

型的变量则为有符号数。<br />

型的变量则为有符号数<br />

上海理工<br />

陈国平

实常量和实数寄存器数据类型使用关键字<br />

实常量和实数寄存器数据类型使用关键字<br />

实常量和实数寄存器数据类型使用关键字real来声明<br />

实常量和实数寄存器数据类型使用关键字 来声明<br />

,可以用十进制或科学记数法<br />

可以用十进制或科学记数法<br />

可以用十进制或科学记数法(例如<br />

可以用十进制或科学记数法 例如 例如3e6代表<br />

例如 代表 代表3 代表 000<br />

000)来表示 来表示 来表示。实数声明不能带有范围<br />

来表示 实数声明不能带有范围<br />

实数声明不能带有范围,其默认值为<br />

实数声明不能带有范围 其默认值为<br />

其默认值为0<br />

其默认值为<br />

。如果将一个实数赋给一个整数<br />

如果将一个实数赋给一个整数<br />

如果将一个实数赋给一个整数,那么实数将会被取<br />

如果将一个实数赋给一个整数 那么实数将会被取<br />

那么实数将会被取<br />

整为最接近的整数<br />

整为最接近的整数。<br />

整为最接近的整数<br />

上海理工<br />

陈国平

仿真是按照仿真时间进行的<br />

仿真是按照仿真时间进行的<br />

仿真是按照仿真时间进行的,<strong>Verilog</strong>使用一个特殊<br />

仿真是按照仿真时间进行的 使用一个特殊<br />

的时间寄存器数据类型来保存仿真时间<br />

的时间寄存器数据类型来保存仿真时间。时间变量通<br />

的时间寄存器数据类型来保存仿真时间<br />

的时间寄存器数据类型来保存仿真时间 时间变量通<br />

过使用关键字<br />

过使用关键字time来声明<br />

过使用关键字<br />

过使用关键字 来声明 来声明,其宽度与具体实现有关<br />

来声明 其宽度与具体实现有关<br />

其宽度与具体实现有关,<br />

其宽度与具体实现有关<br />

最小为 最小为64位。通过调用系统函数<br />

最小为 通过调用系统函数<br />

通过调用系统函数$time可以得到当前<br />

通过调用系统函数 可以得到当前<br />

的仿真时间<br />

的仿真时间。<br />

的仿真时间<br />

上海理工<br />

陈国平

3.2.6 数组 数组<br />

数组<br />

在<strong>Verilog</strong>中允许声明<br />

中允许声明<br />

中允许声明reg,integer,time,real,<br />

中允许声明<br />

realtime及其向量类型的数组<br />

及其向量类型的数组<br />

及其向量类型的数组。<br />

及其向量类型的数组<br />

integer count [0:7]; //8个整 个整 个整形变量<br />

个整 变量<br />

reg bl [31:0]; //32个寄存器变量<br />

个寄存器变量<br />

time time chk [1:10]; //10个时间变量<br />

个时间变量<br />

个时间变量<br />

reg [4:0] port_id [0:7]; //8个端 个端 个端口变量<br />

个端 变量 变量,位宽为<br />

变量 位宽为 位宽为5<br />

位宽为<br />

上海理工<br />

陈国平

注意,不要将数组和线网或寄存器向量<br />

将数组和线网或寄存器向量<br />

将数组和线网或寄存器向量混淆起<br />

将数组和线网或寄存器向量 混淆起 混淆起来。向<br />

混淆起<br />

量是一个单<br />

量是一个单独的元件<br />

量是一个单 的元件 的元件,它的位宽为<br />

的元件 它的位宽为<br />

它的位宽为n;数组由<br />

它的位宽为 数组由 数组由多个元<br />

数组由 个元<br />

件组 件组成,其中的<br />

件组 件组 其中的 其中的每个元件的位宽为<br />

其中的 个元件的位宽为<br />

个元件的位宽为n或1。<br />

个元件的位宽为<br />

integer count [0:7]; //8个整 个整 个整形变量<br />

个整 变量<br />

reg [4:0] port_id [0:7]; //8个端 个端 个端口变量<br />

个端 变量 变量,位宽为<br />

变量 位宽为 位宽为5 位宽为<br />

count count [5] = 0;<br />

port_id [3] = 0; //将第 将第 将第3个寄存器单元<br />

将第 个寄存器单元<br />

个寄存器单元(5位)复位<br />

个寄存器单元<br />

port_id =0; //非法,企图写整个数组 整个数组<br />

上海理工<br />

陈国平

3.2.7 存储器<br />

存储器<br />

存储器<br />

存储器<br />

在<strong>Verilog</strong>中,使用寄存器的一<br />

使用寄存器的一<br />

使用寄存器的一<br />

使用寄存器的一维数组来表示存储器<br />

数组来表示存储器<br />

数组来表示存储器<br />

数组来表示存储器。<br />

数组的<br />

数组的<br />

数组的<br />

数组的每个元<br />

个元<br />

个元<br />

个元素称<br />

素称<br />

素称<br />

素称为一个元<br />

为一个元<br />

为一个元<br />

为一个元素或一个字<br />

或一个字<br />

或一个字<br />

或一个字(word),<br />

),<br />

),<br />

),由<br />

一个数组<br />

一个数组<br />

一个数组<br />

一个数组索引<br />

索引<br />

索引<br />

索引来指定<br />

来指定<br />

来指定<br />

来指定,每个字的位宽为<br />

个字的位宽为<br />

个字的位宽为<br />

个字的位宽为1位或<br />

位或<br />

位或<br />

位或多位。注<br />

意,n个1位寄存器和一个<br />

位寄存器和一个<br />

位寄存器和一个<br />

位寄存器和一个n位寄存器是不同的<br />

位寄存器是不同的<br />

位寄存器是不同的<br />

位寄存器是不同的。<br />

陈国平<br />

上海理工

3.2.8 参数<br />

参数<br />

参数<br />

参数<br />

<strong>Verilog</strong>允许使用关键字<br />

允许使用关键字<br />

允许使用关键字<br />

允许使用关键字parameter在模<br />

在模<br />

在模<br />

在模块内<br />

块内<br />

块内<br />

块内定义常数<br />

定义常数<br />

定义常数<br />

定义常数。<br />

参数代表常数<br />

参数代表常数<br />

参数代表常数<br />

参数代表常数,不能<br />

不能<br />

不能<br />

不能像变量那<br />

变量那<br />

变量那<br />

变量那样赋值<br />

赋值<br />

赋值<br />

赋值,但是每个模<br />

个模<br />

个模<br />

个模块<br />

实例的参数值可以在编译阶段被<br />

实例的参数值可以在编译阶段被<br />

实例的参数值可以在编译阶段被<br />

实例的参数值可以在编译阶段被重载<br />

重载<br />

重载<br />

重载。<br />

陈国平<br />

上海理工<br />

<strong>Verilog</strong>中的<br />

中的<br />

中的<br />

中的局部<br />

局部<br />

局部<br />

局部参数使用关键字<br />

参数使用关键字<br />

参数使用关键字<br />

参数使用关键字localparam来定义<br />

来定义<br />

来定义<br />

来定义,<br />

其作用等同于参数<br />

其作用等同于参数<br />

其作用等同于参数<br />

其作用等同于参数,区别在于它的值不能<br />

别在于它的值不能<br />

别在于它的值不能<br />

别在于它的值不能改变,不能<br />

不能<br />

不能<br />

不能<br />

通过参数<br />

通过参数<br />

通过参数<br />

通过参数重载<br />

重载<br />

重载<br />

重载语句<br />

语句<br />

语句<br />

语句(defparam)或通过有<br />

或通过有<br />

或通过有<br />

或通过有序参数列<br />

参数列<br />

参数列<br />

参数列<br />

表或<br />

表或<br />

表或<br />

表或命名<br />

命名<br />

命名<br />

命名参数赋值来<br />

参数赋值来<br />

参数赋值来<br />

参数赋值来直接修改<br />

修改<br />

修改<br />

修改。

3.2.9 字符串<br />

字符串<br />

字符串<br />

字符串<br />

字符串保存在<br />

字符串保存在<br />

字符串保存在<br />

字符串保存在reg类型的变量中<br />

类型的变量中<br />

类型的变量中<br />

类型的变量中,每个字符<br />

个字符<br />

个字符<br />

个字符占用8位<br />

(一个字<br />

一个字<br />

一个字<br />

一个字节),<br />

),<br />

),<br />

),因此<br />

因此<br />

因此<br />

因此寄存器变量的宽度<br />

寄存器变量的宽度<br />

寄存器变量的宽度<br />

寄存器变量的宽度应足够<br />

应足够<br />

应足够<br />

应足够大,以<br />

保证容纳全部<br />

证容纳全部<br />

证容纳全部<br />

证容纳全部字符<br />

字符<br />

字符<br />

字符。如果寄存器变量的宽度大于字符<br />

如果寄存器变量的宽度大于字符<br />

如果寄存器变量的宽度大于字符<br />

如果寄存器变量的宽度大于字符<br />

串的大小<br />

串的大小<br />

串的大小<br />

串的大小(位),<br />

),<br />

),<br />

),则<strong>Verilog</strong>使用<br />

使用<br />

使用<br />

使用0来填充左边<br />

填充左边<br />

填充左边<br />

填充左边的空<br />

的空<br />

的空<br />

的空余<br />

位;如果寄存器变量的宽度小于字符串的大小<br />

如果寄存器变量的宽度小于字符串的大小<br />

如果寄存器变量的宽度小于字符串的大小<br />

如果寄存器变量的宽度小于字符串的大小(位),<br />

),<br />

),<br />

),<br />

则<strong>Verilog</strong>截去<br />

截去<br />

截去<br />

截去字符串最<br />

字符串最<br />

字符串最<br />

字符串最左边<br />

左边<br />

左边<br />

左边的位<br />

的位<br />

的位<br />

的位。<br />

陈国平<br />

上海理工<br />

则<strong>Verilog</strong>截去<br />

截去<br />

截去<br />

截去字符串最<br />

字符串最<br />

字符串最<br />

字符串最左边<br />

左边<br />

左边<br />

左边的位<br />

的位<br />

的位<br />

的位。

3.2.9 字符串<br />

字符串<br />

字符串<br />

字符串(续)<br />

有一<br />

有一<br />

有一<br />

有一些特殊字符在显示字符串时具有特定的<br />

特殊字符在显示字符串时具有特定的<br />

特殊字符在显示字符串时具有特定的<br />

特殊字符在显示字符串时具有特定的意义,例<br />

如换行符<br />

行符<br />

行符<br />

行符、制表符和显示参数的值<br />

制表符和显示参数的值<br />

制表符和显示参数的值<br />

制表符和显示参数的值。如果<br />

如果<br />

如果<br />

如果需要<br />

需要<br />

需要<br />

需要在字符<br />

在字符<br />

在字符<br />

在字符<br />

串中显示<br />

串中显示<br />

串中显示<br />

串中显示这些<br />

这些<br />

这些<br />

这些特殊的字符<br />

特殊的字符<br />

特殊的字符<br />

特殊的字符,则必<br />

则必<br />

则必<br />

则必须加<br />

须加<br />

须加<br />

须加前缀转<br />

缀转<br />

缀转<br />

缀转义字符<br />

义字符<br />

义字符<br />

义字符。<br />

陈国平<br />

上海理工

3.3 系统任务和编译指令<br />

系统任务和编译指令<br />

系统任务和编译指令<br />

系统任务<br />

系统任务<br />

<strong>Verilog</strong>为某些常用操作提供了标准的系统任务<br />

为某些常用操作提供了标准的系统任务<br />

为某些常用操作提供了标准的系统任务(也称系统函<br />

为某些常用操作提供了标准的系统任务 也称系统函<br />

数), ), ),这些操作包括屏幕显示<br />

), 这些操作包括屏幕显示<br />

这些操作包括屏幕显示、线网值动态监视<br />

这些操作包括屏幕显示 线网值动态监视<br />

线网值动态监视、暂停和结束<br />

线网值动态监视 暂停和结束<br />

仿真等 仿真等。所有的系统任务都具有<br />

仿真等 仿真等 所有的系统任务都具有<br />

所有的系统任务都具有$的形式<br />

所有的系统任务都具有<br />

的形式 的形式。常用系<br />

的形式 常用系<br />

统任务如下<br />

统任务如下<br />

显示信息 显示信息 $display,格式 格式 格式:$display 格式 格式:$display 格式<br />

(p1, p2, p3,…,pn);<br />

监控信息 监控信息 $monitor,格式 格式 格式:$monitor 格式<br />

(p1, p2, p3,…,pn);<br />

暂停仿真 暂停仿真 $stop,格式 格式 格式:$stop;<br />

格式<br />

结束仿真 结束仿真$finish,格式<br />

结束仿真 格式 格式: 格式 $finish;<br />

上海理工<br />

陈国平

3.3 系统任务和编译指令<br />

系统任务和编译指令<br />

系统任务和编译指令<br />

系统任务和编译指令<br />

编译指令<br />

编译指令<br />

编译指令<br />

编译指令<br />

<strong>Verilog</strong>提供了一些编译指令供用户使用<br />

提供了一些编译指令供用户使用<br />

提供了一些编译指令供用户使用<br />

提供了一些编译指令供用户使用,其使用方式为<br />

其使用方式为<br />

其使用方式为<br />

其使用方式为<br />

`。在这里我们只对两种最常用的编译指令进行介绍<br />

在这里我们只对两种最常用的编译指令进行介绍<br />

在这里我们只对两种最常用的编译指令进行介绍<br />

在这里我们只对两种最常用的编译指令进行介绍。<br />

`define<br />

编译指令<br />

编译指令<br />

编译指令<br />

编译指令`define用于定义<br />

用于定义<br />

用于定义<br />

用于定义<strong>Verilog</strong>中的文本宏<br />

中的文本宏<br />

中的文本宏<br />

中的文本宏。在编译阶段<br />

在编译阶段<br />

在编译阶段<br />

在编译阶段,<br />

`< ><br />

陈国平<br />

上海理工<br />

当编译器遇到<br />

当编译器遇到<br />

当编译器遇到<br />

当编译器遇到`时,使用预定义的文本宏进行替换<br />

使用预定义的文本宏进行替换<br />

使用预定义的文本宏进行替换<br />

使用预定义的文本宏进行替换,它类<br />

它类<br />

它类<br />

它类<br />

似于<br />

似于<br />

似于<br />

似于C语言中的<br />

语言中的<br />

语言中的<br />

语言中的#define结构<br />

结构<br />

结构<br />

结构。在使用预定义的常数或文本宏时<br />

在使用预定义的常数或文本宏时<br />

在使用预定义的常数或文本宏时<br />

在使用预定义的常数或文本宏时,<br />

在宏名前加上前缀号<br />

在宏名前加上前缀号<br />

在宏名前加上前缀号<br />

在宏名前加上前缀号“`”。<br />

`include<br />

使用<br />

使用<br />

使用<br />

使用`include可以在编译期间将一个<br />

可以在编译期间将一个<br />

可以在编译期间将一个<br />

可以在编译期间将一个<strong>Verilog</strong>源文件包含在另一<br />

源文件包含在另一<br />

源文件包含在另一<br />

源文件包含在另一<br />

个<strong>Verilog</strong>文件中<br />

文件中<br />

文件中<br />

文件中,作用类似于<br />

作用类似于<br />

作用类似于<br />

作用类似于C语言中的<br />

语言中的<br />

语言中的<br />

语言中的# include结构<br />

结构<br />

结构<br />

结构。该指<br />

该指<br />

该指<br />

该指<br />

令通常用于将内含全局或公用定义的头文件包含在设计文件中<br />

令通常用于将内含全局或公用定义的头文件包含在设计文件中<br />

令通常用于将内含全局或公用定义的头文件包含在设计文件中<br />

令通常用于将内含全局或公用定义的头文件包含在设计文件中。

3.4 小结<br />

小结<br />

小结<br />

小结<br />

在本章中<br />

在本章中<br />

在本章中<br />

在本章中,我们对<br />

我们对<br />

我们对<br />

我们对<strong>Verilog</strong>中的一些基本概念进行了讨论<br />

中的一些基本概念进行了讨论<br />

中的一些基本概念进行了讨论<br />

中的一些基本概念进行了讨论,深<br />

入理解这些概念将为后续章节的学习提供必要的基础<br />

入理解这些概念将为后续章节的学习提供必要的基础<br />

入理解这些概念将为后续章节的学习提供必要的基础<br />

入理解这些概念将为后续章节的学习提供必要的基础。<br />

在语法上<br />

在语法上<br />

在语法上<br />

在语法上,<strong>Verilog</strong>与C语言十分相似<br />

语言十分相似<br />

语言十分相似<br />

语言十分相似;具有<br />

具有<br />

具有<br />

具有C语言基础的硬件<br />

语言基础的硬件<br />

语言基础的硬件<br />

语言基础的硬件<br />

设计者会发现<br />

设计者会发现<br />

设计者会发现<br />

设计者会发现<strong>Verilog</strong>学习起来很容易<br />

学习起来很容易<br />

学习起来很容易<br />

学习起来很容易。<br />

详细讨论了<br />

详细讨论了<br />

详细讨论了<br />

详细讨论了<strong>Verilog</strong>关于操作符<br />

关于操作符<br />

关于操作符<br />

关于操作符、注释<br />

注释<br />

注释<br />

注释、空白符<br />

空白符<br />

空白符<br />

空白符、数字<br />

数字<br />

数字<br />

数字、字符<br />

字符<br />

字符<br />

字符<br />

串和标识符的词法约定<br />

串和标识符的词法约定<br />

串和标识符的词法约定<br />

串和标识符的词法约定。<br />

陈国平<br />

上海理工<br />

<strong>Verilog</strong>预定义了各种数据类型<br />

预定义了各种数据类型<br />

预定义了各种数据类型<br />

预定义了各种数据类型,包括线网<br />

包括线网<br />

包括线网<br />

包括线网、寄存器<br />

寄存器<br />

寄存器<br />

寄存器、向量<br />

向量<br />

向量<br />

向量、<br />

数字<br />

数字<br />

数字<br />

数字、仿真时间<br />

仿真时间<br />

仿真时间<br />

仿真时间、数组<br />

数组<br />

数组<br />

数组、存储器<br />

存储器<br />

存储器<br />

存储器、参数和字符串<br />

参数和字符串<br />

参数和字符串<br />

参数和字符串。在<strong>Verilog</strong><br />

中采用四值逻辑<br />

中采用四值逻辑<br />

中采用四值逻辑<br />

中采用四值逻辑,此外每个值还可以具有不同的强度等级<br />

此外每个值还可以具有不同的强度等级<br />

此外每个值还可以具有不同的强度等级<br />

此外每个值还可以具有不同的强度等级。使<br />

用这些数据类型可以很精确地表示硬件中的各种元件<br />

用这些数据类型可以很精确地表示硬件中的各种元件<br />

用这些数据类型可以很精确地表示硬件中的各种元件<br />

用这些数据类型可以很精确地表示硬件中的各种元件。<br />

<strong>Verilog</strong>为用户提供了<br />

为用户提供了<br />

为用户提供了<br />

为用户提供了诸如显示<br />

如显示<br />

如显示<br />

如显示、监视<br />

监视<br />

监视<br />

监视、暂停和结束仿真等有<br />

暂停和结束仿真等有<br />

暂停和结束仿真等有<br />

暂停和结束仿真等有<br />

用的系统任务<br />

用的系统任务<br />

用的系统任务<br />

用的系统任务。<br />

编译指令<br />

编译指令<br />

编译指令<br />

编译指令`define用于定义文本宏<br />

用于定义文本宏<br />

用于定义文本宏<br />

用于定义文本宏,`include用于将其<br />

用于将其<br />

用于将其<br />

用于将其他<br />

<strong>Verilog</strong>源文件包含在该文件中<br />

源文件包含在该文件中<br />

源文件包含在该文件中<br />

源文件包含在该文件中