- Page 1 and 2:

FLÁBIO ALBERTO BARDEMAKER BATISTAM

- Page 3 and 4:

MODULAÇÃO VETORIAL APLICADA A RET

- Page 5 and 6:

Abstract of Thesis presented to UFS

- Page 7 and 8:

3.3.1 - Vetores Disponíveis.......

- Page 9 and 10:

6.2.2 - Dimensionamento dos Indutor

- Page 11 and 12:

B.2 - Netlist para a Simulação do

- Page 13 and 14:

LISTA DE SIMBOLOS1. Símbolos Adota

- Page 15 and 16:

5. Sub-Índices UtilizadosSímboloS

- Page 17 and 18:

2Nesta área, podem ser citados est

- Page 19 and 20:

4As referências que tratam deste c

- Page 21 and 22:

6PD A1D B1D C1iO ( t)S A1D A3S B1D

- Page 23 and 24:

8o Análise da forma de implementa

- Page 25 and 26:

10Capítulo 2 - Modulação Vetoria

- Page 27 and 28:

12Aplicando a transformação αβ0

- Page 29 and 30:

14T 1 representa o intervalo de apl

- Page 31 and 32:

16TT′ = ⋅T11 ST1+T2TT′ = ⋅T

- Page 33 and 34:

18Tabela 2.6 - Seqüência de vetor

- Page 35 and 36:

20A Fig. 2-5 mostra a razão cícli

- Page 37 and 38:

22A definição dos setores é infl

- Page 39 and 40:

24O sistema original com referencia

- Page 41 and 42:

26RSEé a resistência equivalente

- Page 43 and 44:

28diA(t) diC(t)2⋅ vA( t) + vC( t)

- Page 45 and 46:

30Aplicando esta transformação à

- Page 47 and 48:

32Através da Fig. 2-11 é possíve

- Page 49 and 50:

34ComoTXD⋅ XD= 1⎡ cos( ω ⋅t)

- Page 51 and 52:

536PS A1S B1S C1iO( t )D A1D B1D C1

- Page 53 and 54:

38De forma semelhante, foi aplicado

- Page 55 and 56:

40200100vAiA( t)( t)0-100-2000s 5ms

- Page 57 and 58:

42800mVDbeta( t)Dalfa( t)400mV0V-40

- Page 59 and 60:

44As razões cíclicas das fases A,

- Page 61 and 62:

46Capítulo 3 - Modulação Vetoria

- Page 63 and 64:

48As etapas de operação para o Se

- Page 65 and 66:

50Na implementação dos vetores di

- Page 67 and 68:

52Tabela 3.2 - Sinais de comando pa

- Page 69 and 70:

54Tabela 3.5 - Sinais de comando pa

- Page 71 and 72:

56T 02T 12T 2T 12T 02cmd Atcmd Btcm

- Page 73 and 74:

58As razões cíclicas dos eixos α

- Page 75 and 76:

60Verifica-se também que a distrib

- Page 77 and 78:

623.4.1. Cálculos Preliminares e C

- Page 79 and 80:

64• Corrente média nos diodos D

- Page 81 and 82:

66Tabela 3.11 - Relações entre os

- Page 83 and 84:

68s + ωCI( s)=−KI⋅s ⋅ s +ZI(

- Page 85 and 86:

70A resposta ao degrau de referênc

- Page 87 and 88:

72⎛s + ω V ⎞⎜ ⋅ ⋅lim⎜s

- Page 89 and 90:

74A resposta ao degrau de referênc

- Page 91 and 92:

76No detalhe da Fig. 3-25 observa-s

- Page 93 and 94:

78450V450440V440430420VVo420410400V

- Page 95 and 96:

801.0V0.5VDd( t)Dq( t)0V0s 10ms 20m

- Page 97 and 98:

8220V20V10VSEL>>0VV(cmd1a)20V10VSEL

- Page 99 and 100:

84Os valores apresentados na Tabela

- Page 101 and 102:

86Neste caso, são definidos os mes

- Page 103 and 104:

884.3. Modulação Vetorial4.3.1. V

- Page 105 and 106:

90Tabela 4.2 - Sinais de comando pa

- Page 107 and 108:

92Tabela 4.4 - Sinais de comando pa

- Page 109 and 110:

94T 22T 12T 0T 12T 22cmd Atcmd Btcm

- Page 111 and 112:

96Neste caso, também se observa qu

- Page 113 and 114:

984.4. Dimensionamento do Estágio

- Page 115 and 116:

100• Corrente média nos diodos D

- Page 117 and 118:

5102As relações para outros sub-s

- Page 119 and 120:

104100.0V87.5V75.0V62.5V50.0V30ms 4

- Page 121 and 122:

106450V450440V440430420VVo420410400

- Page 123 and 124:

1081.0V0.5VDd( t)Dq( t)0V0s 10ms 20

- Page 125 and 126:

1101.0uV1.0uV0VSEL>>-1.0uVV(cmd1a)2

- Page 127 and 128:

112200V200V0V0V-200V-277V20ms 24ms

- Page 129 and 130:

114A Fig. 4-33 mostra a forma de te

- Page 131 and 132:

1164.7. ConclusãoO retificador tri

- Page 133 and 134:

118Neste caso, são consideradas me

- Page 135 and 136:

120120V110V100V90V9.6ms 10.0ms 10.4

- Page 137 and 138:

122A Fig. 5-10 apresenta as razões

- Page 139 and 140:

124100V75V50V30ms 40ms 60ms 80ms 10

- Page 141 and 142:

126450V450440V440430420VVo420410400

- Page 143 and 144:

1285.4.1. Vetores Utilizados e Sina

- Page 145 and 146:

1305.4.2. Seqüência de Vetores e

- Page 147 and 148:

1325.4.3. Modelagem do RetificadorP

- Page 149 and 150:

134O projeto dos controladores para

- Page 151 and 152:

136Verifica-se a mesma dinâmica ap

- Page 153 and 154:

138200vA( t)100iA( t)0-100-2000s 10

- Page 155 and 156:

AADa10.90.80.70.60.50.40.30.20.1ALB

- Page 157 and 158:

142Como principal diferença entre

- Page 159 and 160:

144PPPD A1D B1D C1iO() tD A1D B1D C

- Page 161 and 162:

146Neste caso, a razão cíclica n

- Page 163 and 164:

148Para uma análise mais aprofunda

- Page 165 and 166:

150Tabela 6.1 - Especificações de

- Page 167 and 168:

152C2P ⋅ ⋅T= = 4296 μFO hold-u

- Page 169 and 170:

154• Corrente média nos diodos D

- Page 171 and 172:

156• Perdas totais diodo D 34 :PD

- Page 173 and 174:

158RθT− THD34 AHAmax= =PSEMI0,13

- Page 175 and 176:

160Para f A= 10 kHz e considerando

- Page 177 and 178:

162+15VR493.3k25K13 1C29 2.2pR51R50

- Page 179 and 180:

164Saída 2: -15V/500mA para a alim

- Page 181 and 182:

1667.2.1. Malha de CorrenteA funç

- Page 183 and 184:

168νZIνCI= 2⋅π⋅ fv = 6498 ra

- Page 185 and 186:

170• Expressão (7.25): erro de c

- Page 187 and 188:

172A freqüência de corte para a m

- Page 189 and 190:

174Na Fig. 7-7 é mostrada a respos

- Page 191 and 192:

176A posição dos pólos em malha

- Page 193 and 194:

178A Fig. 7-14 mostra a lógica uti

- Page 195 and 196:

180referênciaNa Fig. 7-19 é mostr

- Page 197 and 198:

182O comportamento das razões cíc

- Page 199 and 200:

184604020IA,IB,IC (A)0-20-40-600.4

- Page 201 and 202:

1867.5. Programação7.5.1. Fluxogr

- Page 203 and 204:

188É reservada uma região da mem

- Page 205 and 206:

190senoides utilizadas nas transfor

- Page 207 and 208:

192vO() ttFig. 7-31 - Comportamento

- Page 209 and 210:

1947.5.8. Definição dos Setores e

- Page 211 and 212:

196vA () tiA() ta) Tensão de refer

- Page 213 and 214:

198A Fig. 8-4 mostra os sinais de c

- Page 215 and 216:

200Fig. 8-6 - Razões cíclicas par

- Page 217 and 218:

202a) Correntes de entrada para 177

- Page 219 and 220:

204Na Fig. 8-10 (a) observa-se a te

- Page 221 and 222:

206DA( t )DB( t)DC( t)iA( t )Fig. 8

- Page 223 and 224:

208Tabela 8-3 - Comparação entre

- Page 225 and 226:

210Neste caso, observa-se uma maior

- Page 227 and 228:

212Na Fig. 8-22 (a) observa-se tens

- Page 229 and 230: 214Neste caso, observa-se que as fo

- Page 231 and 232: 216Estas grandezas apresentam forma

- Page 233 and 234: 218VS( t)iS( t )V ( t)D1iD1( t )a)

- Page 235 and 236: 2208.5.2. Operação com V L = 380

- Page 237 and 238: 222Tabela 8-7 - Fator de potência.

- Page 239 and 240: 224Na Fig. 8-41, na Fig. 8-42 e na

- Page 241 and 242: 226CONCLUSÃO GERALForam demonstrad

- Page 243 and 244: 228dos valores teóricos, validando

- Page 245 and 246: 230R83C386.94kV15n714nVo5/400R82 TL

- Page 247 and 248: 232V_V46 V15n 0 DC -15D_D43 $N_0005

- Page 249 and 250: I234ANEXO B. Diagrama Esquemático

- Page 251 and 252: 236um5um1Eq1um1Eq4Dalfa1.225Dalfa1.

- Page 253 and 254: 238.ends qualyuniy20k_S36.subckt qu

- Page 255 and 256: 240R97C497.7kV15n646nVo5/400R92 TL0

- Page 257 and 258: 242E_SUM26 $N_0009 0 VALUE{V($N_001

- Page 259 and 260: 244ANEXO D. Dimensionamento do Est

- Page 261 and 262: 246D.2. Dimensionamento dos Indutor

- Page 263 and 264: 248⎧ vA(t) + vB(t) + vC(t) = 0⎪

- Page 265 and 266: 250P 0,613⋅V −2⋅η⋅VI = ⋅

- Page 267 and 268: 252ππ⎧⎫6 61 ⎪⎪IS = ⋅⎨

- Page 269 and 270: 254ID3456MEDdiodos D I3456 .0⎧⎫

- Page 271 and 272: 256ANEXO E. Esquemas Elétricos das

- Page 273 and 274: 258C7100pF1110U2ALF347324111+-V+V-O

- Page 275 and 276: 260GNDVsincA10k56nR54C31+15VR473.3k

- Page 277 and 278: 262Barra de PinosBarra de Pinos1Bar

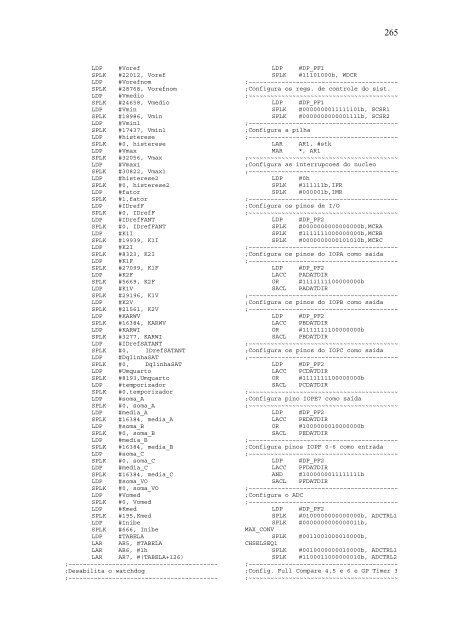

- Page 279: 264int10: B int10int11: B int11int1

- Page 283 and 284: 268SACL IDrefSATMAR *,AR4LDP #IDref

- Page 285 and 286: 270; Dqlinha (total)LDP #DqlinhaPAD

- Page 287 and 288: 272LDP #KD_1LT KD_1MPY DalfaSPACLDP

- Page 289 and 290: 274CLRC SXMCLRC OVM; testa Inibe pa

- Page 291 and 292: 276REFERÊNCIAS BIBLIOGRÁFICAS[1]

- Page 293 and 294: 278[21] AREDES, M.; Active Power Li

- Page 295 and 296: 280[44] BOTTERÓN, F.; Análise, Pr

- Page 297: 282[67] BORGONOVO, Deivis; Análise