Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

EPUSP — <strong>PCS</strong> 2011 — Laboratório Digital<br />

GERADOR DE SINAIS<br />

Versão 2013<br />

RESUMO<br />

Esta experiência tem como objetivo a familiarização com o problema da conversão <strong>de</strong> sinais digitalizados<br />

em sinais analógicos, o conversor digital-analógico <strong>de</strong> 8 bits DAC0800 da National e apresenta também a<br />

memória EPROM 2716. A parte experimental apresenta o projeto <strong>de</strong> um gerador <strong>de</strong> sinais analógicos com<br />

várias formas <strong>de</strong> onda (senói<strong>de</strong>, rampa, etc) usando a placa <strong>de</strong> <strong>de</strong>senvolvimento FPGA DE2 da Altera.<br />

OBJETIVOS<br />

Após a conclusão <strong>de</strong>sta experiência, os seguintes tópicos <strong>de</strong>vem ser conhecidos pelos alunos:<br />

<br />

<br />

<br />

Estudo <strong>de</strong> conversores D/A;<br />

Aplicação <strong>de</strong> memórias;<br />

Descrição <strong>de</strong> memórias ROM em VHDL.<br />

1. PARTE TEÓRICA<br />

1.1. Introdução à Conversão <strong>de</strong> <strong>Sinais</strong><br />

A gran<strong>de</strong> maioria das gran<strong>de</strong>zas físicas com as quais lidamos são gran<strong>de</strong>zas analógicas por natureza. Tais<br />

gran<strong>de</strong>zas, como temperatura, pressão, velocida<strong>de</strong>, etc, são representadas por valores contínuos e,<br />

assim, para po<strong>de</strong>rem ser processadas por sistemas digitais precisam antes ser convertidas para uma<br />

ca<strong>de</strong>ia <strong>de</strong> bits. Esta conversão é conhecida como Conversão Analógica-Digital. De forma similar, para que<br />

os sistemas digitais possam controlar ou atuar sobre variáveis analógicas torna-se necessária a<br />

<strong>de</strong>codificação <strong>de</strong> uma ca<strong>de</strong>ia <strong>de</strong> bits em uma gran<strong>de</strong>za que possa assumir uma gama contínua <strong>de</strong> valores<br />

e não apenas níveis discretos especificados a partir dos níveis lógicos ‘0’ e ‘1’. Esta conversão é<br />

conhecida como Conversão Digital-Analógica.<br />

Os equipamentos que convertem gran<strong>de</strong>zas físicas em sinais elétricos e vice-versa são chamados<br />

transdutores. Por exemplo, gran<strong>de</strong>zas como temperaturas, velocida<strong>de</strong>s e posições são transformadas em<br />

correntes ou tensões proporcionais. Como exemplo <strong>de</strong> transdutor po<strong>de</strong>-se citar o termistor, que muda o<br />

valor <strong>de</strong> sua resistência conforme a temperatura a que estiver submetido.<br />

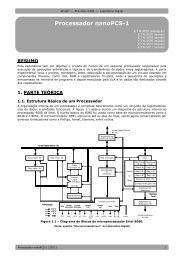

A figura 1.1 apresenta o ciclo completo <strong>de</strong> processamento <strong>de</strong> uma gran<strong>de</strong>za física, envolvendo:<br />

<br />

<br />

<br />

<br />

<br />

<br />

<br />

A conversão inicial do sinal oriundo do processo físico, através da passagem por um<br />

Transdutor, criando o sinal analógico convertido;<br />

O condicionamento <strong>de</strong>sse sinal (se necessário), por meio <strong>de</strong> um Condicionador <strong>de</strong> Sinal,<br />

gerando o sinal analógico condicionado;<br />

A conversão do sinal por um Conversor A/D, resultando no sinal digitalizado;<br />

O processamento do sinal realizado pelo Sistema Digital;<br />

A conversão do sinal digital presente na saída do Sistema Digital feita por um Conversor<br />

D/A;<br />

O condicionamento <strong>de</strong>sse sinal (se necessário), por meio <strong>de</strong> um Condicionador <strong>de</strong> Sinal,<br />

gerando o sinal analógico condicionado; e<br />

A conversão final do sinal, através da passagem por outro Transdutor, gerando um sinal que<br />

po<strong>de</strong> ser utilizado novamente pelo processo físico.<br />

<strong>Gerador</strong> <strong>de</strong> <strong>Sinais</strong> – quadrimestral (2013) 1

EPUSP — <strong>PCS</strong> 2011 — Laboratório Digital<br />

Conversor<br />

Sinal <strong>de</strong><br />

Processo<br />

Físico<br />

Trans<br />

dutor<br />

Sinal<br />

Analógico<br />

Convertido<br />

Condicionador<br />

<strong>de</strong> Sinal<br />

Sinal<br />

Analógico<br />

Condicionado<br />

A<br />

D<br />

Sinal<br />

Digital<br />

Sistema<br />

Digital<br />

Conversor<br />

Sinal <strong>de</strong><br />

Processo<br />

Físico<br />

Trans<br />

dutor<br />

Sinal<br />

Analógico<br />

Condicionado<br />

Condicionador<br />

<strong>de</strong> Sinal<br />

Sinal<br />

Analógico<br />

D<br />

A<br />

Sinal<br />

Digital<br />

Figura 1.1 - Etapas <strong>de</strong> Tratamento <strong>de</strong> Gran<strong>de</strong>za Físicas.<br />

Até algum tempo atrás, o processamento dos sinais analógicos era <strong>de</strong>sempenhado, em sua<br />

maioria, por sistemas exclusivamente analógicos, baseados em circuitos integradores, somadores, etc.<br />

Com o <strong>de</strong>senvolvimento dos sistemas digitais, no que diz respeito à funcionalida<strong>de</strong>, velocida<strong>de</strong>,<br />

confiabilida<strong>de</strong> e custo, estes passaram a ocupar espaços antes exclusivos <strong>de</strong> sistemas analógicos.<br />

Os sistemas digitais apresentam maior flexibilida<strong>de</strong> e facilida<strong>de</strong> <strong>de</strong> <strong>de</strong>puração. Entretanto um<br />

ponto crítico é a interface entre os circuitos digitais e os circuitos analógicos. Assim, <strong>de</strong>vem-se ter os<br />

cuidados necessários no projeto <strong>de</strong>stas interfaces uma vez que elas é também <strong>de</strong>terminam a precisão,<br />

rapi<strong>de</strong>z <strong>de</strong> resposta e confiabilida<strong>de</strong> no processamento digital <strong>de</strong> informações.<br />

1.2. Técnicas <strong>de</strong> Conversão D/A<br />

Existem várias técnicas <strong>de</strong> conversão Digital-Analógica, em função da precisão <strong>de</strong>sejada e do tempo<br />

máximo aceitável para se realizar esta conversão, a saber (Matsunaga e Tsugawa, 2005):<br />

<br />

<br />

<br />

<br />

<br />

<br />

Conversão D/A com resistências pon<strong>de</strong>radas;<br />

Conversão D/A com resistências <strong>de</strong> pesos binários;<br />

Conversão D/A em escada R-2R;<br />

Conversão D/A com re<strong>de</strong> <strong>de</strong> capacitores com pesos binários;<br />

Conversão D/A com oversampling;<br />

entre outras.<br />

Uma técnica <strong>de</strong> conversão bastante simples é aquela baseada em uma re<strong>de</strong> resistiva R-2R. Uma<br />

vantagem <strong>de</strong>sta técnica é o uso <strong>de</strong> apenas dois valores distintos <strong>de</strong> resistores. A figura 1.2 apresenta<br />

esse tipo <strong>de</strong> re<strong>de</strong> resistiva.<br />

Figura 1.2 – Re<strong>de</strong> resistiva R-2R para 4 bits.<br />

<strong>Gerador</strong> <strong>de</strong> <strong>Sinais</strong> – quadrimestral (2013) 2

EPUSP — <strong>PCS</strong> 2011 — Laboratório Digital<br />

Uma alternativa é usar uma re<strong>de</strong> NR. Aqui é utilizada uma re<strong>de</strong> <strong>de</strong> N resistores em série, on<strong>de</strong> N<br />

correspon<strong>de</strong> ao número <strong>de</strong> divisões discretas dada pelo código digital, ou seja, trata-se <strong>de</strong> um gran<strong>de</strong><br />

divisor resistivo <strong>de</strong> tensão. Para um conversor <strong>de</strong> 4 bits necessita-se <strong>de</strong> uma re<strong>de</strong> 16R, ou seja, 16<br />

resistores iguais em série. Para 8 bits, há a necessida<strong>de</strong> <strong>de</strong> uma re<strong>de</strong> 256R. O divisor resistivo conectado<br />

a um conjunto <strong>de</strong> chaves, controlado por um gran<strong>de</strong> <strong>de</strong>codificador, é a base <strong>de</strong>ste conversor. A figura 1.3<br />

apresenta esse tipo <strong>de</strong> re<strong>de</strong>.<br />

Figura 1.3 – Re<strong>de</strong> resistiva NR.<br />

Para maiores informações sobre as técnicas <strong>de</strong> conversão digital-analógica, consulte as<br />

referências (Matsunaga e Tsugawa, 2005) ou (Tocci et al. 2011).<br />

<strong>Gerador</strong> <strong>de</strong> <strong>Sinais</strong> – quadrimestral (2013) 3

EPUSP — <strong>PCS</strong> 2011 — Laboratório Digital<br />

2. PARTE EXPERIMENTAL<br />

O circuito do <strong>Gerador</strong> <strong>de</strong> <strong>Sinais</strong> será <strong>de</strong>senvolvido <strong>de</strong> forma integrada, dividindo a implementação do<br />

circuito na placa <strong>de</strong> <strong>de</strong>senvolvimento FPGA DE2 da Altera e no painel <strong>de</strong> montagens experimentais. A<br />

parte digital do circuito <strong>de</strong>verá ser implementado na placa DE2 e os componentes analógicos no painel <strong>de</strong><br />

montagens experimentais. A integração das partes <strong>de</strong>ve ser realizada com cuidado para não danificar as<br />

partes.<br />

2.1. Familiarização com o Conversor D/A DAC0800<br />

Utilizar, para o conversor D/A DAC0800, a configuração mostrada na Figura 2.1, testando, estaticamente,<br />

o seu funcionamento com as chaves C0-C7 do painel <strong>de</strong> montagens ligadas nas entradas E1-E8.<br />

Figura 2.1 - Configuração do Conversor DAC0800.<br />

a) Elaborar uma tabela e um gráfico da tensão <strong>de</strong> saída código <strong>de</strong> entrada. A tensão <strong>de</strong> saída é<br />

positiva ou negativa?<br />

b) Qual é a característica apresentada pelo gráfico do item a) para os valores iniciais do código <strong>de</strong><br />

entrada?<br />

c) Qual é esta característica, para os valores finais?<br />

d) Como os 8 bits <strong>de</strong> entrada do DAC0800 po<strong>de</strong>rão ser conectados nos 6 bits <strong>de</strong> saída da memória<br />

EPROM no projeto do gerador <strong>de</strong> sinais para que a amplitu<strong>de</strong> do sinal gerado seja maximizado?<br />

DICA: qual é o bit mais significativo da entrada digital do conversor D/A?<br />

e) Em seguida ligar o buffer 74365 nas 6 entradas selecionadas do DAC0800 como preparação da<br />

conexão com a placa FPGA DE2.<br />

DICA: verifique a conexão dos sinais do buffer testando o circuito com a ligação das 6 entradas nas<br />

chaves novamente. Teste alguns pontos e compare-os com os valores do gráfico do item 2.1.a).<br />

<strong>Gerador</strong> <strong>de</strong> <strong>Sinais</strong> – quadrimestral (2013) 4

EPUSP — <strong>PCS</strong> 2011 — Laboratório Digital<br />

2.2. Familiarização com a EPROM<br />

Uma <strong>de</strong>scrição em VHDL <strong>de</strong> um circuito similar a EPROM 2716 (2048x8) <strong>de</strong>verá ser <strong>de</strong>senvolvido. A<br />

interface <strong>de</strong>ste componente <strong>de</strong>verá seguir aquele <strong>de</strong>finido na figura 2.2. O conteúdo é especificado pelo<br />

arquivo eprom-mapa.mif disponível no site da disciplina.<br />

Figura 2.2 – Interface da memória em VHDL.<br />

A verificação <strong>de</strong>ste componente <strong>de</strong>verá ser realizada e documentada no planejamento. Utilizar a saída <strong>de</strong><br />

um circuito contador <strong>de</strong> 8 bits nas entradas <strong>de</strong> en<strong>de</strong>reços A0-A7 da memória EPROM e três chaves <strong>de</strong><br />

entrada F0 a F2 nas entradas A8-A10 da EPROM. Use um botão ou sinal <strong>de</strong> relógio na entrada <strong>de</strong> clock do<br />

contador. Observar a saída da memória, conforme a figura 2.3 abaixo.<br />

Figura 2.3 – Familiarização da memória.<br />

f) Verifique o conteúdo da memória, acionando a entrada do contador. Consulte o mapa da EPROM<br />

disponível no Laboratório Digital.<br />

g) Verifique também o comportamento do bit b 7 da memória. Como este bit varia em função do<br />

en<strong>de</strong>reço da memória?<br />

<strong>Gerador</strong> <strong>de</strong> <strong>Sinais</strong> – quadrimestral (2013) 5

EPUSP — <strong>PCS</strong> 2011 — Laboratório Digital<br />

2.3. Especificação do Projeto do <strong>Gerador</strong> <strong>de</strong> <strong>Sinais</strong><br />

Projetar um sistema gerador <strong>de</strong> sinais analógicos, com a saída apresentando as funções seno, x 2 ,<br />

exponencial, rampa, elíptica, x 3 e Gaussiana, consi<strong>de</strong>rando o seguinte diagrama <strong>de</strong> blocos (Figura 2.4):<br />

Figura 2.4 - Diagrama <strong>de</strong> Blocos do <strong>Gerador</strong> <strong>de</strong> Funções.<br />

Consi<strong>de</strong>re as seguintes condições:<br />

<br />

<br />

As funções foram digitalizadas e os dados estão armazenados em uma memória EPROM, cada<br />

uma em 256 posições consecutivas, que formam uma página (Obs.: a função rampa está<br />

repetida);<br />

Os bits da saída da EPROM b 7 , b 6 , ..., b 0 são assim constituídos:<br />

- b 0 a b 5 : valor digitalizado da função;<br />

- b 6 : não utilizado;<br />

- b 7 : sinal para sincronização do osciloscópio.<br />

Os “mapas” <strong>de</strong> gravação da EPROM estão disponíveis no Laboratório Digital.<br />

<br />

<br />

<br />

Para selecionar uma função <strong>de</strong>ve-se acionar o botão FUNÇÃO (o que <strong>de</strong>ve fazer acen<strong>de</strong>r o LED L0<br />

‘EM SELEÇÃO’, indicando processo <strong>de</strong> seleção em curso) e escolhe-se a página <strong>de</strong> memória,<br />

através das chaves <strong>de</strong> INDICAÇÃO DE PÁGINA;<br />

Para mostrar a função analógica no osciloscópio <strong>de</strong>ve-se acionar o botão MOSTRA, o que <strong>de</strong>ve<br />

apagar o LED EM SELEÇÃO e acen<strong>de</strong>r o LED EM OPERAÇÃO, indicando o modo ‘EM OPERAÇÃO’.<br />

A função <strong>de</strong>ve ser mostrada continuadamente, até que nova requisição <strong>de</strong> seleção seja feita<br />

(acionando novamente o botão FUNÇÃO).<br />

OBSERVAÇÕES:<br />

<br />

<br />

Enquanto o gerador estiver mostrando uma função, qualquer acionamento das chaves <strong>de</strong><br />

seleção <strong>de</strong> página e do botão MOSTRA <strong>de</strong>ve ser inócuo;<br />

Trabalhar com tensões entre +5V e -5V na saída do conversor.<br />

<strong>Gerador</strong> <strong>de</strong> <strong>Sinais</strong> – quadrimestral (2013) 6

EPUSP — <strong>PCS</strong> 2011 — Laboratório Digital<br />

2.4. Execução da Montagem<br />

A montagem do circuito <strong>de</strong>verá ser realizada em duas etapas: primeiro a parte analógica composta pelo<br />

DAC0800 e o buffer 74365 que já <strong>de</strong>verá estar montado (no item 2.1). Em seguida, a parte digital <strong>de</strong>verá<br />

ser testada <strong>de</strong> forma in<strong>de</strong>pen<strong>de</strong>nte na placa DE2. Finalmente, ambas as partes po<strong>de</strong>m ser integradas<br />

para formar o circuito gerador <strong>de</strong> sinais.<br />

Adotar a seguinte <strong>de</strong>signação <strong>de</strong> sinais:<br />

• PÁGINA[0..2] : chaves SW0 a SW2<br />

• FUNÇÃO : botão KEY0<br />

• MOSTRA : botão KEY1<br />

• FUNÇÃO : botão KEY3<br />

• CLOCK : clock interno <strong>de</strong> 50 MHz (CLK_50)<br />

• MEMÓRIA[0..7] : GPIO_0[0] a GPIO_0[7]<br />

DICA: lembrem-se que os botões na placa<br />

DE2 são ativos em baixo. Os projetos<br />

<strong>de</strong>vem levar isto em consi<strong>de</strong>ração. Use a<br />

tabela <strong>de</strong> <strong>de</strong>signação <strong>de</strong> pinos da placa<br />

DE2.<br />

h) Como a parte digital do circuito po<strong>de</strong> ser <strong>de</strong>monstrado ao professor.<br />

DICA: use sinais extras <strong>de</strong> <strong>de</strong>puração em leds e displays.<br />

CUIDADO: ligar em PRIMEIRO LUGAR o sinal <strong>de</strong> TERRA da placa DE2 (pino 12 do conector<br />

GPIO_0) com o pino <strong>de</strong> TERRA do painel <strong>de</strong> montagens experimentais. Em caso <strong>de</strong> negligência,<br />

a placa DE2 po<strong>de</strong> ser danificada!<br />

i) Montar o circuito gerador <strong>de</strong> sinais e mostrar as 8 funções armazenadas. Apresente a sequência <strong>de</strong><br />

montagem adotada.<br />

j) Construa uma tabela i<strong>de</strong>ntificando as funções geradas para cada código. Use o bit b7 da memória<br />

EPROM para sincronizar no osciloscópio o sinal analógico da saída do conversor.<br />

k) Tentar utilizar outros sinais <strong>de</strong> sincronização distintos daquele armazenado na memória (bit b 7 ).<br />

Que outras formas <strong>de</strong> sincronização po<strong>de</strong>m ser utilizadas? Justifique.<br />

l) Baseado no projeto <strong>de</strong>senvolvido pela equipe, discuta quais são os fatores que afetam o<br />

funcionamento do circuito em função da frequência <strong>de</strong> operação.<br />

m) Varie a frequência <strong>de</strong> operação e comente o funcionamento do circuito do gerador <strong>de</strong> sinais.<br />

Perguntas:<br />

1. O circuito é funcional a baixas frequências? Como é a forma <strong>de</strong> onda gerada nestes casos?<br />

2. Há uma limitação superior para o funcionamento correto do gerador <strong>de</strong> sinais? Que fatores são<br />

<strong>de</strong>terminantes nesta limitação?<br />

3. A página <strong>de</strong> dados na EPROM para cada forma <strong>de</strong> onda tem 256 posições. Como o projeto do gerador<br />

<strong>de</strong> sinais po<strong>de</strong>ria ser melhorado com relação à “<strong>de</strong>finição” da forma <strong>de</strong> onda gerada?<br />

4. O que ocorre na saída do circuito se o número da página da EPROM for modificado durante a<br />

apresentação <strong>de</strong> uma <strong>de</strong>terminada forma <strong>de</strong> onda?<br />

2.5. Modificação do Circuito<br />

n) (OPCIONAL) Implemente a modificação proposta pelo professor. Documente o circuito e apresente<br />

seu funcionamento <strong>de</strong> forma objetiva e convincente.<br />

<strong>Gerador</strong> <strong>de</strong> <strong>Sinais</strong> – quadrimestral (2013) 7

EPUSP — <strong>PCS</strong> 2011 — Laboratório Digital<br />

3. BIBLIOGRAFIA<br />

<br />

<br />

FREGNI, Edson e SARAIVA, Antonio M. Engenharia do Projeto Lógico Digital: Conceitos e<br />

Prática. Editora Edgard Blücher Ltda, 1995.<br />

TOCCI, R. J.; WIDMER, N. S.; MOSS, G. L. Digital Systems: principles and applications.<br />

11 th ed., Prentice-Hall, 2011.<br />

WAKERLY, John F. Digital Design Principles & Practices. 4 th edition, Prentice Hall, 2006.<br />

KLEITZ, William. Digital Electronics - A Practical Approach. Prentice-Hall, 1987.<br />

TOKLEIN, Roger L. Princípios Digitais. Schaum-McGraw Hill, 1983.<br />

Signetics. TTL Logic Data Manual. 1982.<br />

<br />

<br />

LSD-EPUSP. Conversores Analógico-Digitais. Apostila <strong>de</strong> PEL308, RA/ES.<br />

MATSUNAGA, A. M. e TSUGAWA, M. O. Conversor Digital/Analógico. Apostila <strong>de</strong> <strong>PCS</strong>2498<br />

Laboratório <strong>de</strong> Processadores II. Versão <strong>de</strong> 2005, revisado por André Riyuiti Hirakawa e Carlos<br />

Eduardo Cugnasca.<br />

4. MATERIAL DISPONÍVEL<br />

<br />

<br />

Circuitos Integrados TTL (parte digital):<br />

- 7400, 7404, 7408, 7432, 7474, 74161, 74163, 74175, 74193.<br />

- 74365 – buffer para interface entre a placa DE2 e o DAC0800.<br />

- 2716 - Memória EPROM.<br />

Outros Componentes (parte analógica):<br />

- Resistores: 4,7 K<br />

- Capacitores: 10nF<br />

- DAC 0800 - Conversor D/A<br />

5. EQUIPAMENTOS NECESSÁRIOS<br />

1 painel <strong>de</strong> montagens experimentais.<br />

1 fonte <strong>de</strong> alimentação fixa, 5V 5%, 4A.<br />

1 fonte <strong>de</strong> alimentação variável 12V 10%, 0,5 A<br />

1 osciloscópio digital.<br />

1 multímetro digital.<br />

1 placa <strong>de</strong> <strong>de</strong>senvolvimento FPGA DE2 da Altera com o dispositivo Altera Cyclone II EP2C35F672C6.<br />

1 computador PC com programa Altera Quartus II e interface USB.<br />

Histórico <strong>de</strong> Revisões<br />

E.T.M./2007 – adaptação<br />

E.T.M./2011 – revisão<br />

E.T.M./2012 – revisão<br />

E.T.M./2013 – revisão da parte experimental<br />

<strong>Gerador</strong> <strong>de</strong> <strong>Sinais</strong> – quadrimestral (2013) 8