Dynamic Voltage Scaling Dissertação para obtenção do Grau de ...

Dynamic Voltage Scaling Dissertação para obtenção do Grau de ...

Dynamic Voltage Scaling Dissertação para obtenção do Grau de ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

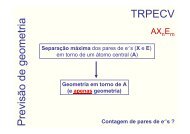

4. Demonstra<strong>do</strong>r FPGA<br />

4.4.3 Multiplexer tri-state (cut_speed)<br />

O sinal cut_speed foi cria<strong>do</strong> <strong>para</strong> facilitar o tratamento da informação gerada pelo Sensor<br />

Global. Inicialmente foi implementa<strong>do</strong> um codifica<strong>do</strong>r <strong>para</strong> converter o código termómetro numa<br />

palavra digital que posteriormente seria com<strong>para</strong>da com a palavra <strong>de</strong> calibração <strong>para</strong> <strong>de</strong>finir qual a<br />

categoria <strong>de</strong> velocida<strong>de</strong> a atribuir. No entanto, após alguns testes percebeu-se que esta abordagem<br />

tem eleva<strong>do</strong>s custos no caso <strong>de</strong> ser implementada com portas lógicas, quer na quantida<strong>de</strong> <strong>de</strong> portas<br />

necessárias mas principalmente no tempo <strong>de</strong> atraso. Isto porque na FPGA utilizada apenas é<br />

possível implementar codifica<strong>do</strong>res lógicos em que os bits mais significativos <strong>de</strong>pen<strong>de</strong>m <strong>de</strong> to<strong>do</strong>s os<br />

anteriores. Esta situação é particularmente gravosa uma vez que requer esperar pela propagação <strong>do</strong><br />

código termómetro no codifica<strong>do</strong>r a cada verificação efectuada pelo sensor.<br />

Como solução final, implementou-se este conceito mas no senti<strong>do</strong> inverso. Deste mo<strong>do</strong>,<br />

preten<strong>de</strong> usar-se um <strong>de</strong>scodifica<strong>do</strong>r <strong>para</strong> converter a palavra <strong>de</strong> calibração e <strong>de</strong>sse mo<strong>do</strong> atacar um<br />

conjunto <strong>de</strong> buffers tri-state liga<strong>do</strong>s ao código termómetro. O objectivo é multiplexar os <strong>do</strong>is bits<br />

consecutivos <strong>do</strong> código termómetro correspon<strong>de</strong>ntes à calibração <strong>do</strong> caminho crítico a simular. Na<br />

Figura 4.9 po<strong>de</strong> ver-se que são utiliza<strong>do</strong>s <strong>do</strong>is multiplexers, um <strong>para</strong> cada bit <strong>do</strong> sinal cut_speed,<br />

correspon<strong>de</strong>ntes à selecção <strong>do</strong>s <strong>do</strong>is bits consecutivos <strong>do</strong> código termómetro. Os <strong>do</strong>is mutiplexers<br />

têm a vantagem <strong>de</strong> ser realiza<strong>do</strong>s usan<strong>do</strong> apenas um <strong>de</strong>scodifica<strong>do</strong>r. Isto é feito <strong>de</strong>sfasan<strong>do</strong> a<br />

sequência com que os bits <strong>do</strong> <strong>de</strong>scodifica<strong>do</strong>r entram no segun<strong>do</strong> conjunto <strong>de</strong> buffers tri-state. A<br />

utilização <strong>de</strong>stes buffers tem também a vantagem <strong>de</strong> po<strong>de</strong>r criar gran<strong>de</strong>s multiplexers <strong>de</strong> atraso<br />

reduzi<strong>do</strong>, uma vez que evita toda a lógica sequencial e tira proveito <strong>do</strong> facto <strong>do</strong> <strong>de</strong>scodifica<strong>do</strong>r ficar<br />

estático após a calibração.<br />

Figura 4.9 – Multiplexer tri-state <strong>para</strong> geração <strong>do</strong> sinal cut_speed<br />

37