Dynamic Voltage Scaling Dissertação para obtenção do Grau de ...

Dynamic Voltage Scaling Dissertação para obtenção do Grau de ...

Dynamic Voltage Scaling Dissertação para obtenção do Grau de ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

4. Demonstra<strong>do</strong>r FPGA<br />

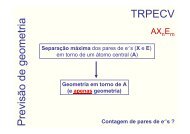

A lógica aritmética utilizada no cálculo da palavra tensão é apresentada Figura 4.8. É utiliza<strong>do</strong><br />

um registo <strong>para</strong> guardar a palavra <strong>de</strong> tensão Vprog a enviar ao DCDC através bloco SPI e um<br />

multiplexer <strong>para</strong> inicializar o DCDC com a palavra <strong>de</strong> tensão Vmax. Durante o processo <strong>de</strong><br />

optimização é utiliza<strong>do</strong> um Soma<strong>do</strong>r/Subtractor <strong>para</strong> incrementar ou <strong>de</strong>crementar uma unida<strong>de</strong> à<br />

palavra <strong>de</strong> tensão Vprog. Por fim são utiliza<strong>do</strong>s <strong>do</strong>is com<strong>para</strong><strong>do</strong>res <strong>para</strong> interromper a optimização<br />

caso sejam alcança<strong>do</strong>s os limites Vmax ou Vmin.<br />

4.4.2 Comportamento<br />

Neste subcapítulo será <strong>de</strong>talhada a função <strong>de</strong> cada esta<strong>do</strong> apresenta<strong>do</strong> na Figura 4.7.<br />

<br />

<br />

<br />

<br />

<br />

<br />

<br />

<br />

<br />

INIT – esta<strong>do</strong> inicial no qual é transferida a palavra <strong>de</strong> tenção Vmax <strong>para</strong> o registo conten<strong>do</strong><br />

Vprog. O processo é realiza<strong>do</strong> seleccionan<strong>do</strong> a entrada Vmax no multiplexer e activan<strong>do</strong> a<br />

escrita no registo.<br />

Verify – esta<strong>do</strong> no qual é avalia<strong>do</strong> o <strong>de</strong>sempenho <strong>do</strong> circuito através <strong>do</strong> sinal cut_speed.<br />

Comp_add – esta<strong>do</strong> no qual é com<strong>para</strong>da a actual palavra <strong>de</strong> tensão Vprog com Vmax a fim <strong>de</strong><br />

verificar se foi atingi<strong>do</strong> o limite superior <strong>de</strong> tensão.<br />

Comp_sub – esta<strong>do</strong> no qual é com<strong>para</strong>da a actual palavra <strong>de</strong> tensão Vprog com Vmin a fim <strong>de</strong><br />

verificar se foi atingi<strong>do</strong> o limite inferior <strong>de</strong> tensão.<br />

Increase – esta<strong>do</strong> no qual é efectua<strong>do</strong> o incremento <strong>de</strong> uma unida<strong>de</strong> à palavra <strong>de</strong> tensão<br />

Vprog. O processo é realiza<strong>do</strong> seleccionan<strong>do</strong> no multiplexer a entrada vinda <strong>do</strong><br />

Soma<strong>do</strong>r/Subtractor, activan<strong>do</strong> a escrita no registo e or<strong>de</strong>nan<strong>do</strong> a operação <strong>de</strong> soma ao<br />

Soma<strong>do</strong>r/Subtractor.<br />

Decrease – esta<strong>do</strong> no qual é efectua<strong>do</strong> o <strong>de</strong>cremento <strong>de</strong> uma unida<strong>de</strong> à palavra <strong>de</strong> tensão<br />

Vprog. O processo é realiza<strong>do</strong> seleccionan<strong>do</strong> no multiplexer a entrada vinda <strong>do</strong><br />

Soma<strong>do</strong>r/Subtractor, activan<strong>do</strong> a escrita no registo e or<strong>de</strong>nan<strong>do</strong> a operação <strong>de</strong> subtracção ao<br />

Soma<strong>do</strong>r/Subtractor.<br />

SPI_Write – esta<strong>do</strong> no qual é dada or<strong>de</strong>m ao bloco SPI <strong>para</strong> comunicar a nova palavra <strong>de</strong><br />

tensão Vprog ao DCDC.<br />

Wait_1 – esta<strong>do</strong> no qual se aguarda que o sinal ready venha a ‘0’. Este esta<strong>do</strong> é essencial uma<br />

vez que a transição <strong>para</strong> ‘1’ <strong>do</strong> sinal ready indica a presença <strong>de</strong> novos da<strong>do</strong>s <strong>de</strong> <strong>de</strong>sempenho<br />

vin<strong>do</strong>s <strong>do</strong> Sensor Global. Por teste motivo é necessário esperar a sua vinda a ‘0’ uma vez que o<br />

perío<strong>do</strong> <strong>do</strong> sinal ready é muito superior ao tempo que a máquina <strong>de</strong> esta<strong>do</strong>s <strong>de</strong>mora <strong>para</strong><br />

realizar as operações até este esta<strong>do</strong>.<br />

Wait_2 – esta<strong>do</strong> no qual se aguarda pela conclusão da transmissão <strong>de</strong> da<strong>do</strong>s SPI (sinal busy)<br />

bem como a chegada <strong>de</strong> novos da<strong>do</strong>s por parte <strong>do</strong> Sensor Global (sinal ready).<br />

36