Dynamic Voltage Scaling Dissertação para obtenção do Grau de ...

Dynamic Voltage Scaling Dissertação para obtenção do Grau de ...

Dynamic Voltage Scaling Dissertação para obtenção do Grau de ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

3. Sensor Global<br />

3.2 Sensor PVTA<br />

Num circuito digital, ocorre uma falha quan<strong>do</strong> um sinal que se propaga no caminho crítico não o<br />

consegue percorrer num tempo inferior ao perío<strong>do</strong> <strong>de</strong> relógio. Sen<strong>do</strong> este o problema que se<br />

preten<strong>de</strong> evitar, o funcionamento <strong>do</strong> sensor foi projecta<strong>do</strong> <strong>para</strong> <strong>de</strong>tectar esta situação. Deste mo<strong>do</strong>, o<br />

sensor me<strong>de</strong> o <strong>de</strong>sempenho <strong>do</strong> circuito, emulan<strong>do</strong> o atraso <strong>do</strong> caminho crítico, recorren<strong>do</strong> a um<br />

circuito composto por uma ca<strong>de</strong>ia <strong>de</strong> atraso construída com portas NOR ligadas sequencialmente<br />

(circuito réplica). O motivo pelo qual são utilizadas portas NOR <strong>de</strong>ve-se ao facto <strong>de</strong> estas<br />

envelhecerem mais rapidamente <strong>do</strong> que as restantes portas lógicas. Esta característica garante que<br />

o tempo <strong>de</strong> propagação no sensor será sempre superior ao <strong>do</strong>s potenciais caminhos críticos que<br />

possam surgir <strong>de</strong>vi<strong>do</strong> ao envelhecimento a longo prazo. Publicações anteriores mostram que pelo<br />

facto <strong>do</strong> NBTI ser mais significativo nos transístores PMOS, a <strong>de</strong>gradação <strong>do</strong> tempo <strong>de</strong> atraso é mais<br />

relevante nas transições <strong>do</strong> ‘0’ <strong>para</strong> o ’1’ lógico e que o efeito cascata verifica<strong>do</strong> nos transístores<br />

PMOS das portas NOR contribui fortemente <strong>para</strong> o aumento <strong>do</strong> tempo <strong>de</strong> atraso da porta lógica com<br />

o seu envelhecimento a longo prazo [13] [14].<br />

No entanto, como foi referi<strong>do</strong> anteriormente, a activida<strong>de</strong> lógica origina regeneração e <strong>para</strong><br />

garantir o pior cenário <strong>de</strong> envelhecimento no circuito réplica foi necessário impor <strong>do</strong>is mo<strong>do</strong>s <strong>de</strong><br />

funcionamento ao sensor. Assim, no intervalo que <strong>de</strong>corre entre as verificações <strong>de</strong> <strong>de</strong>sempenho, o<br />

sensor passa ao Mo<strong>do</strong> <strong>de</strong> Envelhecimento (Aging Mo<strong>de</strong>), e no momento da verificação, o sensor<br />

passa ao Mo<strong>do</strong> <strong>de</strong> Teste (Test Mo<strong>de</strong>).<br />

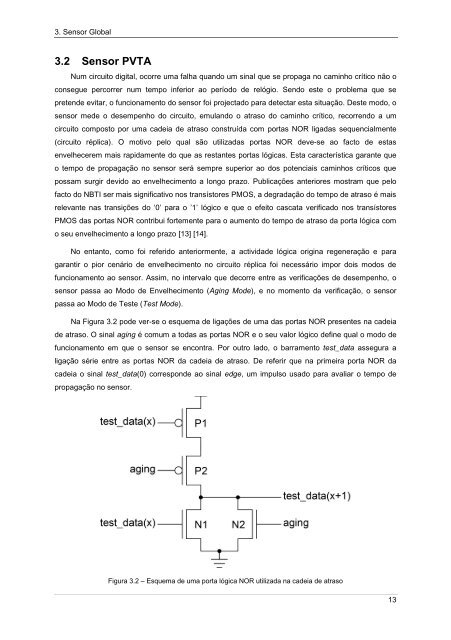

Na Figura 3.2 po<strong>de</strong> ver-se o esquema <strong>de</strong> ligações <strong>de</strong> uma das portas NOR presentes na ca<strong>de</strong>ia<br />

<strong>de</strong> atraso. O sinal aging é comum a todas as portas NOR e o seu valor lógico <strong>de</strong>fine qual o mo<strong>do</strong> <strong>de</strong><br />

funcionamento em que o sensor se encontra. Por outro la<strong>do</strong>, o barramento test_data assegura a<br />

ligação série entre as portas NOR da ca<strong>de</strong>ia <strong>de</strong> atraso. De referir que na primeira porta NOR da<br />

ca<strong>de</strong>ia o sinal test_data(0) correspon<strong>de</strong> ao sinal edge, um impulso usa<strong>do</strong> <strong>para</strong> avaliar o tempo <strong>de</strong><br />

propagação no sensor.<br />

Figura 3.2 – Esquema <strong>de</strong> uma porta lógica NOR utilizada na ca<strong>de</strong>ia <strong>de</strong> atraso<br />

13