Dynamic Voltage Scaling Dissertação para obtenção do Grau de ...

Dynamic Voltage Scaling Dissertação para obtenção do Grau de ...

Dynamic Voltage Scaling Dissertação para obtenção do Grau de ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

<strong>Dynamic</strong> <strong>Voltage</strong> <strong>Scaling</strong><br />

(Optimização da Tensão <strong>de</strong> Alimentação)<br />

Pedro Luís Neves<br />

<strong>Dissertação</strong> <strong>para</strong> <strong>obtenção</strong> <strong>do</strong> <strong>Grau</strong> <strong>de</strong> Mestre em<br />

Engenharia Electrotécnica e <strong>de</strong> Computa<strong>do</strong>res<br />

Júri<br />

Presi<strong>de</strong>nte: Doutor Nuno Cavaco Gomes Horta<br />

Orienta<strong>do</strong>r: Doutor Marcelino Bicho <strong>do</strong>s Santos<br />

Vogais: Doutor Jorge Filipe Leal Costa Semião<br />

Outubro <strong>de</strong> 2012

“The only limits we have are the limits we believe.”<br />

(Os únicos limites que temos são aqueles em que acreditamos.)<br />

Dr. Wayne W. Dyer

Agra<strong>de</strong>cimentos<br />

Estudar no IST tem si<strong>do</strong> uma experiência muito gratificante.<br />

Para além <strong>do</strong> meu reconhecimento a to<strong>do</strong>s os que <strong>de</strong>forma directa ou indirecta contribuíram<br />

<strong>para</strong> o meu percurso académico e <strong>para</strong> a minha felicida<strong>de</strong>, gostaria <strong>de</strong> agra<strong>de</strong>cer em particular:<br />

Aos meus pais por toda a <strong>de</strong>dicação e amor que sempre <strong>de</strong>monstraram, mas também to<strong>do</strong>s os<br />

sacrifícios realiza<strong>do</strong>s <strong>para</strong> que eu pu<strong>de</strong>sse concluir os meus estu<strong>do</strong>s.<br />

Aos restantes elementos da minha família, irmã, padrinhos, tios, primos e avós, os bons<br />

momentos proporciona<strong>do</strong>s, com um especial obriga<strong>do</strong> ao tio Henrique que <strong>de</strong> um mo<strong>do</strong> muito próprio<br />

<strong>de</strong>u o seu contributo <strong>para</strong> a minha formação pessoal.<br />

Ao gran<strong>de</strong> amigo Nuno Órfão por estar sempre presente nos bons e maus momentos.<br />

Aos companheiros e amigos <strong>de</strong> faculda<strong>de</strong> agra<strong>de</strong>ço o companheirismo e entreajuda.<br />

Aos colegas <strong>de</strong> laboratório Tiago Moita e Ruben Cabral, os ensinamentos, a ajuda, a amiza<strong>de</strong> e<br />

a boa disposição <strong>de</strong>monstradas durante o tempo em que trabalhamos juntos.<br />

Ao professor Jorge Semião e ao Bruno Jacinto, a disponibilida<strong>de</strong> <strong>para</strong> discussões sobre os<br />

assuntos aborda<strong>do</strong>s neste trabalho.<br />

Ao professor Marcelino Bicho <strong>do</strong>s Santos, a oportunida<strong>de</strong> e as condições <strong>de</strong> excelência que me<br />

proporcionou <strong>para</strong> a realização <strong>de</strong>ste trabalho.<br />

A toda a equipa da SILICONGATE LDA pelo acolhimento excepcional e em especial ao<br />

Floriberto Lima pelos bons ensinamentos e prontidão <strong>para</strong> fornecer as melhores condições <strong>para</strong> a<br />

realização <strong>de</strong>ste trabalhar.<br />

Por fim um pedi<strong>do</strong> <strong>de</strong> <strong>de</strong>sculpa às pessoas a quem prestei menos atenção <strong>de</strong>vi<strong>do</strong> às obrigações<br />

académicas, em especial ao afilha<strong>do</strong> João Pedro pela impossibilida<strong>de</strong> <strong>de</strong> aproveitar o pouco tempo<br />

disponível <strong>para</strong> estar com ele.<br />

i

Resumo<br />

Nesta dissertação é apresentada uma nova meto<strong>do</strong>logia que permite melhorar a eficiência <strong>do</strong>s<br />

circuitos digitais em microelectrónica, sem comprometer o <strong>de</strong>sempenho e fiabilida<strong>de</strong> <strong>do</strong> sistema.<br />

Actualmente a estratégia da indústria resi<strong>de</strong> em fixar a tensão <strong>de</strong> alimentação num patamar<br />

suficientemente alto que garanta o funcionamento <strong>do</strong> circuito <strong>para</strong> quaisquer variações no processo<br />

<strong>de</strong> fabrico, temperatura e envelhecimento (PVTA – Process+<strong>Voltage</strong>+Temperature+Aging). No<br />

entanto esta abordagem traduz-se num eleva<strong>do</strong> dispêndio <strong>de</strong> energia uma vez que por norma os<br />

circuitos não funcionam nas piores condições. Contu<strong>do</strong>, contornar a abordagem actual não é um<br />

problema trivial. É necessário que o sistema consiga adaptar-se às diferentes condições sem<br />

comprometer o <strong>de</strong>sempenho e a fiabilida<strong>de</strong>. Com o objectivo <strong>de</strong> obter a eficiência máxima, foi<br />

<strong>de</strong>senvolvi<strong>do</strong> um sensor que permite monitorizar a <strong>de</strong>gradação no <strong>de</strong>sempenho <strong>do</strong>s circuitos por<br />

forma a ajustar a tensão <strong>de</strong> alimentação às suas necessida<strong>de</strong>s. Para comprovar o seu<br />

funcionamento foi cria<strong>do</strong> um <strong>de</strong>monstra<strong>do</strong>r em FPGA conten<strong>do</strong> um multiplica<strong>do</strong>r com autoteste (BIST<br />

– Built-In Self-Test), on<strong>de</strong> foi aplica<strong>do</strong> o sensor <strong>de</strong>senvolvi<strong>do</strong> a fim <strong>de</strong> <strong>de</strong>monstrar a sua operação<br />

sem erros e com um consumo <strong>de</strong> energia optimiza<strong>do</strong>.<br />

Palavras Chave<br />

Sensor PVTA, FPGA, Prototipagem, Gestão <strong>de</strong> Energia em Microelectrónica<br />

iii

Abstract<br />

The present work reports a new metho<strong>do</strong>logy to improve the power efficiency of microelectronics<br />

digital cores, without compromising their performance or reliability. Nowadays, the industry most<br />

common strategy to support variations of the circuit fabrication Process, power supply <strong>Voltage</strong>,<br />

Temperature and Aging (PVTA) is based on imposing a custom voltage high enough to ensure the<br />

correct operation of the circuit in a worst case scenario. However, this approach leads to a<br />

consi<strong>de</strong>rable waste of energy since most of the time circuits <strong>do</strong> not operate un<strong>de</strong>r worst case<br />

conditions.<br />

Nevertheless, the solution for this problem is not trivial since it is mandatory to <strong>de</strong>velop a<br />

metho<strong>do</strong>logy were the system is able to adapt itself to different conditions but without compromising<br />

its performance or reliability.<br />

In this context, a new metho<strong>do</strong>logy is here proposed that aims to guarantee maximum efficiency<br />

through the use of a sensor that monitors the performance <strong>de</strong>gradation of circuits in or<strong>de</strong>r to adjust its<br />

power supply voltage, guaranteeing the best power consumption but without compromising its<br />

performance or reliability. To <strong>de</strong>monstrate the sensor operation, a prototype circuit was <strong>de</strong>veloped<br />

and implemented in a FPGA. The <strong>de</strong>veloped prototype inclu<strong>de</strong>s a multiplier, and corresponding self-<br />

-test (BIST), to which the <strong>de</strong>veloped sensor was applied in or<strong>de</strong>r to ensure its operation without<br />

errors, guaranteeing at the same time minimal power consumption.<br />

Keywords<br />

PVTA Sensor, FPGA, Prototyping, Power Management for Microelectronics<br />

v

Conteú<strong>do</strong><br />

Agra<strong>de</strong>cimentos ....................................................................................................................................... i<br />

Resumo .................................................................................................................................................. iii<br />

Abstract ................................................................................................................................................... v<br />

Conteú<strong>do</strong> ............................................................................................................................................... vii<br />

Lista <strong>de</strong> Figuras ...................................................................................................................................... ix<br />

Lista <strong>de</strong> Tabelas ..................................................................................................................................... xi<br />

Lista <strong>de</strong> Acrónimos ................................................................................................................................ xiii<br />

Introdução ....................................................................................................................................... 1<br />

1.1 Motivação ................................................................................................................................ 2<br />

1.2 Principais Contribuições .......................................................................................................... 4<br />

1.3 Objectivos ................................................................................................................................ 5<br />

1.4 Organização da <strong>Dissertação</strong> ................................................................................................... 5<br />

Análise e Previsão <strong>do</strong> Envelhecimento ........................................................................................... 7<br />

2.1 Envelhecimento e Efeito NBTI ................................................................................................ 8<br />

2.2 Ring Oscillator Sensor (IBM ® )................................................................................................. 9<br />

2.3 Sensor <strong>de</strong> envelhecimento da Sun Microsystems ® .............................................................. 10<br />

Sensor Global................................................................................................................................ 11<br />

3.1 Introdução ............................................................................................................................. 12<br />

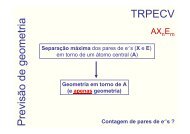

3.2 Sensor PVTA......................................................................................................................... 13<br />

3.2.1 Mo<strong>do</strong> <strong>de</strong> Envelhecimento .................................................................................................. 14<br />

3.2.2 Mo<strong>do</strong> <strong>de</strong> Teste .................................................................................................................. 15<br />

3.2.3 Detecção ........................................................................................................................... 15<br />

3.2.4 Implementação Prática ..................................................................................................... 17<br />

3.3 Temporiza<strong>do</strong>r ........................................................................................................................ 20<br />

3.3.1 Divisor <strong>de</strong> Relógio ............................................................................................................. 20<br />

3.3.2 Máquina <strong>de</strong> Esta<strong>do</strong>s ......................................................................................................... 22<br />

3.3.3 Diagrama <strong>de</strong> Esta<strong>do</strong>s ........................................................................................................ 24<br />

Demonstra<strong>do</strong>r FPGA ..................................................................................................................... 27<br />

4.1 Introdução ............................................................................................................................. 28<br />

4.2 Arquitectura ........................................................................................................................... 28<br />

vii

Conteú<strong>do</strong><br />

4.3 Meto<strong>do</strong>logia <strong>de</strong> Optimização ................................................................................................. 29<br />

4.3.1 Modificações Efectuadas .................................................................................................. 30<br />

4.3.2 Conversor DCDC .............................................................................................................. 30<br />

4.3.3 Comunicação SPI.............................................................................................................. 31<br />

4.3.4 Implementação <strong>do</strong> Sensor Global ..................................................................................... 33<br />

4.3.5 Multiplica<strong>do</strong>r Pipeline ........................................................................................................ 33<br />

4.4 Bloco <strong>de</strong> Controlo e Optimização.......................................................................................... 34<br />

4.4.1 Caminho <strong>de</strong> Da<strong>do</strong>s............................................................................................................ 35<br />

4.4.2 Comportamento................................................................................................................. 36<br />

4.4.3 Multiplexer tri-state (cut_speed)........................................................................................ 37<br />

Resulta<strong>do</strong>s Experimentais ............................................................................................................ 39<br />

5.1 Características <strong>do</strong> Demonstra<strong>do</strong>r ......................................................................................... 40<br />

5.2 Simulações Post-Route ......................................................................................................... 41<br />

5.3 Teste em Temperatura .......................................................................................................... 43<br />

Conclusões e Trabalho Futuro ...................................................................................................... 47<br />

6.1 Conclusões ............................................................................................................................ 48<br />

6.2 Trabalho Futuro ..................................................................................................................... 48<br />

Bibliografia............................................................................................................................................. 49<br />

Anexos .......................................................................................................................................... 51<br />

viii

Lista <strong>de</strong> Figuras<br />

Figura 1.1 – Distribuição da variação <strong>do</strong> <strong>de</strong>sempenho típica no processo <strong>de</strong> fabrico <strong>de</strong><br />

semicondutores ....................................................................................................................................... 3<br />

Figura 1.2 – Meto<strong>do</strong>logia actualmente utilizada nos microprocessa<strong>do</strong>res <strong>para</strong> ajuste <strong>de</strong> tensão ......... 3<br />

Figura 2.1 – Difusão <strong>do</strong> Hidrogénio em direcção à poly durante a fase <strong>de</strong> stress ................................. 8<br />

Figura 2.2 – Degradação no V th <strong>de</strong> um transístor PMOS após 50% <strong>do</strong> tempo na fase <strong>de</strong> stress e<br />

recuperação ............................................................................................................................................ 9<br />

Figura 2.3 – Meto<strong>do</strong>logia <strong>do</strong> sensor PVTA da IBM ® ............................................................................. 10<br />

Figura 2.4 – Sensor <strong>de</strong> Envelhecimento da Sun Microsystems ® ......................................................... 10<br />

Figura 3.1 – Diagrama simplifica<strong>do</strong> <strong>do</strong> Sensor Global ......................................................................... 12<br />

Figura 3.2 – Esquema <strong>de</strong> uma porta lógica NOR utilizada na ca<strong>de</strong>ia <strong>de</strong> atraso .................................. 13<br />

Figura 3.3 – Esta<strong>do</strong> <strong>do</strong>s transístores das portas NOR no Mo<strong>do</strong> <strong>de</strong> Envelhecimento .......................... 14<br />

Figura 3.4 – Esta<strong>do</strong> <strong>do</strong>s transístores das portas NOR no Mo<strong>do</strong> <strong>de</strong> Teste ........................................... 15<br />

Figura 3.5 – Esquema <strong>de</strong>talha<strong>do</strong> <strong>do</strong> Sensor PVTA .............................................................................. 16<br />

Figura 3.6 – Diagrama temporal comportamental <strong>do</strong>s principais sinais <strong>do</strong> Sensor Global .................. 16<br />

Figura 3.7 – Atraso da porta NOR <strong>para</strong> diferentes tensões <strong>de</strong> alimentação ........................................ 18<br />

Figura 3.8 - Atraso da porta NOR <strong>para</strong> diferentes temperaturas.......................................................... 18<br />

Figura 3.9 – Exemplo <strong>de</strong> optimização no Sensor PVTA ....................................................................... 19<br />

Figura 3.10 – Princípio <strong>de</strong> funcionamento <strong>do</strong> conta<strong>do</strong>r assíncrono ..................................................... 20<br />

Figura 3.11 – Esquema lógico e diagrama temporal <strong>de</strong> um Ripple Counter crescente <strong>de</strong> 4 bits ........ 21<br />

Figura 3.12 – Divisor <strong>de</strong> relógio implementa<strong>do</strong> .................................................................................... 22<br />

Figura 3.13 – Módulo assíncrono da máquina <strong>de</strong> esta<strong>do</strong>s ................................................................... 23<br />

Figura 3.14 – Módulo síncrono da máquina <strong>de</strong> esta<strong>do</strong>s ....................................................................... 23<br />

Figura 3.15 – Diagrama <strong>de</strong> esta<strong>do</strong>s <strong>do</strong> Temporiza<strong>do</strong>r ......................................................................... 24<br />

Figura 3.16 – Diagrama temporal comportamental <strong>do</strong>s sinais da máquina <strong>de</strong> esta<strong>do</strong>s ...................... 25<br />

Figura 4.1 – Arquitectura <strong>de</strong> funcionamento <strong>do</strong> <strong>de</strong>monstra<strong>do</strong>r ............................................................ 28<br />

Figura 4.2 – Fluxograma da estratégia Global <strong>de</strong> Controlo .................................................................. 29<br />

Figura 4.3 – Verso da placa <strong>de</strong> circuito impresso da FPGA indican<strong>do</strong> o LDO a remover ................... 30<br />

Figura 4.4 – Conversor DCDC programável por SPI ............................................................................ 31<br />

ix

Lista <strong>de</strong> Figuras<br />

Figura 4.5 – Vista <strong>de</strong> topo da placa <strong>de</strong> circuito impresso da FPGA indican<strong>do</strong> o LDO <strong>do</strong>s 3,3V .......... 31<br />

Figura 4.6 – Exemplo da implementação SPI....................................................................................... 32<br />

Figura 4.7 – Diagrama <strong>de</strong> esta<strong>do</strong>s <strong>do</strong> bloco <strong>de</strong> Controlo e Optimização ............................................. 34<br />

Figura 4.8 – Caminho <strong>de</strong> da<strong>do</strong>s necessário <strong>para</strong> o funcionamento <strong>do</strong> controlo .................................. 35<br />

Figura 4.9 – Multiplexer tri-state <strong>para</strong> geração <strong>do</strong> sinal cut_speed ...................................................... 37<br />

Figura 5.1 – Fotografia <strong>do</strong> protótipo final .............................................................................................. 40<br />

Figura 5.2 – Diagrama temporal <strong>do</strong> bloco Temporiza<strong>do</strong>r ..................................................................... 41<br />

Figura 5.3 – Diagrama temporal <strong>do</strong> bloco SPI ...................................................................................... 41<br />

Figura 5.4 – Diagrama temporal <strong>do</strong> Sensor PVTA ............................................................................... 42<br />

Figura 5.5 – Gráfico da variação da tensão <strong>de</strong> alimentação <strong>do</strong> núcleo digital da FPGA com a<br />

temperatura ........................................................................................................................................... 44<br />

Figura 5.6 – Gráfico da variação da corrente consumida pelo núcleo digital da FPGA com a<br />

temperatura ........................................................................................................................................... 45<br />

Figura 5.7 – Gráfico da variação da Potência consumida pelo núcleo digital da FPGA com a<br />

temperatura ........................................................................................................................................... 45<br />

Figura 5.8 – Poupança obtida com a utilização <strong>do</strong> Sensor Global <strong>para</strong> diferentes temperaturas ....... 46<br />

Figura 7.1 – Esquema eléctrico <strong>do</strong>s dispositivos <strong>de</strong> alimentação da placa FGPA utilizada ................ 52<br />

x

Lista <strong>de</strong> Tabelas<br />

Tabela 3.1 – Dimensão <strong>do</strong>s transístores PMOS e NMOS utiliza<strong>do</strong>s <strong>para</strong> simular o atraso da porta<br />

NOR ...................................................................................................................................................... 17<br />

Tabela 4.1 – Tabela com as tensões <strong>de</strong> saída <strong>do</strong> DCDC <strong>para</strong> cada palavra <strong>de</strong> configuração ............ 32<br />

Tabela 5.1 – Atributos da FPGA ........................................................................................................... 40<br />

Tabela 5.2 – Medições em Temperatura .............................................................................................. 43<br />

xi

Lista <strong>de</strong> Tabelas<br />

xii

Lista <strong>de</strong> Acrónimos<br />

ASIC<br />

Application-specific integrated circuit (Circuito integra<strong>do</strong> <strong>de</strong> aplicação especifica)<br />

BIST<br />

Built-in self-test (Autoteste embuti<strong>do</strong>)<br />

BTI<br />

Bias Temperature Instability (Instabilida<strong>de</strong> em temperatura e polarização)<br />

CUT<br />

Circuit Un<strong>de</strong>r Test (Circuito em teste)<br />

DVS<br />

<strong>Dynamic</strong> <strong>Voltage</strong> <strong>Scaling</strong> (Optimização da Tensão <strong>de</strong> Alimentação)<br />

FPGA<br />

Field-programmable gate array (Arranjo <strong>de</strong> Portas Programável em Campo)<br />

I2C<br />

Inter-Integrated Circuit (Circuito Inter-integra<strong>do</strong> - barramento série multi-mestre)<br />

ISM<br />

Internal Supply Module (Modulo <strong>de</strong> fornecimento interno)<br />

JTAG<br />

Joint Test Action Group (Grupo <strong>de</strong> Teste <strong>de</strong> Ação Conjunta)<br />

LDO<br />

Low-dropout voltage regulator (regula<strong>do</strong>r <strong>de</strong> tensão com baixa queda <strong>de</strong> tensão)<br />

LUT<br />

Look-Up Table (Tabela <strong>de</strong> referêcia)<br />

MISO<br />

Master Input, Slave Output (Entrada <strong>do</strong> Mestre, Saída <strong>do</strong> Escravo)<br />

MOSI<br />

Master Output, Slave Input (Saída <strong>do</strong> Mestre, Entrada <strong>do</strong> Escravo)<br />

NBTI<br />

Negative Bias Temperature Instability (Instabilida<strong>de</strong> em temperatura e polarização<br />

negativa)<br />

xiii

Lista <strong>de</strong> Acrónimos<br />

PBTI<br />

Positive Bias Temperature Instability (Instabilida<strong>de</strong> em temperatura e polarização positiva)<br />

PMU<br />

Power Management Unit (Unida<strong>de</strong> <strong>de</strong> Gestão <strong>de</strong> Energia)<br />

PVT<br />

PVTA<br />

SoC<br />

Process, power supply <strong>Voltage</strong> and Temperature (Processo <strong>de</strong> fabrico, tensão <strong>de</strong><br />

alimentação e temperatura)<br />

Process, power supply <strong>Voltage</strong>, Temperature and Aging (Processo <strong>de</strong> fabrico, tensão <strong>de</strong><br />

alimentação, temperatura e envelhecimento)<br />

System-on-Chip (sistema-em-um-chip)<br />

SPI<br />

Serial Peripheral Interface (Interface periférica <strong>de</strong> comunicação série)<br />

VHDL<br />

VHSIC Hardware Description Language (Linguagem <strong>de</strong> <strong>de</strong>scrição <strong>de</strong> hardware VHSIC)<br />

VHSIC<br />

Very High Speed Integrated Circuits (Circuito integra<strong>do</strong> <strong>de</strong> muito alta velocida<strong>de</strong>)<br />

xiv

Introdução<br />

Conteú<strong>do</strong><br />

1.1 Motivação . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2 .<br />

1.2 Principais Contribuições . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 .<br />

1.3 Objectivos . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 .<br />

1.4 Organização da <strong>Dissertação</strong> . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 .<br />

1

1. Introdução<br />

1.1 Motivação<br />

Num mun<strong>do</strong> em que a mobilida<strong>de</strong> tem ganho cada vez mais importância, to<strong>do</strong> o tipo <strong>de</strong><br />

dispositivos portáteis tem si<strong>do</strong> cria<strong>do</strong> <strong>para</strong> satisfazer as necessida<strong>de</strong>s <strong>de</strong> comunicação e<br />

entretenimento. No entanto, as baterias actualmente utilizadas por esses dispositivos têm si<strong>do</strong> o elo<br />

mais fraco na conjugação entre a autonomia e o volume ocupa<strong>do</strong> pelas mesmas. Por outro la<strong>do</strong>, as<br />

preocupações ambientais têm instiga<strong>do</strong> um maior cuida<strong>do</strong> com a eficiência <strong>do</strong>s equipamentos<br />

electrónicos, com o objectivo <strong>de</strong> reduzir os gastos com a energia.<br />

Em tecnologia CMOS, gran<strong>de</strong> parte da energia é consumida no perío<strong>do</strong> <strong>de</strong> comutação <strong>do</strong>s<br />

transístores. A expressão que traduz a potência dissipada por essas comutações é dada pela<br />

expressão (1.1):<br />

P sw = CfV 2 (1.1)<br />

on<strong>de</strong> C representa a capacida<strong>de</strong> média <strong>do</strong>s nós que mudam <strong>de</strong> esta<strong>do</strong>, f é a frequência <strong>de</strong> relógio<br />

<strong>do</strong> circuito e V é a tensão com que é alimenta<strong>do</strong> o núcleo digital.<br />

Esta expressão não é exacta, na medida em que a activida<strong>de</strong> média <strong>do</strong> circuito não é constante<br />

durante a sua operação, mas <strong>de</strong>ixa antever uma <strong>de</strong>pendência quadrática <strong>do</strong> consumo relativamente<br />

à tensão <strong>de</strong> alimentação. Para além das perdas <strong>de</strong> comutação existe também uma corrente <strong>de</strong> fuga<br />

estática nos transístores (subthreshold leakage) que é agravada com a miniaturização <strong>do</strong>s circuitos.<br />

Esta corrente <strong>de</strong> fuga começa a ser preocupante <strong>para</strong> tecnologias abaixo <strong>do</strong>s 90nm e o acréscimo <strong>de</strong><br />

potência <strong>de</strong> perdas é da<strong>do</strong> pela expressão (1.2):<br />

P leak = VI leak<br />

(1.2)<br />

on<strong>de</strong> V é a tensão <strong>de</strong> alimentação e I leak é o somatório da corrente <strong>de</strong> fuga nos transístores.<br />

Outra causa <strong>para</strong> a reduzida optimização no consumo <strong>do</strong>s semicondutores são as variações no<br />

processo <strong>de</strong> fabrico que, <strong>de</strong>vi<strong>do</strong> à sua natureza incerta, obrigam a que a tensão <strong>de</strong> alimentação<br />

atribuída a um da<strong>do</strong> microprocessa<strong>do</strong>r seja suficientemente alta <strong>para</strong> permitir a correcta operação <strong>de</strong><br />

to<strong>do</strong>s os chips fabrica<strong>do</strong>s. Na Figura 1.1 é apresenta<strong>do</strong> um exemplo típico da relação entre a<br />

quantida<strong>de</strong> <strong>de</strong> chips com <strong>de</strong>sempenhos acima e abaixo da média com<strong>para</strong>tivamente com a tensão<br />

necessária ao seu correcto funcionamento.<br />

2

1. Introdução<br />

Figura 1.1 – Distribuição da variação <strong>do</strong> <strong>de</strong>sempenho típica no processo <strong>de</strong> fabrico <strong>de</strong> semicondutores<br />

Estas condições têm dificulta<strong>do</strong> a tarefa <strong>de</strong> encontrar mecanismos que consigam optimizar o<br />

consumo <strong>do</strong>s dispositivos durante o seu tempo <strong>de</strong> utilização. Não só as incertezas no processo <strong>de</strong><br />

fabrico, mas também a <strong>de</strong>gradação <strong>do</strong> seu <strong>de</strong>sempenho <strong>de</strong>vida ao envelhecimento <strong>do</strong>s transístores,<br />

têm si<strong>do</strong> as principais barreiras na hora <strong>de</strong> optimizar a tensão <strong>de</strong> alimentação <strong>do</strong>s circuitos.<br />

Actualmente, a estratégia mais utilizada em microprocessa<strong>do</strong>res passa por tabelar a tensão <strong>de</strong><br />

alimentação <strong>para</strong> diferentes frequências <strong>de</strong> trabalho, reduzin<strong>do</strong> o consumo quan<strong>do</strong> existe menor<br />

activida<strong>de</strong> computacional (Figura 1.2). No entanto, quan<strong>do</strong> o processa<strong>do</strong>r passa à plena carga, a<br />

tensão <strong>de</strong> alimentação e a frequência passam <strong>para</strong> o valor máximo, <strong>de</strong>ixan<strong>do</strong> <strong>de</strong> haver qualquer<br />

benefício <strong>para</strong> o consumo. Exemplos <strong>de</strong>sta abordagem são as tecnologias SpeedStep ® da Intel ® [1] e<br />

PowerNow! da AMD [2].<br />

Figura 1.2 – Meto<strong>do</strong>logia actualmente utilizada nos microprocessa<strong>do</strong>res <strong>para</strong> ajuste <strong>de</strong> tensão<br />

3

1. Introdução<br />

Apesar <strong>de</strong> não disponível comercialmente, existe ainda o sistema Razor da ARM ® [3] que<br />

permite ajustar a tensão <strong>de</strong> alimentação com base na quantida<strong>de</strong> <strong>de</strong> falhas ocorridas durante a<br />

execução <strong>de</strong> tarefas. A correcta operação <strong>do</strong> circuito é assegurada por um mecanismo <strong>de</strong><br />

autocorrecção <strong>de</strong> erros basea<strong>do</strong> num mo<strong>de</strong>lo <strong>de</strong> amostragem dupla (uma com relógio rápi<strong>do</strong> e outra<br />

com relógio lento). Esta solução permite reduções elevadas no consumo, mas necessita que to<strong>do</strong>s<br />

os caminhos críticos sejam refeitos <strong>de</strong> mo<strong>do</strong> a integrar os dispositivos <strong>de</strong> <strong>de</strong>tecção e resolução <strong>de</strong><br />

falhas. No entanto, como esta abordagem interfere no normal fluxo <strong>de</strong> projecto, a sua a<strong>do</strong>pção por<br />

parte da indústria torna-se difícil.<br />

Depois <strong>de</strong>sta análise é possível concluir que se po<strong>de</strong>m obter gran<strong>de</strong>s ganhos <strong>de</strong> energia caso<br />

sejam reduzidas as margens <strong>de</strong> tensão atribuídas <strong>para</strong> compensar incertezas <strong>de</strong>vi<strong>do</strong> ao processo <strong>de</strong><br />

fabrico, temperatura <strong>de</strong> operação e envelhecimento.<br />

1.2 Principais Contribuições<br />

O sensor aqui apresenta<strong>do</strong> surge na sequência <strong>de</strong> estu<strong>do</strong>s sobre o impacto <strong>do</strong> envelhecimento<br />

nos transístores que mostram um aumento <strong>do</strong> tempo <strong>de</strong> propagação <strong>do</strong>s sinais digitais com o<br />

<strong>de</strong>correr <strong>do</strong> tempo. O fenómeno <strong>de</strong> envelhecimento afecta principalmente os transístores tipo P e o<br />

seu impacto nos circuitos digitais foi analisa<strong>do</strong> em [4].<br />

Com o objectivo <strong>de</strong> prever antecipadamente possíveis falhas nos circuitos digitais causadas por<br />

variações no processo <strong>de</strong> fabrico, temperatura e envelhecimento (PVTA), foi <strong>de</strong>senvolvi<strong>do</strong> um sensor<br />

local [5] que verifica junto <strong>do</strong>s principais caminhos críticos a eminência <strong>de</strong> uma falha ocorrer.<br />

Mais tar<strong>de</strong> foi <strong>de</strong>senvolvi<strong>do</strong> um segun<strong>do</strong> sensor [6] <strong>para</strong> avalizar o <strong>de</strong>sempenho global <strong>do</strong><br />

circuito em complemento com o sensor local.<br />

A principal contribuição <strong>de</strong>ste trabalho consiste no <strong>de</strong>senvolvimento <strong>de</strong> um <strong>de</strong>monstra<strong>do</strong>r em<br />

FPGA que coloca em prática uma parte <strong>do</strong> princípio proposto em [6]. Recorren<strong>do</strong> a um circuito com<br />

autoteste, é validada a solução proposta e são quantifica<strong>do</strong>s os ganhos obti<strong>do</strong>s no consumo<br />

energético quan<strong>do</strong> a tensão <strong>de</strong> alimentação é optimizada <strong>de</strong> forma permanente.<br />

4

1. Introdução<br />

1.3 Objectivos<br />

Esta dissertação tem como objectivo validar um processo que permite optimizar, <strong>de</strong> forma<br />

in<strong>de</strong>pen<strong>de</strong>nte (sem interferir no fluxo <strong>de</strong> projecto) e em tempo real, a tensão <strong>de</strong> alimentação nos<br />

circuitos digitais em microelectrónica. Para efectuar esta validação foi cria<strong>do</strong> um protótipo em FPGA<br />

que permitiu obter resulta<strong>do</strong>s experimentais. O sistema sensor e respectivo controlo não provocam<br />

um acréscimo <strong>de</strong> recursos físicos nem <strong>de</strong> consumo significativos quan<strong>do</strong> com<strong>para</strong><strong>do</strong> com o restante<br />

circuito.<br />

Para emular as condições reais <strong>de</strong> funcionamento foi integra<strong>do</strong> um multiplica<strong>do</strong>r com autoteste<br />

que indica qualquer falha que ocorra se o processamento for <strong>de</strong>masia<strong>do</strong> lento. Habilitan<strong>do</strong> e<br />

<strong>de</strong>sabilitan<strong>do</strong> este multiplica<strong>do</strong>r po<strong>de</strong>m ainda efectuar-se testes à fiabilida<strong>de</strong> <strong>do</strong> sensor durante<br />

transitórios <strong>de</strong> carga com diferentes temperaturas.<br />

1.4 Organização da <strong>Dissertação</strong><br />

<br />

<br />

<br />

<br />

<br />

Capitulo 2: Análise e Previsão <strong>do</strong> Envelhecimento – Neste capítulo é realizada uma<br />

análise ao efeito <strong>do</strong> envelhecimento nos transístores tipo P (NBTI) bem como apresentadas<br />

algumas das actuais estratégias <strong>de</strong> optimização <strong>de</strong> energia.<br />

Capitulo 3: Sensor Global – Neste capítulo é apresenta<strong>do</strong> o princípio <strong>de</strong> funcionamento <strong>do</strong><br />

sensor PVTA utiliza<strong>do</strong> na FPGA.<br />

Capitulo 4: Demonstra<strong>do</strong>r FPGA – Neste capítulo são apresenta<strong>do</strong>s os mecanismos<br />

necessários à realização <strong>do</strong> protótipo em FPGA: algoritmo <strong>de</strong> controlo global, modificações<br />

físicas e dispositivos utiliza<strong>do</strong>s.<br />

Capitulo 5: Resulta<strong>do</strong>s Experimentais – Neste capítulo são apresenta<strong>do</strong>s os resulta<strong>do</strong>s<br />

obti<strong>do</strong>s por simulação em Xilinx ® bem como os resulta<strong>do</strong>s práticos <strong>do</strong> funcionamento <strong>do</strong><br />

sensor <strong>para</strong> diferentes temperaturas.<br />

Capitulo 6: Conclusões e Trabalho Futuro – Neste capítulo são discuti<strong>do</strong>s os resulta<strong>do</strong>s<br />

face aos objectivos iniciais e aponta<strong>do</strong>s os objectivos futuros.<br />

5

1. Introdução<br />

6

Análise e Previsão <strong>do</strong><br />

Envelhecimento<br />

Conteú<strong>do</strong><br />

2.1 Envelhecimento e Efeito NBTI . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 .<br />

2.2 Ring Oscillator Sensor (IBM ® ) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 .<br />

2.3 Sensor <strong>de</strong> envelhecimento da Sun Microsystems ® . . . . . . . . . . . . 9 .<br />

7

2. Análise e Previsão <strong>do</strong> Envelhecimento<br />

2.1 Envelhecimento e Efeito NBTI<br />

Uma das consequências da operação a longo prazo <strong>do</strong>s circuitos digitais é a <strong>de</strong>gradação no<br />

<strong>de</strong>sempenho das portas lógicas <strong>de</strong>vi<strong>do</strong> ao envelhecimento. Esta diminuição <strong>do</strong> <strong>de</strong>sempenho é<br />

provocada pelo aumento da tensão <strong>de</strong> threshold (V th ) nos transístores, que leva à redução na<br />

corrente <strong>de</strong> dreno. O fenómeno <strong>de</strong> envelhecimento po<strong>de</strong> ocorrer tanto em transístores tipo N (PBTI)<br />

como em tipo P (NBTI), no entanto os seus efeitos têm maior relevância nos transístores tipo P [4].<br />

Neste trabalho não será consi<strong>de</strong>ra<strong>do</strong> o PBTI, mas <strong>para</strong> tecnologias inferiores a 40nm o seu efeito já<br />

<strong>de</strong>ve ser consi<strong>de</strong>ra<strong>do</strong> [6]. Frequentemente chegam a ocorrer erros no processamento digital <strong>de</strong>vi<strong>do</strong> a<br />

incumprimentos temporais causa<strong>do</strong>s pelo envelhecimento a longo prazo, sen<strong>do</strong> um <strong>do</strong>s principais<br />

factores que limitam a vida útil <strong>do</strong>s dispositivos.<br />

O fenómeno <strong>do</strong> NBTI surge <strong>de</strong>vi<strong>do</strong> a processos electroquímicos no seio <strong>do</strong>s transístores com o<br />

dióxi<strong>do</strong> <strong>de</strong> silício puro (SiO 2 ) [7]. Estas reacções ocorrem durante a permanência <strong>do</strong> transístor no<br />

esta<strong>do</strong> <strong>de</strong> condução (fase <strong>de</strong> stress com V GS = –V dd ), on<strong>de</strong> <strong>de</strong>vi<strong>do</strong> ao campo eléctrico e às altas<br />

temperaturas são quebradas as ligações químicas entre o silício (Si) e o hidrogénio (H) na zona <strong>de</strong><br />

junção <strong>do</strong> silício com o oxi<strong>do</strong>. O hidrogénio liberta<strong>do</strong> acaba por se <strong>de</strong>slocar em direcção à porta <strong>de</strong><br />

silício policristalino (poly), chegan<strong>do</strong> por vezes a recombinar-se em H 2 (Figura 2.1). Por outro la<strong>do</strong>, o<br />

silício quebra<strong>do</strong> junto ao óxi<strong>do</strong> (Si-) actua como uma armadilha <strong>para</strong> os porta<strong>do</strong>res <strong>do</strong> canal,<br />

reduzin<strong>do</strong> a mobilida<strong>de</strong> e aumentan<strong>do</strong> a tensão <strong>de</strong> limiar (threshold voltage, V th ) <strong>do</strong> transístor.<br />

Figura 2.1 – Difusão <strong>do</strong> Hidrogénio em direcção à poly durante a fase <strong>de</strong> stress<br />

Por outro la<strong>do</strong>, na passagem <strong>do</strong> transístor ao esta<strong>do</strong> <strong>de</strong> corte (fase <strong>de</strong> recuperação com V GS =<br />

0V), o processo é inverti<strong>do</strong> fazen<strong>do</strong> com que o hidrogénio se recombine <strong>de</strong> novo com o silício,<br />

fazen<strong>do</strong> diminuir a variação na tensão <strong>de</strong> limiar <strong>do</strong> transístor. No entanto, nem todas as ligações<br />

quebradas são restabelecidas. Isto provoca uma <strong>de</strong>gradação acumulada <strong>do</strong> V th no transístor, levan<strong>do</strong><br />

à progressiva <strong>de</strong>gradação <strong>do</strong> <strong>de</strong>sempenho das portas lógicas. A longo prazo, o aumento <strong>do</strong> V th fica<br />

<strong>de</strong>pen<strong>de</strong>nte da taxa <strong>de</strong> ruptura das ligações Si-H e <strong>de</strong> recombinações com Si-. Estas, por sua vez<br />

estão <strong>de</strong>pen<strong>de</strong>ntes da probabilida<strong>de</strong> <strong>do</strong> transístor estar na fase <strong>de</strong> stress ou recuperação e <strong>de</strong> outros<br />

parâmetros como a temperatura [8].<br />

8

2. Análise e Previsão <strong>do</strong> Envelhecimento<br />

Na Figura 2.2 é apresenta<strong>do</strong> um exemplo da variação <strong>de</strong> V th na situação <strong>de</strong> igual perío<strong>do</strong> <strong>de</strong><br />

tempo na fase <strong>de</strong> stress e na fase <strong>de</strong> recuperação. Po<strong>de</strong> ver-se que <strong>para</strong> tentar reaver o V th inicial é<br />

necessário um intervalo <strong>de</strong> tempo muito superior ao que foi necessário <strong>para</strong> a <strong>de</strong>gradação ocorrer.<br />

Figura 2.2 – Degradação no V th <strong>de</strong> um transístor PMOS após 50% <strong>do</strong> tempo na fase <strong>de</strong> stress e recuperação<br />

Mo<strong>de</strong>los <strong>de</strong> previsão, bem como resulta<strong>do</strong>s experimentais apontam <strong>para</strong> que o atraso causa<strong>do</strong><br />

pelo NBTI seja in<strong>de</strong>pen<strong>de</strong>nte da frequência, <strong>para</strong> frequências superiores a 100Hz [9] [10]. O maior<br />

problema surge quan<strong>do</strong> transístores num caminho quase crítico permanecem <strong>de</strong>masia<strong>do</strong> tempo na<br />

fase <strong>de</strong> stress, po<strong>de</strong>n<strong>do</strong> nestas circunstâncias, o envelhecimento transformar este caminho num<br />

caminho crítico.<br />

2.2 Ring Oscillator Sensor (IBM ® )<br />

A técnica utilizada pela IBM ® em [11] tira parti<strong>do</strong> <strong>do</strong> comportamento <strong>de</strong> um ou mais oscila<strong>do</strong>res<br />

em anel (ring oscillators) <strong>para</strong> obter uma frequência <strong>de</strong> relógio proporcional a qualquer variação<br />

PVTA (Figura 2.3). Em seguida o sinal <strong>de</strong> relógio obti<strong>do</strong> passa por um divisor <strong>de</strong> frequência e entra<br />

num conta<strong>do</strong>r. O número <strong>de</strong> oscilações registadas por intervalo <strong>de</strong> tempo é analisa<strong>do</strong> periodicamente<br />

por um bloco <strong>de</strong> controlo que intervirá no caso <strong>de</strong> falha iminente. Esta <strong>de</strong>tecção <strong>de</strong> falhas po<strong>de</strong> ser<br />

obtida <strong>de</strong> duas formas: (1) número <strong>de</strong> oscilações registadas ser inferior ao <strong>de</strong> calibração; (2) uma<br />

discrepância significativa entre leituras.<br />

9

2. Análise e Previsão <strong>do</strong> Envelhecimento<br />

Figura 2.3 – Meto<strong>do</strong>logia <strong>do</strong> sensor PVTA da IBM ®<br />

2.3 Sensor <strong>de</strong> envelhecimento da Sun Microsystems ®<br />

O sistema <strong>de</strong>senvolvi<strong>do</strong> pela antiga Sun Microsystems ® [12], adquirida pela Oracle<br />

Corporation ® , baseia-se na polarização <strong>de</strong> diferentes tensões a transístores tipo N e tipo P que irão<br />

alimentar um regula<strong>do</strong>r <strong>de</strong> tensão que por sua vez liga a um oscila<strong>do</strong>r controla<strong>do</strong> por tensão (VCO).<br />

Em seguida o circuito conta<strong>do</strong>r averigua o número <strong>de</strong> oscilações realizadas por intervalo <strong>de</strong> tempo e<br />

com<strong>para</strong>-as com uma referência. Devi<strong>do</strong> ao envelhecimento <strong>do</strong>s transístores coloca<strong>do</strong>s no sensor, a<br />

corrente fornecida ao regula<strong>do</strong>r <strong>de</strong> tensão <strong>do</strong> VCO é menor e por conseguinte o número <strong>de</strong><br />

oscilações contabilizadas diminui. O diagrama <strong>de</strong> funcionamento <strong>do</strong> sensor é apresenta<strong>do</strong> na Figura<br />

2.4, na qual se po<strong>de</strong> ver a existência <strong>de</strong> um multiplexer <strong>para</strong> escolher qual o sensor a avaliar, bem<br />

como <strong>de</strong> uma memória que guarda informações <strong>de</strong> calibração. Após o varrimento <strong>de</strong> to<strong>do</strong>s os<br />

sensores, a diferença verificada entre a contagem <strong>de</strong> calibração e a obtida na realida<strong>de</strong> é enviada a<br />

um sistema <strong>de</strong> controlo.<br />

Figura 2.4 – Sensor <strong>de</strong> Envelhecimento da Sun Microsystems ®<br />

10

Sensor Global<br />

Conteú<strong>do</strong><br />

3.1 Introdução . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 . .<br />

3.2 Sensor PVTA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 . .<br />

3.3 Temporiza<strong>do</strong>r . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20 . .<br />

11

3. Sensor Global<br />

3.1 Introdução<br />

Nesta secção é apresentada a arquitectura <strong>de</strong> um sensor <strong>para</strong> monitorização da <strong>de</strong>gradação <strong>do</strong><br />

<strong>de</strong>sempenho <strong>do</strong>s circuitos digitais resultante <strong>do</strong> envelhecimento a longo prazo. Esta arquitectura vem<br />

no seguimento <strong>de</strong> uma meto<strong>do</strong>logia recentemente <strong>de</strong>senvolvida pelo grupo <strong>de</strong> investigação <strong>do</strong><br />

INESC-ID no âmbito <strong>do</strong> qual este trabalho foi <strong>de</strong>senvolvi<strong>do</strong> e que foi apresentada em [6].<br />

A introdução <strong>de</strong>sta nova topologia <strong>de</strong> sensor surgiu da necessida<strong>de</strong> <strong>de</strong> contornar <strong>do</strong>is gran<strong>de</strong>s<br />

inconvenientes associa<strong>do</strong>s à utilização <strong>de</strong> sensores locais:<br />

<br />

<br />

A necessida<strong>de</strong> <strong>de</strong> suspen<strong>de</strong>r o funcionamento <strong>do</strong> circuito em monitorização no momento<br />

em que é realizada a medição <strong>do</strong> esta<strong>do</strong> <strong>de</strong> <strong>de</strong>gradação. Esta interrupção é tempo <strong>de</strong><br />

processamento <strong>de</strong>sperdiça<strong>do</strong> e rapidamente se po<strong>de</strong>ria chegar à situação em que o tempo<br />

em processamento seria da mesma or<strong>de</strong>m <strong>de</strong> gran<strong>de</strong>za <strong>do</strong> tempo <strong>de</strong> monitorização.<br />

A necessida<strong>de</strong> <strong>de</strong> substituir os flip-flops <strong>do</strong> caminho crítico por outros com a lógica <strong>de</strong><br />

<strong>de</strong>tecção <strong>de</strong> falhas integrada, o que obriga ao projecto e caracterização <strong>de</strong> células<br />

adicionais <strong>para</strong> cada biblioteca digital e interfere com o normal fluxo <strong>de</strong> projecto.<br />

Por outro la<strong>do</strong>, com a utilização <strong>do</strong> Sensor Global aqui apresenta<strong>do</strong>, é possível avaliar em<br />

tempo real a possibilida<strong>de</strong> <strong>de</strong> uma falha ocorrer, através da verificação periódica <strong>do</strong> <strong>de</strong>sempenho<br />

instantâneo <strong>do</strong> circuito em monitorização. Estas informações <strong>de</strong> <strong>de</strong>sempenho são enviadas <strong>para</strong> um<br />

dispositivo <strong>de</strong> Controlo Digital (apresenta<strong>do</strong> no capítulo 4) que faz subir a tensão <strong>de</strong> alimentação<br />

quan<strong>do</strong> o atraso na propagação das portas lógicas <strong>do</strong> sensor aumenta acima <strong>de</strong> um limiar pré-<br />

-<strong>de</strong>fini<strong>do</strong>, ou faz diminuir a tensão <strong>de</strong> alimentação se o <strong>de</strong>sempenho estiver acima <strong>do</strong> necessário.<br />

A implementação <strong>do</strong> Sensor Global é dividida em 2 blocos distintos (Figura 3.1). Um bloco <strong>de</strong><br />

controlo <strong>para</strong> gerar periodicamente os sinais necessários ao funcionamento <strong>do</strong> sensor e outro<br />

conten<strong>do</strong> os dispositivos que actuam como sensores a variações PVTA.<br />

Figura 3.1 – Diagrama simplifica<strong>do</strong> <strong>do</strong> Sensor Global<br />

12

3. Sensor Global<br />

3.2 Sensor PVTA<br />

Num circuito digital, ocorre uma falha quan<strong>do</strong> um sinal que se propaga no caminho crítico não o<br />

consegue percorrer num tempo inferior ao perío<strong>do</strong> <strong>de</strong> relógio. Sen<strong>do</strong> este o problema que se<br />

preten<strong>de</strong> evitar, o funcionamento <strong>do</strong> sensor foi projecta<strong>do</strong> <strong>para</strong> <strong>de</strong>tectar esta situação. Deste mo<strong>do</strong>, o<br />

sensor me<strong>de</strong> o <strong>de</strong>sempenho <strong>do</strong> circuito, emulan<strong>do</strong> o atraso <strong>do</strong> caminho crítico, recorren<strong>do</strong> a um<br />

circuito composto por uma ca<strong>de</strong>ia <strong>de</strong> atraso construída com portas NOR ligadas sequencialmente<br />

(circuito réplica). O motivo pelo qual são utilizadas portas NOR <strong>de</strong>ve-se ao facto <strong>de</strong> estas<br />

envelhecerem mais rapidamente <strong>do</strong> que as restantes portas lógicas. Esta característica garante que<br />

o tempo <strong>de</strong> propagação no sensor será sempre superior ao <strong>do</strong>s potenciais caminhos críticos que<br />

possam surgir <strong>de</strong>vi<strong>do</strong> ao envelhecimento a longo prazo. Publicações anteriores mostram que pelo<br />

facto <strong>do</strong> NBTI ser mais significativo nos transístores PMOS, a <strong>de</strong>gradação <strong>do</strong> tempo <strong>de</strong> atraso é mais<br />

relevante nas transições <strong>do</strong> ‘0’ <strong>para</strong> o ’1’ lógico e que o efeito cascata verifica<strong>do</strong> nos transístores<br />

PMOS das portas NOR contribui fortemente <strong>para</strong> o aumento <strong>do</strong> tempo <strong>de</strong> atraso da porta lógica com<br />

o seu envelhecimento a longo prazo [13] [14].<br />

No entanto, como foi referi<strong>do</strong> anteriormente, a activida<strong>de</strong> lógica origina regeneração e <strong>para</strong><br />

garantir o pior cenário <strong>de</strong> envelhecimento no circuito réplica foi necessário impor <strong>do</strong>is mo<strong>do</strong>s <strong>de</strong><br />

funcionamento ao sensor. Assim, no intervalo que <strong>de</strong>corre entre as verificações <strong>de</strong> <strong>de</strong>sempenho, o<br />

sensor passa ao Mo<strong>do</strong> <strong>de</strong> Envelhecimento (Aging Mo<strong>de</strong>), e no momento da verificação, o sensor<br />

passa ao Mo<strong>do</strong> <strong>de</strong> Teste (Test Mo<strong>de</strong>).<br />

Na Figura 3.2 po<strong>de</strong> ver-se o esquema <strong>de</strong> ligações <strong>de</strong> uma das portas NOR presentes na ca<strong>de</strong>ia<br />

<strong>de</strong> atraso. O sinal aging é comum a todas as portas NOR e o seu valor lógico <strong>de</strong>fine qual o mo<strong>do</strong> <strong>de</strong><br />

funcionamento em que o sensor se encontra. Por outro la<strong>do</strong>, o barramento test_data assegura a<br />

ligação série entre as portas NOR da ca<strong>de</strong>ia <strong>de</strong> atraso. De referir que na primeira porta NOR da<br />

ca<strong>de</strong>ia o sinal test_data(0) correspon<strong>de</strong> ao sinal edge, um impulso usa<strong>do</strong> <strong>para</strong> avaliar o tempo <strong>de</strong><br />

propagação no sensor.<br />

Figura 3.2 – Esquema <strong>de</strong> uma porta lógica NOR utilizada na ca<strong>de</strong>ia <strong>de</strong> atraso<br />

13

3. Sensor Global<br />

3.2.1 Mo<strong>do</strong> <strong>de</strong> Envelhecimento<br />

A entrada <strong>do</strong> sensor em Mo<strong>do</strong> <strong>de</strong> Envelhecimento ocorre quan<strong>do</strong> o sinal aging é força<strong>do</strong> a ‘1’<br />

pelo bloco Temporiza<strong>do</strong>r. Durante este mo<strong>do</strong> os sinais edge e clkgen permanecem inaltera<strong>do</strong>s no<br />

valor lógico ‘0’. Na Figura 3.3 po<strong>de</strong> ver-se que esta configuração provoca o bloqueio <strong>de</strong> V dd através<br />

<strong>de</strong> P2 ao mesmo tempo que força gnd na saída por meio <strong>de</strong> N2. Deste mo<strong>do</strong>, o sinal test_data<br />

propaga<strong>do</strong> a to<strong>do</strong>s os transístores P1 e N1 é ‘0’, o que força os transístores P1 a envelhecer (fase <strong>de</strong><br />

stress).<br />

Figura 3.3 – Esta<strong>do</strong> <strong>do</strong>s transístores das portas NOR no Mo<strong>do</strong> <strong>de</strong> Envelhecimento<br />

Isto permite concluir que a <strong>de</strong>gradação temporal por envelhecimento observada na ca<strong>de</strong>ia <strong>de</strong><br />

atraso será apenas da responsabilida<strong>de</strong> <strong>do</strong>s transístores P1, uma vez que os transístores P2 estão<br />

em mo<strong>do</strong> <strong>de</strong> recuperação quase to<strong>do</strong> o tempo. Por este motivo, e <strong>para</strong> o correcto funcionamento <strong>do</strong><br />

sensor, é importante que a or<strong>de</strong>m <strong>de</strong> ligação das entradas das portas NOR seja respeitada, uma vez<br />

que durante a fase <strong>de</strong> stress o fenómeno <strong>de</strong> envelhecimento só acontece nos transístores que estão<br />

situa<strong>do</strong>s junto à tensão <strong>de</strong> alimentação.<br />

14

3. Sensor Global<br />

3.2.2 Mo<strong>do</strong> <strong>de</strong> Teste<br />

A mudança <strong>para</strong> o Mo<strong>do</strong> <strong>de</strong> Teste ocorre quan<strong>do</strong> o sinal aging transita <strong>para</strong> ‘0’. Esta alteração<br />

coloca o transístor P2 em condução e o N2 ao corte, fazen<strong>do</strong> com que a saída fique <strong>de</strong>pen<strong>de</strong>nte <strong>do</strong><br />

sinal test_data coloca<strong>do</strong> na entrada. Na Figura 3.4 po<strong>de</strong> ver-se que a nova configuração das portas<br />

NOR reflecte o comportamento lógico <strong>de</strong> um inversor, permitin<strong>do</strong> agora a propagação <strong>de</strong> qualquer<br />

sinal que seja coloca<strong>do</strong> no início da ca<strong>de</strong>ia.<br />

Figura 3.4 – Esta<strong>do</strong> <strong>do</strong>s transístores das portas NOR no Mo<strong>do</strong> <strong>de</strong> Teste<br />

De referir que durante o perío<strong>do</strong> em que ocorre o teste, os transístores P1 passam algum <strong>do</strong><br />

tempo na fase <strong>de</strong> regeneração. No entanto, como o intervalo entre verificações consecutivas andará<br />

sempre acima das centenas <strong>de</strong> ciclos <strong>de</strong> relógio, a duração <strong>do</strong> teste não <strong>de</strong>ve impedir o sensor <strong>de</strong><br />

envelhecer mais <strong>do</strong> que o restante circuito.<br />

3.2.3 Detecção<br />

Uma vez activa a ca<strong>de</strong>ia, é necessário implementar um mecanismo capaz <strong>de</strong> medir<br />

quantitativamente o atraso provoca<strong>do</strong> pelo circuito réplica. A abordagem utilizada baseia-se no<br />

princípio sample-and-hold <strong>para</strong> registar o esta<strong>do</strong> das portas NOR num da<strong>do</strong> instante <strong>do</strong> teste,<br />

utilizan<strong>do</strong> <strong>para</strong> o efeito flip-flops tipo D coloca<strong>do</strong>s à saída das portas NOR. Ten<strong>do</strong> em conta que<br />

durante o teste as portas NOR têm o comportamento <strong>de</strong> inversores, po<strong>de</strong> obter-se uma leitura <strong>do</strong> tipo<br />

código termómetro extrain<strong>do</strong> <strong>de</strong> forma intercalar as saídas ̅ ou <strong>do</strong>s flip-flops. A utilização <strong>de</strong>ste<br />

formato justifica-se com a sua fácil <strong>obtenção</strong> e pelo facto <strong>de</strong> permitir ao projectista usar diferentes<br />

formas <strong>de</strong> manipular a informação <strong>do</strong> sensor com base no algoritmo <strong>de</strong> controlo.<br />

15

3. Sensor Global<br />

A Figura 3.5 mostra o esquema eléctrico final <strong>do</strong> Sensor PVTA. Face a versões anteriores, como<br />

a proposta por J. Semião et al. [6], a versão proposta nesta dissertação apresenta algumas<br />

alterações na forma como são registadas as saídas das portas NOR. On<strong>de</strong> anteriormente existia<br />

uma báscula (latch), um elemento <strong>de</strong> atraso e um <strong>de</strong>tector <strong>de</strong> estabilida<strong>de</strong> (L+DE+SC), existe agora<br />

apenas um flip-flop tipo D. Esta substituição visa tornar o sensor compatível com células digitais<br />

normalizadas ten<strong>do</strong> em conta que a meto<strong>do</strong>logia aqui apresentada não requer a utilização <strong>de</strong><br />

sensores locais.<br />

Figura 3.5 – Esquema <strong>de</strong>talha<strong>do</strong> <strong>do</strong> Sensor PVTA<br />

O mo<strong>do</strong> <strong>de</strong> teste po<strong>de</strong> ainda ser divi<strong>do</strong> em 3 submo<strong>do</strong>s (Figura 3.6):<br />

<br />

<br />

<br />

Inicialização – perío<strong>do</strong> <strong>de</strong> espera <strong>para</strong> permitir que a ca<strong>de</strong>ia <strong>de</strong> portas NOR estabilize após<br />

a transição <strong>para</strong> ‘0’ <strong>do</strong> sinal aging.<br />

Propagação – intervalo <strong>de</strong> tempo em que o sinal edge é propaga<strong>do</strong> na ca<strong>de</strong>ia <strong>de</strong> atraso.<br />

Captura – instante em que é efectuada a captura <strong>do</strong> esta<strong>do</strong> das portas NOR pelos flip-flops.<br />

Figura 3.6 – Diagrama temporal comportamental <strong>do</strong>s principais sinais <strong>do</strong> Sensor Global<br />

16

3. Sensor Global<br />

Os intervalos <strong>de</strong> tempo atribuí<strong>do</strong>s a cada submo<strong>do</strong> são basea<strong>do</strong>s na premissa <strong>de</strong> que após o<br />

perío<strong>do</strong> correspon<strong>de</strong>nte a 1 ciclo <strong>de</strong> relógio toda a lógica num circuito digital <strong>de</strong>verá estar<br />

estabilizada <strong>para</strong> não ocorrerem erros. Por esta razão a captura ocorre 1 ciclo <strong>de</strong> relógio após a<br />

propagação <strong>do</strong> impulso edge e é atribuí<strong>do</strong> 1 ciclo <strong>de</strong> relógio mais uma margem <strong>de</strong> meio perío<strong>do</strong> na<br />

inicialização <strong>de</strong> forma a garantir que a ca<strong>de</strong>ia se encontra estável mesmo quan<strong>do</strong> o circuito tem um<br />

comportamento <strong>de</strong>masia<strong>do</strong> lento.<br />

3.2.4 Implementação Prática<br />

Uma utilização posterior da informação <strong>do</strong> Sensor Global <strong>para</strong> optimização da tensão <strong>de</strong><br />

alimentação requer a calibração prévia <strong>do</strong> sensor. Esta calibração visa <strong>de</strong>terminar quantas portas<br />

NOR são necessárias <strong>para</strong> igualar o atraso <strong>do</strong> caminho crítico a vigiar mais uma margem <strong>de</strong><br />

segurança. Uma vez <strong>de</strong>terminada a calibração, esta <strong>de</strong>verá servir <strong>para</strong> to<strong>do</strong>s os chips <strong>de</strong> um mesmo<br />

circuito. As variações no processo <strong>de</strong> fabrico <strong>de</strong>verão ser compensadas automaticamente <strong>de</strong>vi<strong>do</strong> ao<br />

aumento ou diminuição no <strong>de</strong>sempenho. De forma genérica, o princípio e topologia <strong>do</strong> sensor não<br />

<strong>de</strong>pen<strong>de</strong>m <strong>do</strong> circuito a monitorizar, da frequência <strong>de</strong> relógio, nem da tecnologia em que está<br />

implementa<strong>do</strong>. No entanto a sua implementação vai <strong>de</strong>pen<strong>de</strong>r <strong>de</strong> caso <strong>para</strong> caso. Em particular, o<br />

número <strong>de</strong> portas lógicas utilizadas <strong>para</strong> representar o circuito réplica irá <strong>de</strong>pen<strong>de</strong>r da dimensão <strong>do</strong><br />

caminho crítico, bem como da tecnologia <strong>de</strong> fabrico.<br />

Com o objectivo <strong>de</strong> caracterizar o atraso gera<strong>do</strong> pela porta NOR foram efectuadas simulações<br />

em tecnologia TSMC 65nm. Estas simulações mostram a <strong>de</strong>pendência <strong>do</strong> atraso da porta NOR <strong>para</strong><br />

diferentes tensões <strong>de</strong> alimentação e diferentes temperaturas. Os resulta<strong>do</strong>s obti<strong>do</strong>s dizem respeito a<br />

simulações ao nível <strong>do</strong> esquema eléctrico realizadas com dispositivos cujas dimensões se<br />

apresentam na Tabela 3.1 e correspon<strong>de</strong>m à porta NOR padrão.<br />

Transístor W (nm) L (nm)<br />

P1, P2 460 80<br />

N1, N2 170 80<br />

Tabela 3.1 – Dimensão <strong>do</strong>s transístores PMOS e NMOS utiliza<strong>do</strong>s <strong>para</strong> simular o atraso da porta NOR<br />

Na Figura 3.7 é apresenta<strong>do</strong> o gráfico da variação no atraso da porta NOR com a tensão <strong>de</strong><br />

alimentação <strong>para</strong> três cenários diferentes. O caso típico correspon<strong>de</strong> à operação à temperatura<br />

ambiente (25ºC), no pior caso à temperatura <strong>de</strong> 125ºC e no melhor caso à temperatura <strong>de</strong> -40ºC.<br />

17

Atraso porta NOR (ps)<br />

Atraso porta NOR (ps)<br />

3. Sensor Global<br />

4.50E+01<br />

4.00E+01<br />

3.50E+01<br />

3.00E+01<br />

2.50E+01<br />

2.00E+01<br />

1.50E+01<br />

1.00E+01<br />

typical T = 25ºC<br />

schematic<br />

Worst T = 125ºC Corner<br />

Schematic<br />

Best T = Corner -40ºC<br />

Schematic<br />

5.00E+00<br />

0.00E+00<br />

1.05 1.15 1.25 1.35<br />

Tensão <strong>de</strong> Alimentação (V)<br />

Figura 3.7 – Atraso da porta NOR <strong>para</strong> diferentes tensões <strong>de</strong> alimentação<br />

Na Figura 3.8 é apresenta<strong>do</strong> o gráfico da variação no atraso da porta NOR com a temperatura e<br />

também <strong>para</strong> três cenários diferentes. O caso típico correspon<strong>de</strong> a operar com a tensão <strong>de</strong><br />

alimentação a 1,2V, no pior caso a 1,08V e no melhor caso a 1,32V.<br />

5.00E+01<br />

4.50E+01<br />

4.00E+01<br />

3.50E+01<br />

3.00E+01<br />

2.50E+01<br />

2.00E+01<br />

1.50E+01<br />

1.00E+01<br />

5.00E+00<br />

0.00E+00<br />

-60 -30 0 30 60 90 120 150 180<br />

Temperatura (°C)<br />

typical V dd = 1,2V<br />

schematic<br />

Worst V dd = Corner 1,08V<br />

Schematic<br />

Best V dd<br />

Corner = 1,32V<br />

Schematic<br />

Figura 3.8 - Atraso da porta NOR <strong>para</strong> diferentes temperaturas<br />

Das simulações efectuadas po<strong>de</strong> ver-se que o atraso na porta NOR aumenta significativamente<br />

com a diminuição da tensão <strong>de</strong> alimentação. Por este motivo <strong>de</strong>ve existir especial cuida<strong>do</strong> com as<br />

transições <strong>de</strong> tensão durante o processo <strong>de</strong> optimização. Para que não ocorram falhas, <strong>de</strong>ve<br />

garantir-se que a transição <strong>para</strong> uma tensão inferior não tem <strong>de</strong>masia<strong>do</strong> impacto no <strong>de</strong>sempenho.<br />

Esta margem <strong>de</strong> segurança <strong>de</strong>ve ser consi<strong>de</strong>rada no momento da calibração e é tanto menor quanto<br />

maior for a resolução na programação da tensão na PMU.<br />

18

3. Sensor Global<br />

Por outro la<strong>do</strong>, apenas gran<strong>de</strong>s variações na temperatura <strong>do</strong> circuito fazem aumentar<br />

significativamente o atraso. Assim, apenas é necessário garantir que o intervalo <strong>de</strong> tempo entre as<br />

verificações <strong>de</strong> <strong>de</strong>sempenho não é <strong>de</strong>masia<strong>do</strong> eleva<strong>do</strong> <strong>para</strong> causar erros quan<strong>do</strong> o gradiente <strong>de</strong><br />

temperatura é máximo.<br />

Depen<strong>de</strong>n<strong>do</strong> da tecnologia na qual é projecta<strong>do</strong> o sensor, bem como da arquitectura <strong>do</strong> circuito<br />

em monitorização, a distribuição <strong>do</strong>s flip-flops pelo circuito réplica po<strong>de</strong> ser feita <strong>de</strong> mo<strong>do</strong> a minimizar<br />

os recursos utiliza<strong>do</strong>s. Tipicamente, os microprocessa<strong>do</strong>res estão dividi<strong>do</strong>s em blocos funcionais que<br />

po<strong>de</strong>m ser <strong>de</strong>sliga<strong>do</strong>s consoante o tipo <strong>de</strong> operações a realizar. Diferentes blocos em funcionamento<br />

significam diferentes caminhos críticos a ter em consi<strong>de</strong>ração. Uma melhor optimização <strong>do</strong> consumo<br />

po<strong>de</strong> ser feita ten<strong>do</strong> em conta os caminhos críticos activos num <strong>de</strong>termina<strong>do</strong> instante. Deste mo<strong>do</strong>,<br />

po<strong>de</strong>m colocar-se apenas flip-flops em torno das zonas correspon<strong>de</strong>ntes ao atraso <strong>do</strong>s caminhos<br />

críticos <strong>de</strong> cada bloco. Um exemplo <strong>de</strong>sta abordagem é ilustra<strong>do</strong> na Figura 3.9.<br />

Figura 3.9 – Exemplo <strong>de</strong> optimização no Sensor PVTA<br />

Esta abordagem permite excluir a análise das primeiras NOR uma vez que estão muito distantes<br />

<strong>do</strong> atraso <strong>do</strong> caminho crítico, permitin<strong>do</strong> reduzir a complexida<strong>de</strong> <strong>do</strong> controlo necessária <strong>para</strong><br />

processar a informação. Consoante o nível <strong>de</strong> sensibilida<strong>de</strong> pretendi<strong>do</strong>, o espaçamento entre flip-<br />

-flops consecutivos po<strong>de</strong> ser <strong>de</strong> várias portas NOR. Este aumento <strong>do</strong> atraso entre <strong>do</strong>is flip-flops<br />

consecutivos limita as situações em que o código termómetro oscila entre <strong>do</strong>is valores <strong>de</strong>vi<strong>do</strong> a<br />

diferenças mínimas no atraso da ca<strong>de</strong>ia. É importante frisar que a não introdução <strong>de</strong> flip-flops em<br />

todas as portas NOR leva a que o tempo <strong>de</strong> atraso no circuito réplica <strong>de</strong>ixe <strong>de</strong> ser uniforme, sen<strong>do</strong><br />

maior nas portas NOR que têm a capacida<strong>de</strong> no nó <strong>de</strong> saída aumentada pela ligação <strong>do</strong> flip-flop. Por<br />

esse motivo po<strong>de</strong>m ser coloca<strong>do</strong>s inversores com impedância <strong>de</strong> entrada semelhante à <strong>do</strong>s flip-flops<br />

nas portas NOR excluídas.<br />

19

3. Sensor Global<br />

3.3 Temporiza<strong>do</strong>r<br />

Devi<strong>do</strong> ao funcionamento periódico <strong>do</strong> Sensor Global, <strong>para</strong> implementar o bloco Temporiza<strong>do</strong>r<br />

são necessários <strong>do</strong>is subsistemas. O primeiro é um divisor <strong>de</strong> relógio <strong>para</strong> gerar a base <strong>de</strong> tempo<br />

<strong>para</strong> o accionamento <strong>do</strong> sensor. O segun<strong>do</strong> dispositivo é uma máquina <strong>de</strong> esta<strong>do</strong>s que é accionada<br />

pelo divisor <strong>de</strong> relógio e cujo objectivo é gerar os sinais <strong>de</strong> controlo necessários aos três submo<strong>do</strong>s<br />

presentes no Mo<strong>do</strong> <strong>de</strong> Teste <strong>do</strong> Sensor PVTA.<br />

3.3.1 Divisor <strong>de</strong> Relógio<br />

Existem alguns méto<strong>do</strong>s <strong>para</strong> implementar divisores <strong>do</strong> sinal <strong>de</strong> relógio. No caso específico<br />

<strong>de</strong>ste trabalho interessa uma solução simples e <strong>de</strong> consumo reduzi<strong>do</strong>, mas que permita alguma<br />

flexibilida<strong>de</strong> na alteração da base <strong>de</strong> tempo. A solução que mais se aproxima <strong>do</strong>s objectivos<br />

pretendi<strong>do</strong>s é o conta<strong>do</strong>r assíncrono. Esta topologia <strong>de</strong> conta<strong>do</strong>r tem a vantagem <strong>de</strong> usar apenas<br />

flip-flops na sua implementação, com o benefício <strong>de</strong> consumir menos energia <strong>do</strong> que o conta<strong>do</strong>r<br />

síncrono.<br />

O funcionamento <strong>de</strong>ste conta<strong>do</strong>r baseia-se na realimentação negativa <strong>para</strong> forçar a alternância<br />

<strong>de</strong> esta<strong>do</strong>s em ciclos <strong>de</strong> relógio consecutivos. No exemplo da Figura 3.10 po<strong>de</strong> ver-se que a cada<br />

novo ciclo <strong>de</strong> relógio o flip-flop coloca na saída o esta<strong>do</strong> oposto ao esta<strong>do</strong> anterior. O sinal obti<strong>do</strong> tem<br />

assim um perío<strong>do</strong> que é o <strong>do</strong>bro <strong>do</strong> sinal <strong>de</strong> entrada.<br />

Figura 3.10 – Princípio <strong>de</strong> funcionamento <strong>do</strong> conta<strong>do</strong>r assíncrono<br />

Deste mo<strong>do</strong>, ten<strong>do</strong> em conta que cada flip-flop implementa uma divisão por <strong>do</strong>is relativamente<br />

ao seu sinal <strong>de</strong> relógio, po<strong>de</strong>m obter-se sucessivas divisões colocan<strong>do</strong> vários flip-flops enca<strong>de</strong>a<strong>do</strong>s<br />

ligan<strong>do</strong> apenas as entradas <strong>de</strong> relógio à saída <strong>do</strong> flip-flop anterior. Esta meto<strong>do</strong>logia tem o nome <strong>de</strong><br />

ripple counter e a frequência que é obtida na saída <strong>de</strong> cada flip-flop é dada pela expressão (3.1):<br />

f = f lk<br />

(3.1)<br />

on<strong>de</strong><br />

é o numero <strong>de</strong> flip-flops a montante na ca<strong>de</strong>ia.<br />

20

3. Sensor Global<br />

Na Figura 3.11 po<strong>de</strong>r ver-se um exemplo da implementação <strong>do</strong> ripple counter. Neste caso<br />

preten<strong>de</strong>-se obter um conta<strong>do</strong>r crescente e por esse motivo é necessário que as entradas <strong>de</strong> relógio<br />

<strong>do</strong>s flip-flops seguintes tenham origem na saída Q negada <strong>do</strong> flip-flop anterior. Caso contrário o<br />

conta<strong>do</strong>r seria <strong>de</strong>crescente.<br />

Figura 3.11 – Esquema lógico e diagrama temporal <strong>de</strong> um Ripple Counter crescente <strong>de</strong> 4 bits<br />

Na figura anterior as transições <strong>de</strong> esta<strong>do</strong> a partir <strong>do</strong> segun<strong>do</strong> flip-flop surgem no flanco<br />

negativo. Isto <strong>de</strong>ve-se ao facto <strong>do</strong> diagrama temporal mostrar apenas as saídas Q e não as saídas<br />

que servem <strong>de</strong> relógio ao flip-flop seguinte. Neste conta<strong>do</strong>r to<strong>do</strong>s os flip-flops são <strong>do</strong> tipo edge trigger<br />

positivo.<br />

De referir que este conta<strong>do</strong>r tem o inconveniente das saídas não serem totalmente síncronas<br />

entre si. Isto acontece porque os flip-flops têm entradas <strong>de</strong> relógios in<strong>de</strong>pen<strong>de</strong>ntes cujos atrasos<br />

<strong>de</strong>pen<strong>de</strong>m <strong>do</strong>s flip-flops anteriores. Por este motivo, ao usar o relógio dividi<strong>do</strong> <strong>para</strong> actuar a máquina<br />

<strong>de</strong> esta<strong>do</strong>s <strong>do</strong> sensor <strong>de</strong>ve colocar-se um registo sincroniza<strong>do</strong> com o relógio <strong>para</strong> prevenir violações<br />

temporais. Deste mo<strong>do</strong>, <strong>de</strong>ixa <strong>de</strong> existir qualquer limitação na utilização <strong>de</strong>ste conta<strong>do</strong>r, po<strong>de</strong>n<strong>do</strong><br />

assim tirar-se parti<strong>do</strong> da menor área e <strong>do</strong> menor consumo utiliza<strong>do</strong>s.<br />

21

3. Sensor Global<br />

O número <strong>de</strong> flip-flops a utilizar <strong>de</strong>pen<strong>de</strong> da frequência <strong>de</strong> relógio e <strong>do</strong> tempo que o controlo<br />

externo <strong>de</strong>mora a executar as operações <strong>de</strong> subida e <strong>de</strong>scida da tensão <strong>do</strong> circuito. O intervalo entre<br />

verificações po<strong>de</strong> ser estático ou dinâmico <strong>de</strong>pen<strong>de</strong>n<strong>do</strong> das necessida<strong>de</strong>s. Caso se pretenda usar<br />