You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

<strong>Loginiai</strong> <strong>elementai</strong><br />

Pramoninė elektronika. 10 paskaita "<strong>Loginiai</strong> <strong>elementai</strong>"<br />

<strong>Loginiai</strong> <strong>elementai</strong> (angl. – digital gates; gates) – elektroninės schemos, realizuojančios elementarias logikos algebros<br />

funkcijas.<br />

Tas pačias logines funkcijas gali vykdyti skirtingų schemų loginiai <strong>elementai</strong>. Įvairios loginių elementų schemų<br />

atmainos skiriasi naudojama maitinimo šaltinio galia ir veikimo sparta, maitinimo įtampos dydžiu, aukštų ir žemų<br />

lygių įtampomis, atsparumu trikdžiams, kaina.<br />

Loginių elementų klasifikavimas<br />

Pagal valdančiuosius signalus skiriami impulsiniai ir potencialiniai loginiai <strong>elementai</strong>. Impulsinius elementus valdo<br />

trumpi įtampos arba srovės impulsai, potencialinius — įtampų lygiai (žema ir aukšta įtampa).<br />

Pagal loginio vieneto ir loginio nulio įtampas skiriami teigiamos ir neigiamos logikos <strong>elementai</strong>. Teigiamoje<br />

logikoje aukštas įtampos lygis atitinka vienetą, žemas — nulį, neigiamoje logikoje esti atvirkščiai. Tas pats loginis<br />

elementas teigiamos ir neigiamos logikos schemose vykdo skirtingas logines funkcijas: prisiminkime de Morgano<br />

teoremą, teigiančią, kad po loginių kintamųjų inversijos loginis elementas ARBA-NE vykdo loginę funkciją IR, o<br />

loginis elementas IR-NE — loginę funkciją ARBA.<br />

Pagal schemos elementus skiriami dvipolių ir vienpolių tranzistorių, tranzistorinės logikos (TL), diodinėstranzistorinės<br />

logikos (DTL) ir tranzistorinės-tranzistorinės logikos (TTL) loginiai <strong>elementai</strong>.<br />

Pagal loginio elemento schemą skiriami sujungtųjų kolektorių ir sujungtųjų emiterių schemų loginiai <strong>elementai</strong> bei<br />

loginiai <strong>elementai</strong>, kuriuose loginę funkciją vykdo schemos komponentai jos įėjime.<br />

<strong>Loginiai</strong> <strong>elementai</strong> taip pat klasifikuojami pagal vartojamą maitinimo šaltinio galią ir veikimo spartą. Šie du<br />

parametrai neatskiriami vienas nuo kito: vienam iš jų didėjant didėja ir kitas, ir atvirkščiai. Šį ryšį nesunku paaiškinti: 1<br />

didesnės srovės greičiau perkrauna parazitines talpas.<br />

Dvipolių tranzistorių loginiai <strong>elementai</strong><br />

Dvipolio tranzistoriaus raktas<br />

Pramoninė elektronika. 10 paskaita "<strong>Loginiai</strong> <strong>elementai</strong>"<br />

Logines funkcijas gali vykdyti schemos su bet kokiais raktais — mechaniniais, elektromechaniniais arba elektroniniais. Elektroniniai<br />

raktai gaminami integrine technologija, todėl yra patikimi ir spartūs, mažos masės ir tūrio, vartoja mažą maitinimo šaltinio galią, yra<br />

pigūs.<br />

Elektroninį raktą sudaro valdančioji ir komutuojama grandinės, pastarąją raktas gali nutraukti arba sujungti.<br />

Reikalavimai elektroniniams raktams:<br />

• kuo didesnė atviro rakto ir kuo mažesnė uždaro rakto varžos;<br />

• didelė veikimo sparta;<br />

• valdančiosios ir komutuojamos grandinių atskyrimas;<br />

• atsparumas trikdžiams;<br />

• parametrų pastovumas.<br />

Dvipolių tranzistorių raktai yra spartesni už vienpolių tranzistorių raktus, jie pasižymi maža uždaro rakto varža, bet valdančioji grandinė<br />

(bazė-emiteris) ir komutuojama grandinė (kolektorius-emiteris) šiuose raktuose neatskirtos; šiuo požiūriu jie prastesni už vienpolių<br />

tranzistorių su izoliuotąja užtūra raktus.<br />

Paprasčiausias elektroninis raktas — varžinis stiprinimo laipsnis:<br />

I K<br />

+ E K<br />

E K<br />

R K<br />

R K A S<br />

U K = U IÐ<br />

VT<br />

R B<br />

U IN<br />

I B = I BS<br />

I B = 0<br />

A<br />

0 A<br />

UKS = U 0 UKA = U 1 E K<br />

I B = –I K0<br />

U K<br />

2

Aukštas rakto su dvipoliu tranzistoriumi išėjimo lygis U I ≈ E K<br />

(maitinimo įtampai).<br />

Pramoninė elektronika. 10 paskaita "<strong>Loginiai</strong> <strong>elementai</strong>"<br />

Žemas rakto su dvipoliu tranzistoriumi išėjimo lygis U 0 = 0,1 – 0,2 V (įtampos krytis įsotintame tranzistoriuje).<br />

Įtampos tarp soties režimu dirbančio tranzistoriaus elektrodų:<br />

p<br />

0.5 V<br />

+<br />

+<br />

0.7 V<br />

n<br />

– +<br />

– –<br />

n<br />

0.2 V<br />

Kiekviena rakto apkrova turi aktyviąją ir talpinę varžos dedamąsias:<br />

+ E K<br />

R K<br />

U K = U IÐ<br />

VT<br />

Rap<br />

Cap<br />

Dvipolio tranzistoriaus raktas sparčiau persijungia iš loginio 1 į 0 (nereikia perkrauti apkrovos talpos), perjungimas iš loginio 0<br />

į 1 trunka ilgiau (perkraunama apkrovos talpa ir didelė tranzistoriaus uždarymo trukmė).<br />

U 1<br />

U<br />

0→1 1→ 0<br />

U 0<br />

0<br />

t<br />

3<br />

TRTL — tiesioginių ryšių tranzistorinė logika<br />

Pramoninė elektronika. 10 paskaita "<strong>Loginiai</strong> <strong>elementai</strong>"<br />

TRTL (angl. DCTL — Direct Coupled Transistor Logic) — tai sujungtųjų kolektorių loginės schemos, kuriose keli tranzistoriai<br />

jungiami su bendra kolektoriaus apkrova.<br />

+ E K<br />

R K<br />

VT4<br />

F= A+ B+ C<br />

U IN1<br />

VT1<br />

U IN2<br />

VT2<br />

U IN3<br />

VT3<br />

U IÐ<br />

A B C<br />

VT5<br />

Tiesioginių ryšių tranzistorinės logikos privalumai:<br />

• Paprasta schema; ją sudaro tik dviejų tipų komponentai.<br />

• Tranzistorių daugiau negu rezistorių – puslaidininkinėje integrinėje TRTL schemoje tranzistoriai užima mažesnį kristalo plotą negu<br />

rezistoriai.<br />

• Schema sparti; kuo mažesnė rezistoriaus R K<br />

varža, tuo schema spartesnė.<br />

Trūkumai:<br />

• Daug tranzistorių – jų yra tiek, kiek ir loginių įėjimų, todėl vartojama didelė maitinimo šaltinio galia.<br />

• Nedidelis loginis šuolis (apytikriai 0,5 V) ir jo rezultatas – mažas atsparumas trikdžiams: trikdis, 0,5V viršijantis žemą loginio<br />

elemento išėjimo įtampos lygį, jau atidaro apkrovos tranzistorių.<br />

• Neapibrėžta apkrovų įėjimo srovė; dėl to, supainiojus loginius lygius, gali atsirasti loginė klaida.<br />

TRTL trūkumai yra esminiai ir jie lėmė, kad šiandien nagrinėtojo pavidalo TRTL netaikoma. Šių abiejų trūkumų neturi rezistorinių<br />

ryšių tranzistorinė logika.<br />

4

RRTL — rezistorinių ryšių tranzistorinė logika<br />

Pramoninė elektronika. 10 paskaita "<strong>Loginiai</strong> <strong>elementai</strong>"<br />

RRTL (angl. RCTL Resistor Coupled Transistor Logic) loginių elementų schemos nuo TRTL skiriasi tuo, kad į visų tranzistorių<br />

bazės grandines yra nuo-sekliai įjungti rezistoriai R b<br />

, kurių varža daug didesnė už tranzistoriaus įėjimo varžą:<br />

R<br />

B<br />

≫ r<br />

IN<br />

+E K<br />

R K<br />

U IN1<br />

R B VT1<br />

U IN2<br />

R B<br />

VT2<br />

A<br />

B<br />

Apkrauto RRTL loginio elemento išėjimo įtampa daug aukštesnė negu apkrauto TRTL elemento, nes RRTL elemente įtampa krinta ne<br />

tik atviroje pn sandūroje, bet ir daug didesnės varžos rezistoriuje R B.<br />

Rezistorinių ryšių tranzistorinės logikos privalumai:<br />

• Aukštas išėjimo įtampos lygis (varžos R B<br />

įtaka).<br />

• Nėra apkraunančių tranzistorių įėjimo srovių neapibrėžtumo (varžos R B<br />

įtaka).<br />

Trūkumai:<br />

• Schemoje daugiau elementų, ypač daug rezistorių, kurių didelė varža ir kurie kristale užima daugiau ploto.<br />

• Nuosekliai įjungtas į tranzistoriaus bazės grandinę didelės varžos rezistorius mažina atviro rakto (uždaro tranzistoriaus) varžą.<br />

•Tas pats rezistorius mažina loginio elemento veikimo spartą: dėl didelės jo varžos įėjimo grandine teka silpna srovė, todėl<br />

lėčiau įkraunamos tranzistorių įėjimo talpos.<br />

5<br />

RRTL su loginę funkciją vykdančiais komponentais schemos įėjime<br />

Pramoninė elektronika. 10 paskaita "<strong>Loginiai</strong> <strong>elementai</strong>"<br />

Tai buvo pati populiariausia ir pigiausia loginių elementų iš diskretinių komponentų atmaina. Tai yra tarpinis tranzistorinės ir<br />

diodinės-tranzistorinės logikos variantas.<br />

R1 = R2 = R3<br />

R1<br />

A<br />

R2<br />

B<br />

R3<br />

C<br />

– E<br />

R5<br />

VT<br />

R4<br />

+ E K<br />

F= A+ B+ C<br />

Šios logikos privalumas, palyginti su sujungtųjų kolektorų schemomis, yra tai, kad nepriklausomai nuo loginių įėjimų skaičiaus loginio<br />

elemento schemoje yra tik vienas tranzistorius. Tai garantuoja mažesnę loginio elemento sklaidomą galią.<br />

Logikos trūkumai — dar daugiau rezistorių negu klasikinėje RRTL ir papildomas neigiamos įtampos maitinimo šaltinis.<br />

Aptariamoji logika netinka šiuolaikinei gamybai dėl didelio rezistorių skaičiaus. Situacija pasikeistų, jei rezistorius Rl, R2 ir R3<br />

loginiuose įėjimuose pakeistume diodais. Tačiau tai jau būtų ne tranzistorinė, bet diodinė-tranzistorinė logika.<br />

6

Diodinė-tranzistorinė logika<br />

Pramoninė elektronika. 10 paskaita "<strong>Loginiai</strong> <strong>elementai</strong>"<br />

+ E K<br />

A<br />

B<br />

C<br />

R1<br />

VD1<br />

VD2 VD4 VD5<br />

D<br />

VD3<br />

– E<br />

R2<br />

R3<br />

VT<br />

F= A⋅B⋅C<br />

+ E K<br />

R1<br />

VD1 VD4 VD5<br />

– 0.7 V + + 0.7 V – + 0.7 V –<br />

A<br />

+ +<br />

0.2 V 0.9 V<br />

– –<br />

D<br />

+<br />

F<br />

–<br />

0.2 V 0.5 V<br />

– +<br />

R2<br />

– E<br />

B<br />

Aptariamasis DTL loginis elementas tinkamai veiks tik tuomet, kai jo schemoje bus atkuriantis žemą įtampos lygį diodas VD4. Be<br />

diodo VD5 schema gali veikti, nes jis tik pagerina loginio elemento parametrus. Kita diodų VD4 ir VD5 paskirtis – pagreitinti<br />

tranzistoriaus VT uždarymą.<br />

DTL privalumai (lyginama su tranzistorine logika):<br />

•Aukštas įtampos lygis apkrauto loginio elemento išėjime garantuoja didelį loginį šuolį ir gerą atsparumą trikdžiams (šį dar didina<br />

papildomas žemą įtampos lygį žeminantis diodas bei papildomas neigiamos įtampos maitinimo šaltinis).<br />

•Labai žemas tranzistoriaus įėjimo įtampos lygis garantuoja didelę atviro rakto (tranzistoriaus, dirbančio atkirtos režimu) varžą.<br />

•Loginio elemento schemoje nepriklausomai nuo loginių įėjimų skaičiaus yra tik vienas tranzistorius, todėl schemos sklaidoma galia<br />

esti nedidelė.<br />

•Diodai kristale užima mažiau ploto negu rezistoriai, vadinasi, schema pasižymi aukštu integracijos laipsniu ir kitais iš to<br />

išplaukiančiais privalumais.<br />

•Gerą spartą garantuoja nedidelis diodų užimamas plotas kristale, mažos jų parazitinės talpos ir nuosekliai į bazės grandinę įjungti<br />

diodai, pagreitinantys tranzistoriaus uždarymą.<br />

Trūkumai:<br />

•Schemoje yra daug elementų, kristale užimančių nemažą plotą.<br />

•Reikalingas papildomas neigiamos įtampos maitinimo šaltinis.<br />

7<br />

Tranzistorinė-tranzistorinė logika<br />

Pramoninė elektronika. 10 paskaita "<strong>Loginiai</strong> <strong>elementai</strong>"<br />

Tranzistorinė-tranzistorinė logika – pati populiariausia dvipolių tranzistorių logikos atmaina. TTL loginio elemento schema<br />

gauta iš DTL loginio elemento schemos, pakeitus šioje įėjimo diodų VD1, VD2 ir VD3 np sandūras daugiaemiterinio<br />

tranzistoriaus emiterių-bazės np sandūromis, o pirmojo žemą įtampos lygį atkuriančio diodo VD4 pn sandūrą – įėjimo<br />

tranzistoriaus bazės-kolektoriaus pn sandūra.<br />

+ E K<br />

A<br />

B<br />

C<br />

R1 R3<br />

VT1<br />

VD5<br />

VT2<br />

R2<br />

– E<br />

F= A⋅B⋅C<br />

Paprasčiausias TTL loginis elementas<br />

+ E K<br />

A<br />

B<br />

C<br />

R1<br />

R2<br />

VT1 VT2<br />

F= A⋅B⋅C<br />

8

Pramoninė elektronika. 10 paskaita "<strong>Loginiai</strong> <strong>elementai</strong>"<br />

Standartinis TTL loginis elementas (Dvitaktis išėjimo laipsnis )<br />

+ E K<br />

A<br />

B<br />

C<br />

R2<br />

R1<br />

VT1 VT2<br />

VT3<br />

VD<br />

VT4<br />

R4<br />

F= A⋅B⋅C<br />

R3<br />

Ra<br />

Ca<br />

Dvitaktį laipsnį sudaro du nuosekliai sujungti tranzistoriai VT3 ir VT4, valdomi priešingo poliškumo signalais. Juos sukuria<br />

fazoinversinis laipsnis – tranzistorius VT2.<br />

a<br />

b<br />

c<br />

R2<br />

R1<br />

VT1 d VT2<br />

e<br />

g<br />

VT3<br />

h<br />

VD<br />

VT4<br />

R3<br />

R4<br />

k<br />

f<br />

+ E K<br />

visų įėjimų įtampa žema<br />

Taškas Taško potencialas<br />

a + 0,2 V<br />

d + 0,9 V<br />

e + 0,4 V<br />

g 0<br />

h +E K<br />

k E K<br />

– 0,7 V<br />

f E K<br />

– 1,4 V<br />

visų įėjimų įtampa aukšta<br />

Taškas Taško potencialas<br />

a,b,c + 3,6 V<br />

d + 2,1 V<br />

e + 1,4 V<br />

g + 0,7 V<br />

h + 0,9 V<br />

k + 0,55 V<br />

f + 0,2 V<br />

9<br />

Šotkio TTL<br />

Pramoninė elektronika. 10 paskaita "<strong>Loginiai</strong> <strong>elementai</strong>"<br />

Šotkio TTL (TTLŠ, angl. – Schottky TTL) – tai ta pati tranzistorinė-tranzistorinė logika, tik su Šotkio tranzistoriais. Šotkio<br />

tranzistoriai neįsisotina, todėl greitai užsidaro. Dėl šios priežasties TTLS spartesnė už standartinę TTL.<br />

VDŠ<br />

VT<br />

≡<br />

VTŠ<br />

TTLŠ privalumas — didesnė veikimo sparta; trūkumai: dėl neįsisotinančio išėjimo tranzistoriaus loginio elemento išėjime gaunamas<br />

aukštesnis žemos įtampos lygis, taigi ir mažesnis atsparumas trikdžiams.<br />

Kai rezistorių kolektorių grandinių varžos esti vienodos, srovė, tekanti praviru tranzistoriumi, yra silpnesnė už srovė, tekančią įsotintu<br />

tranzistoriumi. Todėl TTLŠ reikia mažesnės maitinimo šaltinio galios nei TTL. Tačiau, kad būtų realizuota didelė TTLŠ veikimo sparta,<br />

TTLŠ schemose paprastai naudojamas mažesnės varžos kolektoriaus rezistorius, todėl TTLŠ loginis elementas dažniausiai vartoja<br />

didesnę galią.<br />

10

Sujungtųjų emiterių tranzistorinė logika<br />

Pramoninė elektronika. 10 paskaita "<strong>Loginiai</strong> <strong>elementai</strong>"<br />

Sujungtųjų emiterių tranzistorine logika (SETL, kartais SEL, angl. – Emitter-Coupled-Logic – ECL) – šiandien pati sparčiausia logikos<br />

atmaina. Pagrindinę schemos dalį sudaro TRTL loginis elementas – tranzistoriai VT1, VT2 ir VT3 su bendra kolektoriaus apkrova Rl.<br />

Žinome, kad toks loginis elementas vykdo loginę funkciją ARBA-NE. Jo išėjimo signalą pakartoja emiterinis kartotuvas-srovės<br />

stiprintuvas – tranzistorius VT5 su apkrovos rezistoriumi R4.<br />

R1<br />

R3<br />

VT5<br />

VT6<br />

+ E K<br />

VT1 VT2 VT3<br />

VT4<br />

F1= A+ B+ C<br />

A B C<br />

+ E<br />

R2<br />

R4<br />

R5<br />

F2= A+ B+ C<br />

Sujungtųjų emiterių tranzistorinės logikos privalumai:<br />

1. Pati didžiausia veikimo sparta, kurią lemia:<br />

a) rezistorius sujungtų emiterių grandinėje, neleidžiantis tranzistoriams įsisotinti, taigi ir spartinantis šių tranzistorių uždarymą;<br />

b) schemos išėjimuose naudojami emiteriniai kartotuvai, kurių mažos išėjimo varžos lemia mažas apkrovos talpų laiko pastoviąsias<br />

(didelė emiterinių kartotuvų-srovės stiprintuvų srovė greitai perkrauna apkrovos talpas);<br />

c) nepriklausomai nuo loginio elemento įėjimo įtampų per rezistorių R2 nuolat tekanti srovė, sukurianti beveik nekintančią įtampą,<br />

todėl tos schemos dalies parazitinės talpos nepersikrauna.<br />

2. Srovės stiprintuvai išėjimuose garantuoja didelį skaidos koeficientą — galimybę prijungti prie loginio elemento išėjimo daug<br />

loginių elementų.<br />

3. Loginio elemento išėjimuose gaunama tiesioginė arba inversine logines funkcijos 3ARBA reikšmė.<br />

Trūkumai:<br />

1. Pati didžiausia vartojama maitinimo šaltinio galia.<br />

2. Sudėtinga schema, todėl nedidelis jos integracijos laipsnis ir nemaža loginio elemento kaina.<br />

3. Nedidelis loginis šuolis ir nedidelis atsparumas trikdžiams.<br />

11<br />

Vienpolių tranzistorių loginiai <strong>elementai</strong><br />

Pramoninė elektronika. 10 paskaita "<strong>Loginiai</strong> <strong>elementai</strong>"<br />

Paprastai loginių elementų schemoms sudaryti naudojami MOP struktūros lauko tranzistoriai su izoliuotosiomis užtūromis.<br />

Loginių elementų valdomaisiais arba loginiais tranzistoriais būna MOP tranzistoriai su indukuotuoju kanalu. Įtampos kritimas tokiame<br />

atvirame tranzistoriuje atitinka žemą įtampos lygį, nes jo nepakanka šį loginį elementą apkraunantiems kitų loginių elementų<br />

tranzistoriams atidaryti. Įtampos kritimas uždaruose tranzistoriuose su indukuotuoju kanalu paprastai būna lygus maitinimo šaltinio<br />

įtampai. Tai tolygu aukštam įtampos lygiui, atidarančiam apkraunančiųjų loginių elementų tranzistorius.<br />

Vienpolių tranzistorių raktai<br />

MOP tranzistorių raktą sudaro loginiais įėjimo įtampos lygiais valdomas aktyvusis, arba loginis, tranzistorius ir apkrovos tranzistorius.<br />

Apkrovos tranzistorius gali dirbti pasyviu režimu, kai jis nevaldomas, ir aktyviu, kai valdomas.<br />

Raktai su pasyviąja apkrova<br />

VT1<br />

+E<br />

VT2<br />

U IŠ<br />

U IN<br />

Raktas veiks patikimai, jei apkrovos tranzistoriaus kanalo varža bus apie dešimt kartų didesnė už loginio tranzistoriaus kanalo varžą.<br />

Tuomet maitinimo įtampa atviruose tranzistoriuose dalysis taip, kad įtampos kritimas loginiame tranzistoriuje tesudarys apie vieną<br />

dešimtąją maitinimo įtampos dalį. Tai reiškia, kad esant aukštai rakto schemos įėjimo įtampai, gaunama žema išėjimo įtampa,<br />

neatidaranti apkraunančių raktą tranzistorių.<br />

12

Pramoninė elektronika. 10 paskaita "<strong>Loginiai</strong> <strong>elementai</strong>"<br />

Raktas, kurio apkrovos tranzistoriaus užtūros įtampa U u > E + U d<br />

+E U<br />

+E<br />

VT1<br />

VT2<br />

U IŠ<br />

Apkrovos tranzistorius šioje schemoje visuomet atviras<br />

U IN<br />

Kai schemos įėjimo įtampa yra aukšta, maitinimo šaltinio įtampa dviejuose atviruose vienodos topologijos tranzistoriuose dalijasi<br />

pusiau. Todėl ir šioje schemoje apkrovos tranzistoriaus VTl kanalo varža turi būti apie dešimt kartų didesnė už loginio tranzistoriaus<br />

VT2 kanalo varžą, nes tik tai garantuoja pakankamai žemą įtampos lygį schemos išėjime.<br />

Raktas, kai apkrova – tranzistorius su sudarytuoju kanalu.<br />

+E<br />

VT1<br />

Apkrovos tranzistorius visuomet yra atviras ar bent praviras.<br />

VT2<br />

U IŠ<br />

U IN<br />

Schemos privalumas yra tas, kad joje nereikia formuoti tranzistoriaus su didele kanalo varža.Šios schemos tranzistorius „pats<br />

pasistengia", kad jo varža būtų tokia, kokios reikia: arba labai didelė, arba labai maža.<br />

13<br />

Raktas su aktyviąja apkrova – KMOP raktas<br />

Pramoninė elektronika. 10 paskaita "<strong>Loginiai</strong> <strong>elementai</strong>"<br />

Raktą su aktyviąja apkrova sudaro nuosekliai sujungtų papildančiųjų, arba komplementinių – su p kanalu ir su n kanalu, MOP<br />

tranzistorių pora (angl. – Complementary MOSFET – CMOS). Kadangi įėjimo signalas patenka į sujungtas abiejų tranzistorių užtūras,<br />

abu tranzistoriai yra valdomi ir veikia aktyviuoju režimu.<br />

VT1<br />

+E<br />

VT2<br />

U IŠ<br />

U IN<br />

KMOP rakto privalumai:<br />

• Esant bet kokiai įėjimo signalo reikšmei, bent vienas iš nuosekliai sujungtų tranzistorių (arba VTl, arba VT2) yra uždaras, o tai<br />

reiškia, kad nuoseklia grandine neteka maitinimo šaltinio srovė ir nenaudojama maitinimo šaltinio galia.<br />

• Žemas išėjimo įtampos lygis visuomet lygus nuliui, kad ir kokios būtų tranzistorių kanalų varžos. Vadinasi, ir vieno, ir kito<br />

tranzistoriaus kanalo matmenys gali būti minimalūs, ir tai iš dalies kompensuoja didesnį rakto schemos elementų užimamą plotą, kurio<br />

prireikia formuojant tranzistorius ir su p, ir su n kanalais.<br />

• Loginis šuolis, tai yra aukšto ir žemo įtampos lygių skirtumas, lygus maitinimo šaltinio įtampai. Didelis loginis šuolis garantuoja gerą<br />

atsparumą trikdžiams.<br />

• Schemoms su KMOP raktais galima naudoti gerokai mažesnes maitinimo įtampas. Jei standartinėse MOP tranzistorių su<br />

indukuotuoju kanalu schemose maitinimo įtampa tris-keturis kartus viršija slenksčio įtampą, tai KMOP raktų schemose pakan ka, kad<br />

maitinimo įtampa būtų bent truputį didesnė už ją.<br />

Nedidelė maitinimo įtampa KMOP loginėms schemoms teikia šiuos privalumus:<br />

pagal maitinimo įtampą ir loginius lygius KMOP schemos yra suderinamos su standartinėmis dvipolių tranzistorių loginėmis<br />

schemomis;<br />

galima formuoti šiek tiek storesnį dielektriko sluoksnį po užtūros elektrodu, nes dėl šiek tiek padidėjusios slenksčio įtampos maitinimo<br />

14<br />

įtampa keturgubai nepadidės; be to, kai po užtūros elektrodu esti storesnis dielektriko sluoksnis, mikroschemos su KMOP raktais ne taip<br />

greitai pramušamos, kaip nMOP arba pMOP mikroschemos su nMOP arba pMOP raktais.

nMOP ir pMOP tranzistorinė logika<br />

Pramoninė elektronika. 10 paskaita "<strong>Loginiai</strong> <strong>elementai</strong>"<br />

Paskutiniuoju metu vis plačiau taikomos MOP tranzistorių su n kanalais loginės schemos. Svarbiausioji to priežastis – esant tai pačiai<br />

temperatūrai ir priemaišų koncentracijai, elektronai beveik tris kartus judresni negu skylės, todėl ir nMOP schemoms būdinga didesnė veikimo<br />

sparta. Kita priežastis – nMOP loginių schemų maitinimo įtampa ir aukšto bei žemo loginių lygių įtampos yra to paties poliškumo, kaip ir<br />

standartinių dvipolių npn tranzistorių loginių schemų. Tačiau pMOP loginių schemų yra mažesnė kaina.<br />

VT1<br />

+E U<br />

+E<br />

A<br />

U IN1<br />

VT2<br />

B<br />

U IN2<br />

VT3<br />

A+B<br />

U IŠ<br />

Svarbiausieji MOPTL privalumai:<br />

1.MOPTL schemų integracijos laipsnis dviem-trim eilėmis didesnis negu standartinių dvipolių tranzistorių loginių schemų, nes:<br />

• tranzistoriams nereikia formuoti izoliuotų sričių;<br />

• ....schemose nėra rezistorių.<br />

Iš visų dvipolių tranzistorių loginių schemų tik injekcinio maitinimo tranzistorinės logikos schemos savo integracijos laipsniu prilygsta MOPTL<br />

schemoms.<br />

2. Didelis integracijos laipsnis ir paprasta gamybos technologija sąlygoja MOPTL schemų pigumą.<br />

3. Labai didelė tranzistorių su izoliuotomis užtūromis įėjimo varža ir praktiškai lygi nuliui apkraunančiųjų loginių elementų įėjimo srovė<br />

pašalina trūkumus, būdingus dvipolių tranzistorių TRTL schemoms: žemą aukštą išėjimo įtampos lygį ir mažą loginį šuolį.<br />

4. Didelis loginis šuolis lemia gerą atsparumą trukdžiams.<br />

5. Labai didelė apkraunančiųjų loginių elementų įėjimo varža leidžia kiekvieną loginį elementą apkrauti daugeliu kitų loginių elementų.<br />

Svarbiausieji MOPTL trūkumai:<br />

1. Kaip ir MOP tranzistoriai, taip ir MOPTL schemos nėra tokios sparčios, kaip dvipoliai tranzistoriai ir jų loginės schemos.<br />

2. Didelės maitinimo įtampos ir dideli loginiai šuoliai neleidžia naudoti MOPTL schemų kartu su dvipolių tranzistorių loginėmis schemomis.<br />

3. MOPTL schemoms būdingas didelis eksploatacinis trūkumas – jų tranzistorius gali negrįžtamai pramušti net ant žmogaus kūno ar drabužių<br />

15<br />

susikaupusių statinių krūvių sukurtos įtampos. Dėl šios priežasties iki montažo negalima liesti nMOPTL ir pMOPTL mikroschemų išvadų, be to,<br />

jas reikia labai atsargiai montuoti.<br />

Komplementinė MOP tranzistorinė logika<br />

Pramoninė elektronika. 10 paskaita "<strong>Loginiai</strong> <strong>elementai</strong>"<br />

Loginių schemų su komplementiniais MOP tranzistorių raktais sudarymo taisyklė: kai loginiai tranzistoriai jungiami lygiagrečiai, juos<br />

papildantys, arba komplementiniai, tranzistoriai jungiami nuosekliai; kai loginiai tranzistoriai jungiami nuosekliai, komplementiniai<br />

tranzistoriai jungiami lygiagrečiai.<br />

VT4<br />

+E U<br />

U IN2 B<br />

A<br />

U IN1<br />

VT1<br />

VT3<br />

VT2<br />

A+B<br />

U IŠ<br />

16

Pramoninė elektronika. 10 paskaita "<strong>Loginiai</strong> <strong>elementai</strong>"<br />

Svarbiausieji KMOPTL privalumai:<br />

1. Kai KMOPTL loginio elemento įėjimuose lygiai nekinta, loginis elementas veikia statiniu režimu, nes neteka maitinimo šaltinio<br />

srovė. Vadinasi, kai loginis elementas veikia statiniu režimu, nevartojama maitinimo šaltinio galia. Aptardami KMOP rakto savybes<br />

minėjome, kad maitinimo šaltinio galia vartojama tik parazitinėms talpoms perkrauti, kai keičiasi loginiai lygiai schemos įėjime ir<br />

išėjime. Taigi KMOPTL – pati ekonomiškiausia logika.<br />

2. KMOPTL schemų integracijos laipsnis yra šiek tiek mažesnis negu MOPTL schemų, bet gerokai didesnis nei dvipolių tranzistorių<br />

logikų schemų (išimtį sudaro tik injekcinio maitinimo tranzistorinės logikos schemos, kurių KMOPTL integracijos laipsniai panašūs).<br />

Pirmoji ir svarbiausioji priežastis, dėl kurios KMOPTL schemos integracijos laipsniu nusileidžia MOPTL schemoms, yra ta, kad<br />

KMOPTL schemas sudaro abiejų tipų MOP tranzistoriai: su n ir su p kanalais. Todėl vieno tipo tranzistoriams (paprastai su n kanalais)<br />

tenka formuoti specialias kito laidumo tipo sritis. Antroji priežastis – paprasčiausio loginio elemento 2ARBA-NE schemą sudaro keturi,<br />

o ne trys tranzistoriai. Kita vertus, užimamo kristale ploto požiūriu KMOPTL pranašesnė negu MOPTL, nes KMOPTL schemose<br />

nereikia formuoti apkrovos tranzistorių su keliolika kartų didesne nei loginių tranzistorių kanalo varža, o tai reiškia, kad visų KMOPTL<br />

tran- zistorių kanalai gali būti mažiausių ilgių ir pločių.<br />

Priežastys, kodėl KMOPTL integracijos laipsniu lenkia įvairias dvipolių tranzistorių logikos atmainas, išvardytos aptariant MOPTL<br />

savybes.<br />

Aukštas integracijos laipsnis ir gana paprasta gamyba sąlygoja nedidelę (mažesnę negu daugumos dvipolių tranzistorių logikų<br />

atmainų) KMOPTL mikroschemų kainą.<br />

Tai, kad aukštas išėjimo įtampos lygis yra lygus maitinimo įtampai, o žemas – nuliui, garantuoja didelį loginį šuolį ir gerą atsparumą<br />

trikdžiams. Didelis loginis šuolis leidžia mažinti tranzistorių jautrumą valdantiems signalams, tai yra didinti jų slenksčio įtampą. Todėl<br />

pagerėja tranzistorių eksploatacinės savybės – jie atsparesni pramušimui. Tai, kad loginis šuolis yra lygus maitinimo įtampai, leidžia<br />

sumažinti KMOPTL maitinimo įtampos dydį iki standartinių dvipolių tranzistorių loginių schemų maitinimo įtampos.<br />

Pagrindinis KMOPTL trūkumas, palyginti su įvairiomis dvipolių tranzistorių logikų schemomis, – mažesnė veikimo sparta. Kuo<br />

ekonomiškesniu režimu veikia KMOPTL schema (kuo mažesnės srovės perkrauna parazitines talpas keičiantis įtampų lygiams), tuo<br />

mažesnė KMOPTL veikimo sparta.<br />

17<br />

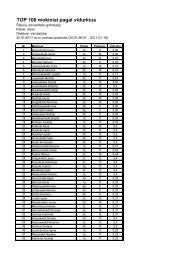

Populiariausiųjų loginių elementų svarbiausieji parametrai<br />

Pramoninė elektronika. 10 paskaita "<strong>Loginiai</strong> <strong>elementai</strong>"<br />

Logikos<br />

variantas<br />

Pvid<br />

mW/1LE<br />

tsv vid<br />

ns<br />

Avid<br />

pJ<br />

Ustat atsp tr<br />

V<br />

NIN<br />

NIŠ<br />

TTL<br />

standartinė<br />

H<br />

L<br />

S<br />

AS<br />

LS<br />

10<br />

25<br />

1<br />

20<br />

8<br />

2<br />

10<br />

6<br />

30<br />

5<br />

4<br />

10<br />

100<br />

150<br />

30<br />

100<br />

30<br />

20<br />

0.8<br />

0.8<br />

0.8<br />

0.5<br />

0.5<br />

0.5<br />

2 – 5<br />

10<br />

SEL<br />

50<br />

1.2<br />

60<br />

0.3<br />

2 – 5<br />

10 – 20<br />

IMTL<br />

0.01 – 0.1<br />

100 – 10<br />

1<br />

0.05<br />

2 – 3<br />

3 – 5<br />

MOPTL<br />

0.5<br />

100<br />

50<br />

2 – 3<br />

2 – 5<br />

50<br />

KMOPTL<br />

C<br />

HC<br />

0.001/1kHz<br />

0.005/1kHz<br />

100<br />

25<br />

–<br />

1 – 2<br />

2 – 5<br />

50<br />

18

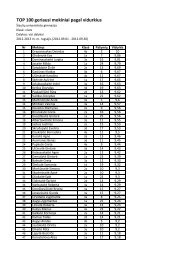

Pramoninė elektronika. 10 paskaita "<strong>Loginiai</strong> <strong>elementai</strong>"<br />

Loginių elementų mikroschemų<br />

žymėjimas Rytuose ir Vakaruose<br />

19<br />

Pramoninė elektronika. 10 paskaita "<strong>Loginiai</strong> <strong>elementai</strong>"<br />

Paskaitos medžiaga parengta pagal: R. Kirvaitis. Loginės schemos. –Vilnius: Enciklopedija, 1999. – 256 p.<br />

20