- Page 1 and 2:

System Generator for DSP リファ

- Page 3 and 4:

目次 このマニュアルにつ

- Page 5 and 6:

目次 ブロック インターフ

- Page 7 and 8:

目次 ブロック パラ メー

- Page 9 and 10:

目次 ブロック パラ メー

- Page 11 and 12:

目次 ザイ リ ンクス LogiCOR

- Page 13 and 14:

目次 CORDIC DIVIDER . . . . . . .

- Page 15 and 16:

目次 xlGenerateButton . . . . . .

- Page 17 and 18:

目次 メンバー データ . . .

- Page 19 and 20:

R このマニュアルについて

- Page 21 and 22:

表記規則 オンライン マニ

- Page 23 and 24:

R ザイリンクス ブロック

- Page 25 and 26:

ブロックセッ ト ラ イ ブ

- Page 27 and 28:

ブロックセッ ト ラ イ ブ

- Page 29 and 30:

ブロックセッ ト ラ イ ブ

- Page 31 and 32:

ブロックセッ ト ラ イ ブ

- Page 33 and 34:

ブロックセッ ト ラ イ ブ

- Page 35 and 36:

ブロックセッ ト ラ イ ブ

- Page 37 and 38:

ブロックセッ ト ラ イ ブ

- Page 39 and 40:

ブロックセッ ト ラ イ ブ

- Page 41 and 42:

ブロックセッ ト ラ イ ブ

- Page 43 and 44:

ブロックセッ ト ラ イ ブ

- Page 45 and 46:

ブロックセッ ト ラ イ ブ

- Page 47 and 48:

ブロックのパラメータ ダ

- Page 49 and 50:

ブロックのパラメータ ダ

- Page 51 and 52:

Accumulator Accumulator このブ

- Page 53 and 54:

Addressable Shift Register Addressa

- Page 55 and 56:

AddSub AddSub ブロック パラ

- Page 57 and 58:

Assert Assert ブロック パラ

- Page 59 and 60:

BitBasher BitBasher このブロッ

- Page 61 and 62:

BitBasher 制限 octal_const : 0、

- Page 63 and 64:

Black Box レート を生成する

- Page 65 and 66:

Black Box • 必要なポー ト

- Page 67 and 68:

Black Box ブロック パラ メ

- Page 69 and 70:

Black Box 例 関連項目 次は

- Page 71 and 72:

ChipScope ブロック パラ メ

- Page 73 and 74:

ChipScope 既知の問題 詳細情

- Page 75 and 76:

Clock Enable Probe Clock Enable Pro

- Page 77 and 78:

CMult CMult ブロック パラ メ

- Page 79 and 80:

Concat Concat このブロックは

- Page 81 and 82:

Configurable Subsystem Manager ブ

- Page 83 and 84:

Constant • [Operation select] : D

- Page 85 and 86:

Convert Convert このブロック

- Page 87 and 88:

Convolutional Encoder v3_0 System G

- Page 89 and 90:

Convolutional Encoder v6_0 System G

- Page 91 and 92:

Counter System Generator ブロッ

- Page 93 and 94:

DAFIR v9_0 係数の リ ロー ド

- Page 95 and 96:

DAFIR v9_0 System Generator ブロ

- Page 97 and 98:

DDS Compiler v1_1 ブロック イ

- Page 99 and 100:

DDS Compiler v1_1 System Generator

- Page 101 and 102:

DDS Compiler v2_0 ブロック イ

- Page 103 and 104:

DDS Compiler v2_0 System Generator

- Page 105 and 106:

DDS v4_0 System Generator ブロッ

- Page 107 and 108:

DDS v5_0 ブロック パラ メー

- Page 109 and 110:

Delay Delay このブロックは

- Page 111 and 112:

Delay 最初の SRL では 16 サ

- Page 113 and 114:

Delay ら ないので、速度が

- Page 115 and 116:

Depuncture ブロック パラ メ

- Page 117 and 118:

Down Sample Down Sample このブ

- Page 119 and 120:

Down Sample フ レームの最後

- Page 121 and 122:

DSP48 • [Provide C port] : オン

- Page 123 and 124:

DSP48 Macro DSP48 Macro このブ

- Page 125 and 126:

DSP48 Macro • 次の図は、 [In

- Page 127 and 128:

DSP48 Macro 予約ポー ト名 ポ

- Page 129 and 130:

DSP48 Macro モードの選択 DSP4

- Page 131 and 132:

DSP48 Macro DSP48 Macro の擬似 o

- Page 133 and 134:

DSP48A DSP48A このブロックは

- Page 135 and 136:

DSP48A 関連項目 • [Reset port

- Page 137 and 138:

DSP48E • [Pattern mask (48 bit he

- Page 139 and 140:

DSP48E • [Reset port for c] : オ

- Page 141 and 142:

Dual Port RAM Dual Port RAM この

- Page 143 and 144:

Dual Port RAM コリジョン ビ

- Page 145 and 146:

Dual Port RAM System Generator ブ

- Page 147 and 148:

EDK Processor EDK Processor この

- Page 149 and 150:

EDK Processor 既知の問題 •

- Page 151 and 152:

FDATool FDATool 使用例 このブ

- Page 153 and 154:

FFT v1_0 FFT v1_0 このブロッ

- Page 155 and 156:

FFT v1_0 FFT のタイ ミング特

- Page 157 and 158:

FFT v3_1 FFT v3_1 このブロッ

- Page 159 and 160:

FFT v3_1 nfft_we アサート さ

- Page 161 and 162:

FFT v3_1 System Generator ブロッ

- Page 163 and 164:

FFT v3_2 入力信号 xn_re 入力

- Page 165 and 166:

FFT v3_2 • [Output ordering] :

- Page 167 and 168:

FFT v4_1 FFT v4_1 このブロッ

- Page 169 and 170:

FFT v4_1 出力信号 ブロック

- Page 171 and 172:

FFT v4_1 System Generator ブロッ

- Page 173 and 174:

FIR Compiler v1_0 FIR Compiler v1_0

- Page 175 and 176:

FIR Compiler v1_0 タ コ ン フ

- Page 177 and 178:

FIR Compiler v2_0 FIR Compiler v2_0

- Page 179 and 180:

FIR Compiler v2_0 ブロック パ

- Page 181 and 182:

FIR Compiler v2_0 System Generator

- Page 183 and 184:

FIR Compiler v3_0 係数の リ ロ

- Page 185 and 186:

FIR Compiler v3_0 対称イ ン タ

- Page 187 and 188:

FIR Compiler v3_0 既知の問題

- Page 189 and 190:

FIR Compiler v3_1 係数の リ ロ

- Page 191 and 192:

FIR Compiler v3_1 対称イ ン タ

- Page 193 and 194:

FIR Compiler v3_1 System Generator

- Page 195 and 196:

From FIFO System Generator ブロ

- Page 197 and 198:

From Register 関連項目 Domain_B

- Page 199 and 200:

Gateway In ば、次の OFFSET = IN

- Page 201 and 202:

Gateway Out とえば、次の OFFS

- Page 203 and 204:

Interleaver Deinterleaver v4_0 Inte

- Page 205 and 206:

Interleaver Deinterleaver v4_0 Syst

- Page 207 and 208:

Interleaver Deinterleaver v5_0 ブ

- Page 209 and 210:

Inverter Inverter このブロッ

- Page 211 and 212:

JTAG Co-Simulation [Advanced] タ

- Page 213 and 214:

LFSR す。 [Galois] を 選択す

- Page 215 and 216:

MCode MCode このブロックは

- Page 217 and 218:

MCode • 比較演算子 < より

- Page 219 and 220:

MCode 定数式 これが使用で

- Page 221 and 222:

MCode スライス関数 : xl_slice

- Page 223 and 224:

MCode empty = v.empty; ベク タ

- Page 225 and 226:

MCode disp('disp(10) is'); disp(10)

- Page 227 and 228:

MCode end regs.push_front_pop_back(

- Page 229 and 230:

MCode Simulink のシ ミ ュ レ

- Page 231 and 232:

MCode 次の図は、 モデルを

- Page 233 and 234:

MCode end persistent ス テー ト

- Page 235 and 236:

MCode 丸めを使用し た xl_sta

- Page 237 and 238:

MicroBlaze Processor ポー ト 各

- Page 239 and 240:

MicroBlaze Processor ブロック

- Page 241 and 242:

MicroBlaze Processor MicroBlaze ソ

- Page 243 and 244:

MicroBlaze Processor 既知の問

- Page 245 and 246:

ModelSim ModelSim このブロッ

- Page 247 and 248:

ModelSim タイム スケール カ

- Page 249 and 250:

ModelSim 上の図は、 System Gen

- Page 251 and 252:

Multiple Subsystem Generator Multip

- Page 253 and 254:

Multiple Subsystem Generator Genera

- Page 255 and 256:

Multiple Subsystem Generator 生成

- Page 257 and 258:

Negate Negate ブロック パラ

- Page 259 and 260:

Network-based Ethernet Co-Simulatio

- Page 261 and 262:

Opmode PCIN)] の場合は、 キ

- Page 263 and 264:

Parallel to Serial Parallel to Seri

- Page 265 and 266:

PicoBlaze Instruction Display PicoB

- Page 267 and 268:

PicoBlaze Microcontroller • [Disp

- Page 269 and 270:

Point-to-point Ethernet Co-Simulati

- Page 271 and 272:

Puncture このブロックで使

- Page 273 and 274:

Reinterpret Reinterpret このブ

- Page 275 and 276:

Resource Estimator Resource Estimat

- Page 277 and 278:

Resource Estimator 既知の問題

- Page 279 and 280:

ROM • [Binary point] : メモリ

- Page 281 and 282:

RS Decoder v5_1 RS Decoder v5_1 こ

- Page 283 and 284:

RS Decoder v5_1 ♦ [Custom] : ブ

- Page 285 and 286:

RS Decoder v6_0 RS Decoder v6_0 こ

- Page 287 and 288:

RS Decoder v6_0 ♦ [ATSC] : ATSC (

- Page 289 and 290:

RS Encoder v5_0 RS Encoder v5_0 こ

- Page 291 and 292:

RS Encoder v5_0 ♦ [CCSDS] : CCSDS

- Page 293 and 294:

RS Encoder v6_0 RS Encoder v6_0 こ

- Page 295 and 296:

RS Encoder v6_0 ♦ [CCSDS] : CCSDS

- Page 297 and 298:

Sample Time Sample Time このブ

- Page 299 and 300:

Serial to Parallel Serial to Parall

- Page 301 and 302:

Shared Memory 実行で き る よ

- Page 303 and 304:

Shared Memory Memory ブロッ ク

- Page 305 and 306:

Shared Memory Read ブロック パ

- Page 307 and 308:

Shared Memory Write ブロック

- Page 309 and 310:

Simulation Multiplexer Simulation M

- Page 311 and 312:

SineCosine SineCosine このブロ

- Page 313 and 314:

Single Port RAM Single Port RAM こ

- Page 315 and 316:

Single Port RAM 書き込みモー

- Page 317 and 318:

Single Port RAM 深さ別の最大

- Page 319 and 320:

Single-Step Simulation Single-Step

- Page 321 and 322:

System Generator System Generator

- Page 323 and 324:

System Generator ♦ [Default] :

- Page 325 and 326:

System Generator ♦ [Input data ty

- Page 327 and 328:

Time Division Demultiplexer Time Di

- Page 329 and 330:

Time Division Multiplexer Time Divi

- Page 331 and 332:

To FIFO System Generator ブロッ

- Page 333 and 334:

To Register クロック ド メ

- Page 335 and 336:

Toolbar ツールバー メニュ

- Page 337 and 338:

Up Sample Up Sample このブロッ

- Page 339 and 340:

Viterbi Decoder v5_0 Viterbi Decode

- Page 341 and 342:

Viterbi Decoder v5_0 System Generat

- Page 343 and 344:

Viterbi Decoder v6_0 ます。 sel

- Page 345 and 346: WaveScope WaveScope このブロッ

- Page 347 and 348: WaveScope [hex] をオンにし、

- Page 349 and 350: WaveScope 2 つ目の選択方法

- Page 351 and 352: WaveScope ク リ ッ ク する

- Page 353 and 354: WaveScope マウス ポ イ ン タ

- Page 355 and 356: WaveScope [Move Cursor Last] 一番

- Page 357 and 358: Xilinx LogiCORE のバージ ョ

- Page 359 and 360: Xilinx LogiCORE のバージ ョ

- Page 361 and 362: R 第 2 章 ザイ リンクス リ

- Page 363 and 364: 2 Channel Decimate by 2 MAC FIR Fil

- Page 365 and 366: 2n-tap Linear Phase MAC FIR Filter

- Page 367 and 368: 4-channel 8-tap Transpose FIR Filte

- Page 369 and 370: 5x5Filter 5x5Filter 5 つの n-tap

- Page 371 and 372: BPSK AWGN Channel BPSK AWGN Channel

- Page 373 and 374: CIC Filter ブロック パラ メ

- Page 375 and 376: Convolutional Encoder ブロック

- Page 377 and 378: CORDIC DIVIDER CORDIC DIVIDER ブ

- Page 379 and 380: CORDIC LOG 参考資料 1. J. E. Vo

- Page 381 and 382: CORDIC SQRT CORDIC SQRT Hyperbolic

- Page 383 and 384: Dual Port Memory Interpolation MAC

- Page 385 and 386: m-channel n-tap Transpose FIR Filte

- Page 387 and 388: Mealy State Machine 例 ミーリ

- Page 389 and 390: Moore State Machine Moore State Mac

- Page 391 and 392: Moore State Machine マ ト リ ッ

- Page 393 and 394: Multipath Fading Channel Model イ

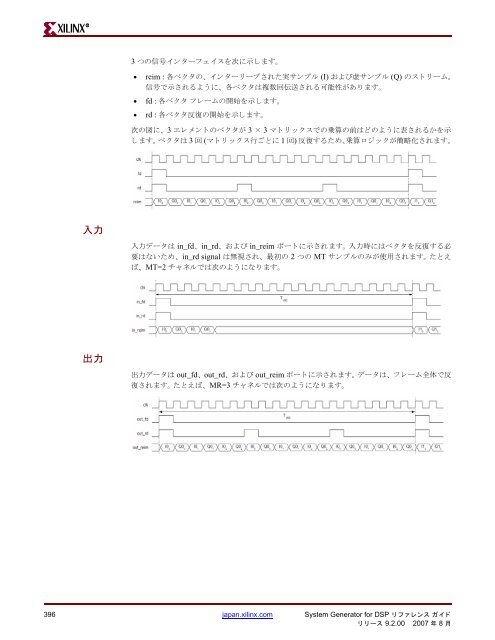

- Page 395: Multipath Fading Channel Model デ

- Page 399 and 400: n-tap Dual Port Memory MAC FIR Filt

- Page 401 and 402: Registered Mealy State Machine Regi

- Page 403 and 404: Registered Mealy State Machine ブ

- Page 405 and 406: Registered Moore State Machine 例

- Page 407 and 408: Virtex Line Buffer Virtex Line Buff

- Page 409 and 410: Virtex2 5 Line Buffer Virtex2 5 Lin

- Page 411 and 412: White Gaussian Noise Generator Box-

- Page 413 and 414: R ザイリンクス XtremeDSP キ

- Page 415 and 416: XtremeDSP Co-simulation XtremeDSP C

- Page 417 and 418: XtremeDSP DAC XtremeDSP DAC モデ

- Page 419 and 420: XtremeDSP LED Flasher XtremeDSP LED

- Page 421 and 422: R System Generator ユーテ ィ

- Page 423 and 424: xlAddTerms optionStruct 引数は

- Page 425 and 426: xlAddTerms 関連項目 「Toolbar

- Page 427 and 428: xlfda_numerator xlfda_numerator 構

- Page 429 and 430: xlgetparam および xlsetparam xlg

- Page 431 and 432: xlInstallPlugin xlInstallPlugin 構

- Page 433 and 434: xlSetNonMemMap xlSetNonMemMap 構

- Page 435 and 436: xlSBDBuilder xlSBDBuilder 構文

- Page 437 and 438: xlTBUtils 例 フィールド名

- Page 439 and 440: xlTimingAnalysis xlTimingAnalysis

- Page 441 and 442: xlUpdateModel ♦ 加えた変更

- Page 443 and 444: xlVersion xlVersion 構文 説明

- Page 445 and 446: R プログラムを使用したア

- Page 447 and 448:

プ ログ ラムを使用し た

- Page 449 and 450:

SharedMemory SharedMemory Public

- Page 451 and 452:

SharedMemory パラ メータ name

- Page 453 and 454:

SharedMemory 戻り値 読み出し

- Page 455 and 456:

LockableSharedMemory LockableShared

- Page 457 and 458:

LockableSharedMemory 戻り値 arg

- Page 459 and 460:

SharedMemoryProxy SharedMemoryProxy

- Page 461 and 462:

SharedMemoryProxy Sysgen::StdLogicV

- Page 463 and 464:

NamedPipeReader NamedPipeReader Pub

- Page 465 and 466:

NamedPipeReader unsigned getNWords

- Page 467 and 468:

NamedPipeWriter メンバー関数

- Page 469 and 470:

索引 数字 2 Channel Decimate by

- Page 471 and 472:

索引 さ ザイ リンクス Logi