power monitors are on an independent i2c bus - Spectrum Digital ...

power monitors are on an independent i2c bus - Spectrum Digital ...

power monitors are on an independent i2c bus - Spectrum Digital ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

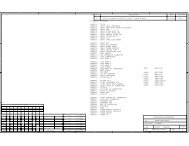

54321EACH DATA GROUP IS MATCHED WITHIN THE GROUPdifferential pairs 100 ohm5 placesU42-5DCBData Group 0-0USE 4X SPACING TRACETO TRACE EQUAL LENGTH+/-5 MILData Group 0-1USE 4X SPACING TRACETO TRACE EQUAL LENGTH+/-5 MILData Group 0-2USE 4X SPACING TRACETO TRACE EQUAL LENGTH+/-5 MILData Group 0-3USE 4X SPACING TRACETO TRACE EQUAL LENGTH+/-5 MIL37 DDR0_DQM037 DDR0_DQS037 DDR0_DQSN037 DDR0_D037 DDR0_D137 DDR0_D237 DDR0_D337 DDR0_D437 DDR0_D537 DDR0_D637 DDR0_D737 DDR0_DQM137 DDR0_DQS137 DDR0_DQSN137 DDR0_D837 DDR0_D937 DDR0_D1037 DDR0_D1137 DDR0_D1237 DDR0_D1337 DDR0_D1437 DDR0_D1537 DDR0_DQM237 DDR0_DQS237 DDR0_DQSN237 DDR0_D1637 DDR0_D1737 DDR0_D1837 DDR0_D1937 DDR0_D2037 DDR0_D2137 DDR0_D2237 DDR0_D2337 DDR0_DQM337 DDR0_DQS337 DDR0_DQSN337 DDR0_D2437 DDR0_D2537 DDR0_D2637 DDR0_D2737 DDR0_D2837 DDR0_D2937 DDR0_D3037 DDR0_D31DDR0_DQM0DDR0_DQS0DDR0_DQSN0DDR0_D0DDR0_D1DDR0_D2DDR0_D3DDR0_D4DDR0_D5DDR0_D6DDR0_D7DDR0_DQM1DDR0_DQS1DDR0_DQSN1DDR0_D8DDR0_D9DDR0_D10DDR0_D11DDR0_D12DDR0_D13DDR0_D14DDR0_D15DDR0_DQM2DDR0_DQS2DDR0_DQSN2DDR0_D16DDR0_D17DDR0_D18DDR0_D19DDR0_D20DDR0_D21DDR0_D22DDR0_D23DDR0_DQM3DDR0_DQS3DDR0_DQSN3DDR0_D24DDR0_D25DDR0_D26DDR0_D27DDR0_D28DDR0_D29DDR0_D30DDR0_D31C2E2E1D3E4D2C1E3F2F4F1F3H2H1G3G2G1G4H3J1H4J2J4L1L2J3K4K3L4L3M4M2M3M1P2P1N4N1N2N3P3R3P4R4DDR[0]_DQM[0]DDR[0]_DQS[0]DDR[0]_DQS[0]NDDR[0]_D[0]DDR[0]_D[1]DDR[0]_D[2]DDR[0]_D[3]DDR[0]_D[4]DDR[0]_D[5]DDR[0]_D[6]DDR[0]_D[7]DDR[0]_DQM[1]DDR[0]_DQS[1]DDR[0]_DQS[1]NDDR[0]_D[8]DDR[0]_D[9]DDR[0]_D[10]DDR[0]_D[11]DDR[0]_D[12]DDR[0]_D[13]DDR[0]_D[14]DDR[0]_D[15]DDR[0]_DQM[2]DDR[0]_DQS[2]DDR[0]_DQS[2]NDDR[0]_D[16]DDR[0]_D[17]DDR[0]_D[18]DDR[0]_D[19]DDR[0]_D[20]DDR[0]_D[21]DDR[0]_D[22]DDR[0]_D[23]DDR[0]_DQM[3]DDR[0]_DQS[3]DDR[0]_DQS[3]NDDR[0]_D[24]DDR[0]_D[25]DDR[0]_D[26]DDR[0]_D[27]DDR[0]_D[28]DDR[0]_D[29]DDR[0]_D[30]DDR[0]_D[31]DDR[0]_BA[0]DDR[0]_BA[1]DDR[0]_BA[2]DDR[0]_A[0]DDR[0]_A[1]DDR[0]_A[2]DDR[0]_A[3]DDR[0]_A[4]DDR[0]_A[5]DDR[0]_A[6]DDR[0]_A[7]DDR[0]_A[8]DDR[0]_A[9]DDR[0]_A[10]DDR[0]_A[11]DDR[0]_A[12]DDR[0]_A[13]DDR[0]_A[14]DDR[0]_A[15]DDR[0]_CS[0]NDDR[0]_RASNDDR[0]_CASNDDR[0]_ODT[0]DDR[0]_WENDDR[0]_RSTDDR[0]_CLKDDR[0]_CLKNDDR[0]_CKEDDR[0]_VTPVREFSSTL_DDR[0]Y4V5U4DDR0_BA0DDR0_BA1DDR0_BA2W4 DDR0_A0U2 DDR0_A1V3 DDR0_A2AA1 DDR0_A3AA2 DDR0_A4V4 DDR0_A5AB3 DDR0_A6T4 DDR0_A7AA3 DDR0_A8AA4 DDR0_A9V2 DDR0_A10W2 DDR0_A11U3U5V1T5T3W5Y3U1W3T2Y2Y1T1P5M5DDR0_A12DDR0_A13DDR0_A14DDR0_A15DDR0_CSN0DDR0_ODT0DDR0_WENDDR0_RSTDDR_VREFSSTLDDR0_CLK0DDR0_CLK0NDDR0_CKER481 49.9DDR0_BA0 36,37,39DDR0_BA1 36,37,39DDR0_BA2 36,37,39DDR0_A0 36,37,39DDR0_A1 36,37,39DDR0_A2 36,37,39DDR0_A3 36,37,39DDR0_A4 36,37,39DDR0_A5 36,37,39DDR0_A6 36,37,39DDR0_A7 36,37,39DDR0_A8 36,37,39DDR0_A9 36,37,39DDR0_A10 36,37,39DDR0_A11 36,37,39DDR0_A12 36,37,39DDR0_A13 36,37,39DDR0_A14 36,37,39DDR0_A15 36,37,39DDR0_CSN0 36,37,39DDR0_RASN 36,37,39DDR0_CASN 36,37,39DDR0_ODT0 36,37,39DDR0_WEN 36,37,39DDR0_RST 37DDR0_CLK0 36,37,39DDR0_CLK0N 36,37,39DDR0_CKE 36,37,39DDR_VREFSSTL 37,57CONTROL GROUP 0USE 4X SPACING TRACETO TRACE EQUAL LENGTH+/-5 MILDDR0_RST is not part of groupCLOCK GROUP 0CONTROL GROUP 0DDR_VREFSSTL is not part of groupDCBJ5_ECO_PARTC3840.1uFATEXAS INSTRUMENTS INCORPORATEDADDR_VREFSSTLDDR_VREFSSTLDDR_VREFSSTL 37,57Title:Page C<strong>on</strong>tents:Size: BJ5 ECO EVMDDR EMIF 0DWG NO 515062-0001Revisi<strong>on</strong>:ADate: M<strong>on</strong>day, J<strong>an</strong>uary 16, 2012 Sheet 18 o f 6454321