3 レベルのマルチレベル方式の半導体素子に 発生 ... - 長岡技術科学大学

3 レベルのマルチレベル方式の半導体素子に 発生 ... - 長岡技術科学大学 3 レベルのマルチレベル方式の半導体素子に 発生 ... - 長岡技術科学大学

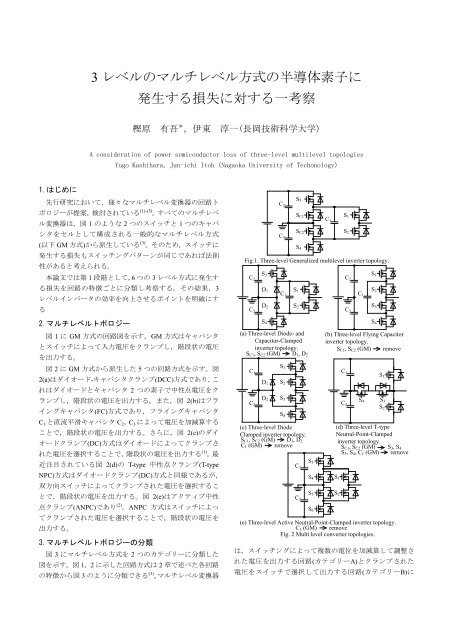

3 レベルのマルチレベル 方 式 の 半 導 体 素 子 に 発 生 する 損 失 に 対 する 一 考 察 樫 原 有 吾 * , 伊 東 淳 一 ( 長 岡 技 術 科 学 大 学 ) A consideration of power semiconductor loss of three-level multilevel topologies Yugo Kashihara, Jun-ichi Itoh (Nagaoka University of Techonology) 1.はじめに 先 行 研 究 において, 様 々なマルチレベル 変 換 器 の 回 路 ト ポロジーが 提 案 , 検 討 されている (1)-(3) 。すべてのマルチレベ ル 変 換 器 は, 図 1 のような 2 つのスイッチと 1 つのキャパ シタをセルとして 構 成 される 一 般 的 なマルチレベル 方 式 ( 以 下 GM 方 式 )から 派 生 している (3) 。そのため,スイッチに 発 生 する 損 失 もスイッチングパターンが 同 じであれば 法 則 性 があると 考 えられる。 本 論 文 では 第 1 段 階 として,6 つの 3 レベル 方 式 に 発 生 す る 損 失 を 回 路 の 特 徴 ごとに 分 類 し 考 察 する。その 結 果 ,3 レベルインバータの 効 率 を 向 上 させるポイントを 明 確 にす る 2.マルチレベルトポロジー 図 1 に GM 方 式 の 回 路 図 を 示 す。GM 方 式 はキャパシタ とスイッチによって 入 力 電 圧 をクランプし, 階 段 状 の 電 圧 を 出 力 する。 図 2 に GM 方 式 から 派 生 した 5 つの 回 路 方 式 を 示 す。 図 2(a)はダイオード-キャパシタクランプ(DCC) 方 式 であり,こ れはダイオードとキャパシタ 2 つの 素 子 で 中 性 点 電 圧 をク ランプし, 階 段 状 の 電 圧 を 出 力 する。また, 図 2(b)はフラ イングキャパシタ(FC) 方 式 であり,フライングキャパシタ C 1 と 直 流 平 滑 キャパシタ C 2 ,C 3 によって 電 圧 を 加 減 算 する ことで, 階 段 状 の 電 圧 を 出 力 する。さらに, 図 2(c)のダイ オードクランプ(DC) 方 式 はダイオードによってクランプさ れた 電 圧 を 選 択 することで, 階 段 状 の 電 圧 を 出 力 する (1) 。 最 近 注 目 されている 図 2(d)の T-type 中 性 点 クランプ(T-type NPC) 方 式 はダイオードクランプ(DC) 方 式 と 同 様 であるが, 双 方 向 スイッチによってクランプされた 電 圧 を 選 択 するこ とで, 階 段 状 の 電 圧 を 出 力 する。 図 2(e)はアクティブ 中 性 点 クランプ(ANPC)であり (2) ,ANPC 方 式 はスイッチによっ てクランプされた 電 圧 を 選 択 することで, 階 段 状 の 電 圧 を 出 力 する。 3.マルチレベルトポロジーの 分 類 図 3 にマルチレベル 方 式 を 2 つのカテゴリーに 分 類 した 図 を 示 す。 図 1,2 に 示 した 回 路 方 式 は 2 章 で 述 べた 各 回 路 の 特 徴 から 図 3 のように 分 類 できる (3) 。マルチレベル 変 換 器 C 2 S 3 S C1 S 1 C 1 S C2 S 2 C 3 S 4 Fig.1. Three-level Generalized multilevel inverter topology. S 3 S 1 C 2 C 2 D 1 S 2 C 1 D 2 C 3 S 2 C 1 S 1 S 4 (a) Three-level Diode- and Capacitor-Clamped (b) Three-level Flying Capacitor inverter topology. inverter topology. S C1 , S C2 (GM) D 1 , D 2 S C1 , S C2 (GM) remove S 1 C 1 C 1 S 1 D 1 S 2 D 2 S 3 S S C 4 3 2 C 2 S 2 S 4 (c) Three-level Diode (d) Three-level T-type Clamped inverter topology. Neutral-Point-Clamped S C1 , S C2 (GM) D 1 , D 2 inverter topology. C 1 (GM) remove S C1 , S C2 (GM) S 3 , S 4 S 3 , S 4 , C 1 (GM) remove C 1 C 2 S 3 S 4 S 5 S 6 (e) Three-level Active Neutral-Point-Clamped inverter topology. C 1 (GM) remove Fig. 2 Multi level converter topologies. は,スイッチングによって 複 数 の 電 位 を 加 減 算 して 調 整 さ れた 電 圧 を 出 力 する 回 路 (カテゴリーA)とクランプされた 電 圧 をスイッチで 選 択 して 出 力 する 回 路 (カテゴリーB)に S 1 S 2 C 3 S 3 S 4

- Page 2: 分 けることができる。FC

3 レベルのマルチレベル 方 式 の 半 導 体 素 子 に<br />

発 生 する 損 失 に 対 する 一 考 察<br />

樫 原 有 吾 * , 伊 東 淳 一 ( 長 岡 技 術 科 学 大 学 )<br />

A consideration of power semiconductor loss of three-level multilevel topologies<br />

Yugo Kashihara, Jun-ichi Itoh (Nagaoka University of Techonology)<br />

1.はじめに<br />

先 行 研 究 において, 様 々なマルチレベル 変 換 器 の 回 路 ト<br />

ポロジーが 提 案 , 検 討 されている (1)-(3) 。すべてのマルチレベ<br />

ル 変 換 器 は, 図 1 のような 2 つのスイッチと 1 つのキャパ<br />

シタをセルとして 構 成 される 一 般 的 なマルチレベル 方 式<br />

( 以 下 GM 方 式 )から 派 生 している (3) 。そのため,スイッチに<br />

発 生 する 損 失 もスイッチングパターンが 同 じであれば 法 則<br />

性 があると 考 えられる。<br />

本 論 文 では 第 1 段 階 として,6 つの 3 レベル 方 式 に 発 生 す<br />

る 損 失 を 回 路 の 特 徴 ごとに 分 類 し 考 察 する。その 結 果 ,3<br />

レベルインバータの 効 率 を 向 上 させるポイントを 明 確 にす<br />

る<br />

2.マルチレベルトポロジー<br />

図 1 に GM 方 式 の 回 路 図 を 示 す。GM 方 式 はキャパシタ<br />

とスイッチによって 入 力 電 圧 をクランプし, 階 段 状 の 電 圧<br />

を 出 力 する。<br />

図 2 に GM 方 式 から 派 生 した 5 つの 回 路 方 式 を 示 す。 図<br />

2(a)はダイオード-キャパシタクランプ(DCC) 方 式 であり,こ<br />

れはダイオードとキャパシタ 2 つの 素 子 で 中 性 点 電 圧 をク<br />

ランプし, 階 段 状 の 電 圧 を 出 力 する。また, 図 2(b)はフラ<br />

イングキャパシタ(FC) 方 式 であり,フライングキャパシタ<br />

C 1 と 直 流 平 滑 キャパシタ C 2 ,C 3 によって 電 圧 を 加 減 算 する<br />

ことで, 階 段 状 の 電 圧 を 出 力 する。さらに, 図 2(c)のダイ<br />

オードクランプ(DC) 方 式 はダイオードによってクランプさ<br />

れた 電 圧 を 選 択 することで, 階 段 状 の 電 圧 を 出 力 する (1) 。 最<br />

近 注 目 されている 図 2(d)の T-type 中 性 点 クランプ(T-type<br />

NPC) 方 式 はダイオードクランプ(DC) 方 式 と 同 様 であるが,<br />

双 方 向 スイッチによってクランプされた 電 圧 を 選 択 するこ<br />

とで, 階 段 状 の 電 圧 を 出 力 する。 図 2(e)はアクティブ 中 性<br />

点 クランプ(ANPC)であり (2) ,ANPC 方 式 はスイッチによっ<br />

てクランプされた 電 圧 を 選 択 することで, 階 段 状 の 電 圧 を<br />

出 力 する。<br />

3.マルチレベルトポロジーの 分 類<br />

図 3 にマルチレベル 方 式 を 2 つのカテゴリーに 分 類 した<br />

図 を 示 す。 図 1,2 に 示 した 回 路 方 式 は 2 章 で 述 べた 各 回 路<br />

の 特 徴 から 図 3 のように 分 類 できる (3) 。マルチレベル 変 換 器<br />

C 2<br />

S 3<br />

S C1<br />

S 1<br />

C 1<br />

S C2<br />

S 2<br />

C 3<br />

S 4<br />

Fig.1. Three-level Generalized multilevel inverter topology.<br />

S 3<br />

S 1<br />

C 2 C 2<br />

D 1<br />

S 2<br />

C 1<br />

D 2<br />

C 3<br />

S 2<br />

C 1<br />

S 1<br />

S 4<br />

(a) Three-level Diode- and<br />

Capacitor-Clamped<br />

(b) Three-level Flying Capacitor<br />

inverter topology.<br />

inverter topology.<br />

S C1 , S C2 (GM) D 1 , D 2<br />

S C1 , S C2 (GM) remove<br />

S 1<br />

C 1<br />

C 1<br />

S 1<br />

D 1 S 2<br />

D 2 S 3<br />

S S<br />

C 4 3<br />

2 C 2<br />

S 2<br />

S 4<br />

(c) Three-level Diode<br />

(d) Three-level T-type<br />

Clamped inverter topology. Neutral-Point-Clamped<br />

S C1 , S C2 (GM) D 1 , D 2 inverter topology.<br />

C 1 (GM) remove<br />

S C1 , S C2 (GM) S 3 , S 4<br />

S 3 , S 4 , C 1 (GM) remove<br />

C 1<br />

C 2<br />

S 3<br />

S 4<br />

S 5<br />

S 6<br />

(e) Three-level Active Neutral-Point-Clamped inverter topology.<br />

C 1 (GM) remove<br />

Fig. 2 Multi level converter topologies.<br />

は,スイッチングによって 複 数 の 電 位 を 加 減 算 して 調 整 さ<br />

れた 電 圧 を 出 力 する 回 路 (カテゴリーA)とクランプされた<br />

電 圧 をスイッチで 選 択 して 出 力 する 回 路 (カテゴリーB)に<br />

S 1<br />

S 2<br />

C 3<br />

S 3<br />

S 4

分 けることができる。FC 方 式 は,フライングキャパシタの<br />

電 位 の 加 減 算 を 行 い 任 意 の 電 圧 に 調 整 して 電 圧 を 出 力 する<br />

ため,カテゴリーA に 分 類 できる。 一 方 で,DC 方 式 や T-type<br />

NPC 方 式 ,ANPC 方 式 はクランプされている 電 圧 から 任 意<br />

の 電 圧 を 選 択 するためカテゴリーB に 分 類 できる。GM 方 式<br />

や DCC 方 式 は, 他 の 方 式 と 比 較 してクランプ 素 子 が 複 数 有<br />

り,スイッチングの 自 由 度 が 高 いため,カテゴリーA,B 両<br />

方 の 動 作 を 取 ることができる。<br />

4.マルチレベル 変 換 器 の 半 導 体 素 子 の 損 失<br />

変 調 方 式 を 位 相 が 異 なる 複 数 のキャリアを 用 いた 位 相 シ<br />

フト 変 調 方 式 とすると,カテゴリーA の 変 調 波 A は(1) 式 で<br />

得 られる。<br />

asin<br />

................................................................. (1)<br />

A<br />

ここで,a は 変 調 率 ,は 出 力 電 流 位 相 である。 一 方 で,<br />

カテゴリーB の 変 調 率 は(2) 式 となる。<br />

asin<br />

when 0 <br />

B <br />

.................... (2)<br />

asin<br />

1<br />

when 2<br />

変 換 器 の 半 導 体 素 子 に 発 生 する 損 失 P loss は 次 式 で 表 すこ<br />

とができる (4) 。<br />

P<br />

loss<br />

P P .....................................................(3)<br />

con<br />

sw<br />

ここで,P con は 導 通 損 失 ,P sw はスイッチング 損 失 である。<br />

スイッチの 導 通 損 失 の 平 均 値 P con はスイッチのオン 電 圧<br />

とスイッチに 流 れる 電 流 から 導 出 することができ(4) 式 ,(5)<br />

式 にて 表 せる。<br />

P<br />

v<br />

Switch<br />

on<br />

1<br />

<br />

2<br />

<br />

<br />

v i d<br />

..........................................(4)<br />

on sw<br />

<br />

r I .....................................................(5)<br />

on<br />

v 0<br />

ここで,v on はスイッチのオン 電 圧 ,i Sw は 素 子 に 流 れる 電<br />

流 ,とは 電 流 の 流 れている 期 間 ,r on はスイッチのオン 抵<br />

抗 ,v 0 は 0A の 時 のオン 電 圧 降 下 である。<br />

出 力 周 波 数 1 周 期 あたりのスイッチング 損 失 は, 次 式 で<br />

表 すことができる。<br />

P<br />

Switch<br />

Vdc<br />

<br />

n 1<br />

1 y<br />

e<br />

on<br />

eoff<br />

f<br />

sw x<br />

2<br />

i<br />

out<br />

d<br />

.................... (6)<br />

ここで,V dc は 入 力 電 圧 ,n はレベル 数 ,e on ,e off は 瞬 時 タ<br />

ーンオン/オフエネルギー,f sw はスイッチング 周 波 数 ,x と<br />

y は 電 流 が 正 または 負 の 始 まりと 終 わりの 位 相 角 ,i out は 出<br />

力 電 流 である。<br />

5. 回 路 方 式 における 損 失 の 比 較<br />

(1),(4) 式 により, 回 路 条 件 ( 使 用 しているスイッチング 素<br />

子 )が 同 じであれば, 導 通 損 失 は 被 変 調 波 のみに 依 存 し, 回<br />

路 方 式 が 異 なってもカテゴリーA の 回 路 方 式 のスイッチに<br />

発 生 する 導 通 損 失 は 同 じになる。ただ,GM 方 式 ,DCC 方<br />

式 は, 導 通 損 失 やスイッチング 損 失 とは 別 にスイッチング<br />

Power loss S1[W]<br />

0.14<br />

0.12<br />

0.1<br />

0.08<br />

0.06<br />

0.04<br />

0.02<br />

0<br />

FC 方 式<br />

(Fig.3)<br />

カテゴリーA<br />

任 意 電 圧 に 調 整<br />

時 に 横 流 が 発 生 するので,それに 伴 う 損 失 が 発 生 する。し<br />

かし, 横 流 による 損 失 は 他 の 損 失 に 対 して 十 分 小 さく 無 視<br />

できると 仮 定 している。<br />

GM 方 式<br />

(Fig.1)<br />

DCC 方 式<br />

(Fig.2)<br />

図 4 に,カテゴリーA の 回 路 (GM,DCC,FC 方 式 )のスイ<br />

ッチ S1 の 導 通 損 失 を 比 較 した 図 を 示 す。 図 1 より, 全 ての<br />

回 路 方 式 の 導 通 損 失 が 一 致 していることがわかる。<br />

カテゴリーB の 回 路 では, 方 式 毎 に 異 なるスイッチング<br />

テーブルを 持 ち, 回 路 内 のスイッチにおいても 変 調 波 の 波<br />

形 に 対 して 半 周 期 もしくは 1 周 期 全 ての 期 間 で 導 通 するな<br />

どスイッチング 動 作 が 異 なる。しかしながら,それぞれの<br />

方 式 において 電 圧 をクランプする, 出 力 電 圧 を 選 択 するス<br />

イッチの 動 作 を 1 つのスイッチで 担 う,もしくは 1 つのス<br />

イッチで 分 担 して 行 っているため,スイッチのパラメータ<br />

が 同 じ 場 合 , 変 調 波 の 期 間 ごとの 損 失 は 一 致 する (5) 。<br />

これらのことから, 変 換 器 の 変 調 方 式 と 電 圧 の 出 力 方 法<br />

が 同 じであれば, 回 路 方 式 による 効 率 の 際 はスイッチング<br />

素 子 の 性 能 により 決 定 づけられる。 従 って, 回 路 方 式 の 特<br />

性 に 応 じたデバイス 選 定 が 重 要 となる。<br />

今 後 は, 各 方 式 の 電 圧 レベルを 5 として 損 失 を 検 討 し,<br />

マルチレベル 変 換 器 の 損 失 一 般 化 について 検 討 を 行 う。<br />

文 献<br />

カテゴリーB<br />

任 意 電 圧 を 選 択<br />

DC 方 式<br />

(Fig.4)<br />

T-type NPC 方 式<br />

(Fig.5)<br />

ANPC 方 式<br />

(Fig.6)<br />

Fig.3. Category of multilevel topologies.<br />

GM DCC FC<br />

Fig.4 Conduction loss comparison of S1.<br />

Switching loss<br />

Conducsion loss<br />

Calculation condition: Output power 1kW, Input voltage 350V,<br />

Output current 5.1Arms, Duty command 0.8, On-resistance 0.008m,<br />

Power factor 1.<br />

(1) A. Nabae, et.al,:IEEE trans. on I.A. Vol.17, pp.518-523(1981)<br />

(2) P. Barbosa, et.al,:PESC, pp.2296-2301(2005)<br />

(3) F. Z. Peng: IEEE trans. on I.A. Vol.37, pp.611-618(2001)<br />

(4) Y. Kashihara, J. Itoh: CIPS, pp.67-72(2012)<br />

(5) 樫 原 有 吾 , 伊 東 淳 一 , 森 田 一 徳 , 宗 島 正 和 , 小 倉 和 也 :<br />

SPC-12-159(2012)