LEZIONE #05 del 12-Mag-2008 (2 ore) - Dipartimento di Ingegneria ...

LEZIONE #05 del 12-Mag-2008 (2 ore) - Dipartimento di Ingegneria ...

LEZIONE #05 del 12-Mag-2008 (2 ore) - Dipartimento di Ingegneria ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

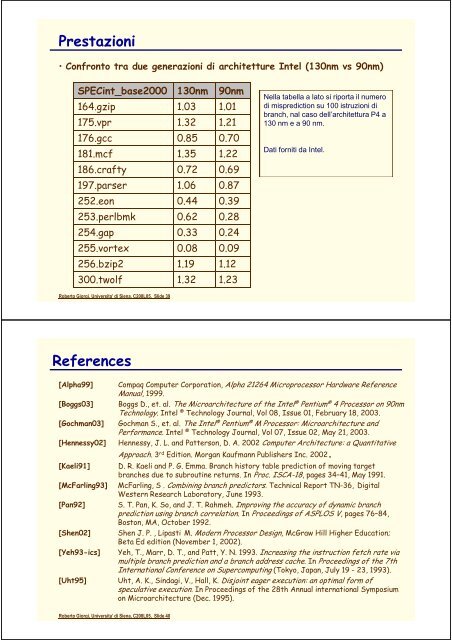

Prestazioni<br />

• Confronto tra due generazioni <strong>di</strong> architetture Intel (130nm vs 90nm)<br />

SPECint_base2000 130nm 90nm<br />

164.gzip 1.03 1.01<br />

175.vpr 1.32 1.21<br />

176.gcc 0.85 0.70<br />

181.mcf 1.35 1.22<br />

186.crafty 0.72 0.69<br />

197.parser 1.06 0.87<br />

252.eon 0.44 0.39<br />

253.perlbmk 0.62 0.28<br />

254.gap 0.33 0.24<br />

255.vortex 0.08 0.09<br />

256.bzip2 1.19 1.<strong>12</strong><br />

300.twolf 1.32 1.23<br />

Roberto Giorgi, Universita’ <strong>di</strong> Siena, C208L05, Slide 39<br />

References<br />

Nella tabella a lato si riporta il numero<br />

<strong>di</strong> mispre<strong>di</strong>ction su 100 istruzioni <strong>di</strong><br />

branch, nal caso <strong>del</strong>l’architettura P4 a<br />

130 nm e a 90 nm.<br />

Dati forniti da Intel.<br />

[Alpha99] Compaq Computer Corporation, Alpha 2<strong>12</strong>64 Microprocessor Hardware Reference<br />

Manual, 1999.<br />

[Boggs03] Boggs D., et. al. The Microarchitecture of the Intel ® Pentium ® 4 Processor on 90nm<br />

Technology. Intel ® Technology Journal, Vol 08, Issue 01, February 18, 2003.<br />

[Gochman03] Gochman S., et. al. The Intel ® Pentium ® M Processor: Microarchitecture and<br />

Performance. Intel ® Technology Journal, Vol 07, Issue 02, May 21, 2003.<br />

[Hennessy02] Hennessy, J. L. and Patterson, D. A. 2002 Computer Architecture: a Quantitative<br />

Approach. 3 rd E<strong>di</strong>tion. Morgan Kaufmann Publishers Inc. 2002.<br />

[Kaeli91] D. R. Kaeli and P. G. Emma. Branch history table pre<strong>di</strong>ction of moving target<br />

branches due to subroutine returns. In Proc. ISCA-18, pages 34–41, May 1991.<br />

[McFarling93] McFarling, S . Combining Combining branch branch pre<strong>di</strong>ctors. pre<strong>di</strong>ctors. Technical Report TN-36, Digital<br />

Western Research Laboratory, June 1993.<br />

[Pan92] S. T. Pan, K. So, and J. T. Rahmeh. Improving the accuracy of dynamic branch<br />

pre<strong>di</strong>ction using branch correlation. In Procee<strong>di</strong>ngs of ASPLOS V, pages 76–84,<br />

Boston, MA, October 1992.<br />

[Shen02] Shen J. P. , Lipasti M. Modern Processor Design, McGraw Hill Higher Education;<br />

Beta Ed e<strong>di</strong>tion (November 1, 2002).<br />

[Yeh93-ics] Yeh, T., Marr, D. T., and Patt, Y. N. 1993. Increasing the instruction fetch rate via<br />

multiple branch pre<strong>di</strong>ction and a branch address cache. In Procee<strong>di</strong>ngs of the 7th<br />

International Conference on Supercomputing (Tokyo, Japan, July 19 - 23, 1993).<br />

[Uht95] Uht, A. K., Sindagi, V., Hall, K. Disjoint eager execution: an optimal form of<br />

speculative execution. In Procee<strong>di</strong>ngs of the 28th Annual international Symposium<br />

on Microarchitecture (Dec. 1995).<br />

Roberto Giorgi, Universita’ <strong>di</strong> Siena, C208L05, Slide 40