TRANSMISSION LINE EFFECTS version L

TRANSMISSION LINE EFFECTS version L

TRANSMISSION LINE EFFECTS version L

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

Transmission line effects<br />

(and a short note on crosstalk effects)<br />

A practical presentation<br />

Michel Forté, Ultra Electronics, Canada, January 28 th , 2004, rev L<br />

♣♣♣♣♣♣♣♣♣♣♣♣♣♣♣♣♣♣♣♣♣♣♣♣♣♣♣♣♣♣♣♣♣♣♣♣♣♣♣♣<br />

TABLE OF CONTENTS<br />

1 SCOPE................................................................................................................................................ 4<br />

2 INTRODUCTION.............................................................................................................................. 4<br />

3 DEFINITION..................................................................................................................................... 6<br />

4 ELECTRICAL CHARACTERISTICS.............................................................................................. 8<br />

4.1 SHORT REVIEW LOAD AND SOURCE "V vs I" DIAGRAMS................................................ 8<br />

4.2 MODEL DESCRIPTION .......................................................................................................... 12<br />

4.3 EXAMPLE WITH A RESISTIVE LOAD ................................................................................. 14<br />

4.4 EXAMPLE WITH A CAPACITIVE LOAD.............................................................................. 18<br />

4.5 BERGERON DIAGRAMS AS AN ANALYSIS TOOL.............................................................. 20<br />

4.6 EFFECT OF SIGNAL RISE TIME........................................................................................... 28<br />

5 PRACTICAL SITUATIONS............................................................................................................ 29<br />

5.1 ACMOS, HCMOS AND OTHER DEVICES CHARACTERISTICS........................................ 29<br />

5.2 PCB's USUAL IMPEDANCES.................................................................................................. 31<br />

5.3 DESCRIPTION OF THE TWO MAIN TYPES OF SIGNALS.................................................. 32<br />

5.4 ONE DRIVER, ONE RECEIVER, clock or data signals ........................................................... 33<br />

5.5 ONE DRIVER, MANY RECEIVERS, clock signals .................................................................. 40<br />

5.6 DATA, CONTROL AND ADDRESS BUSSES .......................................................................... 43<br />

6 RULES OF THUMB ....................................................................................................................... 52<br />

6.1 RULES OF THUMB TO MANAGE <strong>TRANSMISSION</strong> <strong>LINE</strong> <strong>EFFECTS</strong>................................. 52<br />

6.2 RULES OF THUMB TO MANAGE CROSS TALK <strong>EFFECTS</strong>................................................ 53<br />

7 REAL LIFE WAVEFORMS ........................................................................................................... 55<br />

7.1 REAL LIFE WAVEFORMS (from CMA3000 MK2 avionics project)....................................... 55<br />

7.2 REAL LIFE WAVEFORMS (from “SuperHighway” defence communications project)........... 66<br />

7.3 APPENDIX 1: PCB STRIP <strong>LINE</strong>S AND MICROSTRIP CHARACTERISTICS..................... 68<br />

7.4 APPENDIX 2: COAXIAL CABLES.......................................................................................... 70<br />

7.5 APPENDIX 3: MATHCAD PROGRAM FOR OPEN <strong>TRANSMISSION</strong> <strong>LINE</strong> <strong>EFFECTS</strong>...... 73<br />

8 BIBLIOGRAPHY............................................................................................................................. 75<br />

1

LIST OF FIGURES<br />

Figure 1: Typical waveforms distortions....................................................................................................................................................4<br />

Figure 2: Obvious termination problem.....................................................................................................................................................5<br />

Figure 3: Multiple clocking on MUX-DEMUX ATE (GRC-512)...........................................................................................................6<br />

Figure 4: Twisted pair equivalent circuit...................................................................................................................................................6<br />

Figure 5: Coaxial cable equivalent circuit................................................................................................................................................7<br />

Figure 6: Strip line equivalent circuit.........................................................................................................................................................7<br />

Figure 7: V versus I curve for a 5V (or 100 ma) source with a 50 ohms impedance.........................................................................8<br />

Figure 8: "V versus I" curves for a TTL driver .........................................................................................................................................9<br />

Figure 9: Source and load equivalent circuit............................................................................................................................................9<br />

Figure 10: "V versus I" curves for a source and a load........................................................................................................................10<br />

Figure 11: Finding VS and VL from Io,Vo, as in Bergeron’s diagram (to come).............................................................................10<br />

Figure 12: TTL driver, its load and the Thévenin equivalent of its load ............................................................................................11<br />

Figure 13: "V versus I" curves for a TTL driver and its load...............................................................................................................11<br />

Figure 14: Energy traveling down a transmission line..........................................................................................................................12<br />

Figure 15: Transmission line rule #2.......................................................................................................................................................13<br />

Figure 16: Driving a resistive load through a coaxial cable................................................................................................................14<br />

Figure 17: Driving an open circuit through a transmission line.........................................................................................................15<br />

Figure 18: Driving a short circuit through a transmission line...........................................................................................................16<br />

Figure 19: Driving a capacitor through a transmission line................................................................................................................18<br />

Figure 20: Driving a capacitor through a transmission line, waveforms ..........................................................................................19<br />

Figure 21: TTL driver and load.................................................................................................................................................................20<br />

Figure 22: Bergeron diagram for a TTL driver/receiver pair, 0 to high transition, 50 Ω line......................................................20<br />

Figure 23: TTL driver - transmission line pair at t > 0, < 2 line delays............................................................................................21<br />

Figure 24: Transmission line - TTL receiver pair at t > 1, < 3 line delays......................................................................................21<br />

Figure 25: Transmission line - TTL driver pair at t > 2, < 4 line delays...........................................................................................22<br />

Figure 26: Waveforms for a TTL driver/receiver pair, 0 to high transition, 50 Ω line...................................................................23<br />

Figure 27: Bergeron diagram for a TTL driver/receiver pair, high to low transition, 50 Ω line..................................................24<br />

Figure 28: Waveforms for a TTL driver/receiver pair, high to low transition, 50 Ω line...............................................................24<br />

Figure 29: Bergeron diagram for a TTL driver/receiver pair, both transitions, 25Ω line..............................................................25<br />

Figure 30: Waveforms for a TTL driver/receiver pair, both transitions, 25Ω line...........................................................................26<br />

Figure 31: Bergeron diagram for a 0Ω driver driving a short through a 100Ω line.......................................................................27<br />

Figure 32: The effect of rise time ...............................................................................................................................................................28<br />

Figure 33: LVDS (Low Voltage Differential Signaling)........................................................................................................................30<br />

Figure 34: Microstrip and stripline...........................................................................................................................................................31<br />

Figure 35: Strong driver, no termination.................................................................................................................................................33<br />

Figure 36: Strong driver and high impedance receiver Bergeron diagram.......................................................................................34<br />

Figure 37: Strong driver and high impedance receiver waveforms ....................................................................................................34<br />

Figure 38: Strong driver, diode termination............................................................................................................................................35<br />

Figure 39: Strong driver and diodes terminated receiver Bergeron diagram...................................................................................36<br />

Figure 40: Strong driver and diodes terminated receiver waveforms.................................................................................................36<br />

Figure 41: Series termination at the source ............................................................................................................................................37<br />

Figure 42: Waveforms for series termination at the source..................................................................................................................37<br />

Figure 43: Parallel termination at the load.............................................................................................................................................38<br />

Figure 44: Waveforms for parallel termination at the load..................................................................................................................38<br />

Figure 45: Parallel termination at the load with capacitor..................................................................................................................39<br />

Figure 46: Waveforms for parallel termination at the load with capacitor.......................................................................................39<br />

Figure 47: "Many receivers" preferred topology...................................................................................................................................40<br />

Figure 48: "Many receivers" possible waveforms..................................................................................................................................40<br />

Figure 49: Helping with a small serial resistor......................................................................................................................................41<br />

Figure 50: Preferred topology for one driver, many receivers ............................................................................................................41<br />

Figure 51: One driver, many receivers; dangerous star topology.......................................................................................................42<br />

Figure 52: One driver, many receivers; dangerous star topology waveforms ..................................................................................42<br />

Figure 53: Example of multipath net........................................................................................................................................................43<br />

Figure 54: Increasingly complex routing.................................................................................................................................................46<br />

Figure 55: Driving in parallel n 50 ohms lines (n = 1,2,6, ∞) of length 20/n cm with a source impedance of 25, 50 and 100<br />

ohms .................................................................................................................................................................................................................47<br />

Figure 56: Scope waveforms obtained when driving nets with peculiar topologies.........................................................................48<br />

Figure 57: General PCB layout to control cross talk and transmission line effects ........................................................................53<br />

Figure 58: Extender PCB layout to control cross talk and transmission line effects.......................................................................54<br />

Figure 59: Example of a one driver one receiver clock scheme (SED1386 40 MHz clock)............................................................55<br />

2

Figure 60: Waveform directly at driver output (point A) ......................................................................................................................56<br />

Figure 61: Waveform after serial discrete resistor located near driver output (point B) ...............................................................57<br />

Figure 62: Waveform at receiver (point C).............................................................................................................................................58<br />

Figure 63: Measured 20MHz SED1386 at clock input pin without driver serial resistor...............................................................59<br />

Figure 64: Measured 20MHz SED1386 at clock input pin with driver serial resistor....................................................................59<br />

Figure 65: Serial IO clock scheme ............................................................................................................................................................60<br />

Figure 66: Measured 10MHz serial IO clock at driver output without termination resistor..........................................................61<br />

Figure 67: Measured 10MHz serial IO clock at first receiver input without termination resistor................................................61<br />

Figure 68: Measured 10MHz serial IO clock at last receiver input without termination resistor.................................................62<br />

Figure 69: Measured 10MHz serial IO clock at driver output with termination resistor...............................................................62<br />

Figure 70: Measured 10MHz serial IO clock at first receiver input with termination resistor......................................................63<br />

Figure 71: Measured 10MHz serial IO clock at last receiver input with termination resistor......................................................63<br />

Figure 72: "Real life" example of a data bus routing ...........................................................................................................................64<br />

Figure 73: "Real life" example of a data bus waveform.......................................................................................................................65<br />

Figure 74: Power PC SDRAM control signal at driver. Total net length is 10.7 cm......................................................................66<br />

Figure 75: PowerPC control signal worst case stabilization time measured at the driver............................................................67<br />

Figure 76: PowerPC control signal waveform at the far end receiver..............................................................................................67<br />

3

1 SCOPE<br />

This presentation deals with the application of lossless transmission line theory, and its<br />

implications regarding the integrity of digital signals. The presentation is addressed mainly to design<br />

engineers, technicians, cad-cam staff and field personnel. Its purpose is to help people prevent and/or<br />

correct interconnection problems: 1) Between instruments<br />

2) Between PCBs<br />

3) Between ICs of a PCB<br />

Please feel free to make comments as we go along, such as sharing past experiences.<br />

2 INTRODUCTION<br />

As signals rise times diminish, transmission line effects, which were previously seen only when<br />

using long (> 1 meter) interconnections, are now present on most PCB boards where they often become<br />

a source of major headaches. These effects distort the digital signals edges:<br />

Figure 1: Typical waveforms distortions<br />

These characteristic patterns are called ringing. Their end effect on the "well being" of the circuit can be:<br />

1) Multiple clocking on clock lines (which is often fatal)<br />

2) Increased delay on level sensitive lines (which can be fatal at high temperatures where<br />

circuits are slower).<br />

3) Improper operation of parts subjected to those signals.<br />

Here is a typical interconnection problem, and a possible correction:<br />

4

-demo-<br />

Figure 2: Obvious termination problem<br />

Later in the presentation, we present applicable parts of the transmission line theory and the way<br />

to apply it to avoid these difficulties.<br />

What makes these problems especially bad to diagnose is that they are often intermittent and will<br />

maliciously appear at temperature extremes, where probing the circuit is so enjoyable… At high<br />

temperatures, circuits are slower and marginal timings may fail. Problems appear even more often at low<br />

temperature, where circuits are faster, thus providing sharper edges and at the same time being more<br />

susceptible to sharp edges. Here are 3 examples of those problems, which were diagnosed sometimes<br />

ago, at BAE Systems:<br />

EXAMPLE 1: RAM memory write problem on GRC-512 BBU XMT-RCV PLL<br />

cause: uncontrolled WRITE PULSE line layout<br />

solution: change the WRITE PULSE line layout from a star to a daisy chain.<br />

EXAMPLE 2: Flash memory read problem on GRC-512 RFU CONTROLLER<br />

Excessive ringing on address input caused, at low temperatures, a wrong data reading because<br />

the address input voltage value exceeded the chip supply value for a sufficiently long time (there was<br />

actually a spec for this).<br />

5

cause: uncontrolled WRITE PULSE line layout<br />

solution: terminate all address lines with a diode network (one diode to gnd, one to vcc).<br />

EXAMPLE 3: Multiple clocking on MUX-DEMUX ATE (GRC-512)<br />

Figure 3: Multiple clocking on MUX-DEMUX ATE (GRC-512)<br />

The Logic Analyzer is triggered spuriously because it expects a 0-5V level<br />

cause: wrong cable impedance matching<br />

solution: remove one of the 2 resistors, preferably the 50 Ω<br />

3 DEFINITION<br />

Physically, a transmission line is a set of two conductors which exhibit between themselves<br />

controlled mechanical and electrical characteristics.<br />

Zo ≅ 120 Ω<br />

examples:<br />

1- Twisted pair<br />

Figure 4: Twisted pair equivalent circuit<br />

6

2- Coaxial cable: (RG58 and the likes)- (see appendix 2)<br />

Z0 ≅ 50 - 75 Ω<br />

3- Stripline: (designed on a PCB)- (see appendix 1)<br />

Z0 ≅ 40 - 100 Ω<br />

Figure 5: Coaxial cable equivalent circuit<br />

Figure 6: Strip line equivalent circuit<br />

7

4 ELECTRICAL CHARACTERISTICS<br />

4.1 SHORT REVIEW LOAD AND SOURCE "V vs I" DIAGRAMS<br />

4.1.1 Voltage sources and current sources<br />

A time invariant voltage source and its equivalent current source are shown in the following<br />

diagram:<br />

Both of these models are equivalent and are simply different ways of looking at the "V versus I"<br />

curve which describes the source behavior; for the rest of the presentation, we will use the voltage<br />

source model since voltages are easier to measure than currents.<br />

V, volts<br />

6<br />

5<br />

4<br />

3<br />

2<br />

1<br />

0<br />

source.m: V versus I curve for a 5V (or 100 ma) source with a 50 ohms impedance<br />

slope = -50 ohms<br />

-1<br />

-20 0 20 40 60 80 100<br />

I, ma<br />

120 140 160 180 200<br />

Figure 7: V versus I curve for a 5V (or 100 ma) source with a 50 ohms impedance<br />

8

More generally, the curve V versus I is not a straight line. For example, a TTL driver curve looks<br />

like the following:<br />

V, volts<br />

5<br />

4.5<br />

4<br />

3.5<br />

3<br />

2.5<br />

2<br />

1.5<br />

1<br />

0.5<br />

0<br />

-0.5<br />

-1<br />

-1.5<br />

-2<br />

-2.5<br />

ttl.m: "V versus I" curves for a TTL driver<br />

driver "low"<br />

-3<br />

-50 -45 -40 -35 -30 -25 -20 -15 -10<br />

I, ma<br />

-5 0 5 10 15 20 25 30<br />

Figure 8: "V versus I" curves for a TTL driver<br />

4.1.2 Sources and loads<br />

A time invariant voltage source and a load are shown in the following diagram. Note that the<br />

load, which we would normally show as a resistor to ground, has been represented by another source to<br />

be more general to illustrate all kinds of loads such as pull-ups. In fact, the load cannot be distinguished<br />

from the source except for the fact that, by convention, the current enters it instead of leaving it.<br />

Figure 9: Source and load equivalent circuit<br />

Because of the current I sign convention, the source "V versus I" curve has a negative slope -RS<br />

whereas the load has a positive slope +RL. The voltage V and current I present in the circuit are simply<br />

obtained at the intersection of the source and the load curves as shown below:<br />

9<br />

driver "high"

V, volts<br />

sou-load.m: V versus I curve for a 5V, 100 ohms source with a 50 ohms to ground load<br />

6<br />

5<br />

4<br />

3<br />

2<br />

1<br />

0<br />

slope = -100 ohms<br />

33ma, 1.66 volts<br />

-1<br />

-20 0 20 40 60 80 100<br />

I, ma<br />

120 140 160 180 200<br />

10<br />

slope = +50 ohms<br />

Figure 10: "V versus I" curves for a source and a load<br />

Note also that if a point (Io,Vo) is known on a linear source curve of impedance RS, then<br />

the source voltage is Vo+IoRS. Also, if a point (Io,Vo) is known on a linear load curve of<br />

impedance RL, then the "load voltage" is Vo-IoRL, as shown in the picture below:<br />

VS<br />

VL<br />

V<br />

RS = 20<br />

Io,Vo<br />

Io,Vo<br />

RL = 70<br />

I<br />

Source vs Load curves.vsd<br />

Figure 11: Finding VS and VL from Io,Vo, as in Bergeron’s diagram (to come)<br />

Obviously, the same line of reasoning applies if the curves are not straight lines as in the case of<br />

real drivers and real receivers. Below is an example of a TTL gate driving a voltage divider connected<br />

between VCC and GND

V, volts<br />

5<br />

4.5<br />

4<br />

3.5<br />

3<br />

2.5<br />

2<br />

1.5<br />

1<br />

0.5<br />

0<br />

-0.5<br />

-1<br />

-1.5<br />

-2<br />

-2.5<br />

Figure 12: TTL driver, its load and the Thévenin equivalent of its load<br />

ttl-load.m: "V versus I" curves for a TTL driver and its load<br />

driver "low"<br />

load curve<br />

-3<br />

-50 -45 -40 -35 -30 -25 -20 -15 -10 -5 0 5 10 15 20 25 30<br />

I, ma<br />

Figure 13: "V versus I" curves for a TTL driver and its load<br />

11<br />

driver "high"<br />

(-8.5792, 0.20297)<br />

(8.2076, 2.6011)

4.2 MODEL DESCRIPTION<br />

A transmission line is essentially a delay line in which waves of voltage and current circulate.<br />

The line stores energy in the form of voltage, stored in the line capacitance, and in the form of current,<br />

stored in the line inductance. When a voltage is applied or a current injected at one end of the line, a<br />

wave of voltage and current travels down the line at nearly the speed of light (which is 30 cm/nsec).<br />

When the waves encounter a discontinuity, there is an "energy exchange" between the voltage and the<br />

current waves and there are reflected waves. The diagram below illustrates how energy travels along the<br />

line:<br />

Figure 14: Energy traveling down a transmission line<br />

Where the source is turned on, a current I1 is injected in the first inductor, which "stores"<br />

the current. This current charges the first capacitor, which discharges in the second inductor and so on,<br />

forming the propagating waves of voltage and current.<br />

By solving the differential equations that describe this electrical system, and defining<br />

we arrive at mathematical solutions for the voltage and current waveforms. In the above<br />

definition of Zo,<br />

L is the inductance per unit length (Henries/meter) and<br />

C is the capacitance per unit length (Farads/meter)<br />

The smaller the inner conductor, the larger is L and thus the larger Zo; the nearer the 2<br />

conductors, the larger is C and the smaller is Zo.<br />

The mathematical solution can be interpreted to give the following model, which obeys a few<br />

simple rules:<br />

rule 1) The waves travel at nearly the speed of light:<br />

c is the speed of light = 3x10 8 m/sec<br />

εr is the dielectric constant (4.7 for PCB material G10)<br />

v ≅ 12 cm/nsec on a G10 board<br />

Zo = characteristic..<br />

impedance =<br />

v =<br />

c<br />

ε<br />

r<br />

12<br />

L<br />

C

ule 2) Each time there is a change at the driver/line or line/load interfaces, either because<br />

different values of voltage/current (Vo, Io) reach an interface or because the driver/receiver<br />

characteristics change, the new values V and I propagating back along the transmission line are<br />

calculated using the models in the figure below.<br />

If the change occurred because the driver output or the load changed, then "Io, Vo" are<br />

the values in the line when the change occurred; “I, V” are the new values of current and voltage<br />

given by the driver or accepted by the load, that are also propagating back along the line.<br />

If the change occurred because a wave "Io, Vo" has reached the driver or the load, then<br />

again, “I, V” are the new values of current and voltage given by the driver or accepted by the load,<br />

that are also propagating back along the line.<br />

Figure 15: Transmission line rule #2<br />

• The key concept is the expression Vo ± IoZo which shows that the energy is present in the<br />

form of both a voltage and a current.<br />

N.B.: This is completely general, for any type of source or load: for example, the load driven by<br />

the transmission line may be a short, an open, another transmission line, a capacitor, another source, a<br />

filter, etc.<br />

rule 3) Each time a signal reaches the load or the source, if “I, V” are different from “Io,<br />

Vo”, reflections occur. The amplitude of the reflected wave is the difference between the new<br />

signal value that appears at the load (or source) (= “I, V”) and the incident signal value (= “Io,<br />

Vo”).<br />

13

4.3 EXAMPLE WITH A RESISTIVE LOAD<br />

To help crystallize these rules, let us look at a few practical cases illustrated with the following<br />

simple circuit:<br />

Figure 16: Driving a resistive load through a coaxial cable<br />

The following picture shows the progression of the voltage and current waves along the cable.<br />

14

4.3.1 First limit case, RL = ¥, open circuit: -demo-<br />

Figure 17: Driving an open circuit through a transmission line<br />

According to rule # 2, the source first sees the line as a 50 Ω resistor to ground, forming a divider<br />

network with the source impedance. A 2.5V, 50 ma wave starts toward the load.<br />

According to rule #2, the load sees the line as a 2.5 V + 50ma*50Ω = 5 V source. Since there is<br />

no current, since the load is an "open", the voltage at the load becomes 5 V.<br />

According to rule # 3, the reflected voltage wave is 5V at the load - 2.5V incident = 2.5V<br />

reflected. The reflected current wave is 0 ma at the load - 50ma incident = -50 ma reflected<br />

As we can observe, the source "sees" the load 100 nsec late.<br />

15

4.3.2 Second limit case, RL = 0, short circuit: -demo-<br />

Figure 18: Driving a short circuit through a transmission line<br />

According to rule # 2, the source first sees the line as a 50 Ω resistor to ground, forming a divider<br />

network with the source impedance. A 2.5V, 50 ma wave starts toward the load.<br />

According to rule # 2, the load sees the line as a 50ma + 2.5V/50Ω = 100 ma source. There is a<br />

voltage of 0 volt since the load is a short<br />

According to rule # 3, the reflected voltage wave is 0V at the load - 2.5V incident = -2.5V<br />

reflected. The reflected current wave is 100ma at the load - 50ma incident = 50 ma reflected<br />

As we can observe, the source "sees" the short 100 nsec late.<br />

16

4.3.3 General case, RL = any value: -demo-<br />

4.3.3.1 Voltage equations:<br />

According to rule # 2, the source first sees the line as a Zo Ω resistor to ground, forming a<br />

divider network with the source impedance. A wave of amplitude "2.5V, 50ma = 2.5V/50Ω" starts<br />

toward the load. The load sees the line as a "5V = 2.5 V + 50ma*50Ω" source. The voltage VL at the<br />

load is:<br />

⎛ R ⎞ L<br />

V ⎜<br />

⎟<br />

L = 5V<br />

×<br />

⎝ RL<br />

+ 50Ω<br />

⎠<br />

The reflected voltage VR is the actual voltage VL minus the incident voltage (rule 3) or<br />

V<br />

The voltage reflection coefficient CRV is the ratio of the reflected to incident wave and is given<br />

by the well known formula<br />

If RL = Zo = 50Ω, there is no reflection; if RL > Zo, there is a positive reflection; the largest<br />

positive reflection is obtained when RL = ∞, as shown in a previous wave diagram. If RL < Zo, there is a<br />

negative reflection; the largest negative reflection is obtained when RL = 0, as shown in a previous wave<br />

diagram.<br />

4.3.3.2 Current equations:<br />

R<br />

⎛<br />

= 5V<br />

× ⎜<br />

⎝ R<br />

L<br />

R ⎞<br />

⎛ ⎞<br />

L<br />

RL<br />

− 50Ω<br />

⎟ − 2.<br />

5V<br />

= 2.<br />

5V<br />

× ⎜<br />

⎟<br />

+ 50Ω<br />

⎠<br />

⎝ RL<br />

+ 50Ω<br />

⎠<br />

C<br />

RV<br />

⎛ R<br />

= ⎜<br />

⎝ R<br />

L<br />

L<br />

− 50Ω<br />

⎞ ⎛ R<br />

⎟ = ⎜<br />

+ 50Ω<br />

⎠ ⎝ R<br />

The load sees the line as a "2.5V/50Ω + 50ma = 100ma" source. The current IL at the load is:<br />

⎛ 50Ω<br />

⎞<br />

I<br />

⎜<br />

⎟<br />

L = 100ma×<br />

⎝ RL<br />

+ 50Ω<br />

⎠<br />

The reflected current IR is the actual current IL minus the incident current (rule 3) or<br />

⎛ 50Ω<br />

⎞<br />

⎛ 50Ω<br />

− R ⎞ L<br />

I<br />

⎜<br />

⎟<br />

⎜<br />

⎟<br />

R = 100ma×<br />

−50ma<br />

= 50ma×<br />

⎝ RL<br />

+ 50Ω<br />

⎠<br />

⎝ 50Ω<br />

+ RL<br />

⎠<br />

The voltage reflection coefficient CRI is the ratio of the reflected to incident wave and is given by<br />

the well known formula<br />

C<br />

RI<br />

⎛ 50Ω<br />

− R<br />

= ⎜<br />

⎝ 50Ω<br />

+ R<br />

Note that CRI = -CRV. A positive voltage reflection, due to a large load resistor is thus associated<br />

with a negative current reflection, and vice-versa.<br />

17<br />

L<br />

L<br />

L<br />

L<br />

− Zo ⎞<br />

⎟<br />

+ Zo ⎠<br />

⎞ ⎛ Zo − R<br />

⎟ = ⎜<br />

⎠ ⎝ Zo + R<br />

L<br />

L<br />

⎞<br />

⎟<br />

⎠

4.4 EXAMPLE WITH A CAPACITIVE LOAD<br />

18<br />

-demo-<br />

Figure 19: Driving a capacitor through a transmission line

Figure 20: Driving a capacitor through a transmission line, waveforms<br />

According to rule # 2, the source first sees the line as a 50 Ω resistor to ground, forming a divider<br />

network with the source impedance. A 2.5V, 50 ma wave starts toward the load.<br />

According to rule # 2, the load sees the line as a 2.5 V + 50ma*50Ω = 5 V source, and charges<br />

to 5V with a time constant of 50Ω×1nF = 50 nsec.<br />

According to rule # 3, the reflected voltage wave is the load waveform - 2.5V (incident) = 50<br />

nsec RC capacitor charge from -2.5 to +2.5V. The reflected current wave is the load waveform -50ma<br />

(incident) = current discharge from +50ma to -50ma.<br />

19

4.5 BERGERON DIAGRAMS AS AN ANALYSIS TOOL<br />

Bergeron diagrams are an analytical tool to visualize and predict line transmission effects for a<br />

single driver single receiver pair. As an example, we will consider the TTL driver and the receiver<br />

"V vs I" curves shown previously:<br />

Figure 21: TTL driver and load<br />

At time t = 0, the switch is closed, and the TTL driver, already in a high state, starts to drive the<br />

transmission line. This point in time is the START POINT in the diagram below. If the transmission line<br />

were infinitely short, the voltage and current would instantaneously jump to the END POINT. Because<br />

of the transmission line, the voltage and current change by steps as shown by the zigzag line and as<br />

explained below.<br />

V, volts<br />

5<br />

4.5<br />

4<br />

3.5<br />

3<br />

2.5<br />

2<br />

1.5<br />

1<br />

0.5<br />

0<br />

-0.5<br />

-1<br />

-1.5<br />

-2<br />

-2.5<br />

ttl-high.m: Bergeron`s diagram for TTL driver/receiver pair and a 50 ohms line<br />

receiver curve<br />

(-.62,2.29)<br />

1

By rule 2), at t = 0, when the switch is closed, the driver sees a 50 Ω resistor load to ground as<br />

shown below. The transmission line load curve is thus the straight line between the start point and point<br />

A.<br />

Figure 23: TTL driver - transmission line pair at t > 0, < 2 line delays<br />

A wave of voltage and a wave of current start traveling down the line. The voltage and current values<br />

are given by the coordinates of intersection point A: 22.6 ma, 1.13 volts.<br />

At t = 1 transmission line unit delay, the waves reach the load, to which, by rule 2), they appear as a<br />

source of 2.26 volts with 50Ω impedance as shown below: V + I×Zo = 1.13 + 22.6 ma × .050 KΩ =2.26<br />

volts.<br />

Figure 24: Transmission line - TTL receiver pair at t > 1, < 3 line delays<br />

The transmission line source curve is thus the straight line between point A and B. The voltage and<br />

current values at the load are given by the coordinates of intersection point B: -.62 ma, 2.29 volts. By<br />

rule 3), there are reflected waves of amplitude such that what remains in the line is what is seen by the<br />

load (-.62 ma, 2.29 volts).<br />

21

These waves travel back toward the source where they make the transmission line look like a load of<br />

2.321 volts with 50Ω impedance as shown below: V - I×Zo = 2.29 - -.62 ma * .050 KΩ = 2.321 volts.<br />

Figure 25: Transmission line - TTL driver pair at t > 2, < 4 line delays<br />

The transmission line source curve is thus the straight line between point B and C. The voltage and<br />

current values at the source are given by the coordinates of intersection point C: 7.62 ma, 2.70 volts.<br />

Again, parts of the wave are reflected back.<br />

By iterating, we slowly converge toward the END POINT.<br />

22

On a practical point of view, what is important is to determine the moment where the load will see a<br />

high level (2.0 volts). In this case, the first incident wave carries 2.29 volts and is thus enough so that the<br />

delay to get a "one" is the minimum value of one line delay. This can be better observed in the following<br />

time diagrams extracted from the Bergeron diagram. The waveform at the driver is also supplied. These<br />

can of course be seen on a scope.<br />

V, volts<br />

10<br />

9<br />

8<br />

7<br />

6<br />

5<br />

4<br />

3<br />

2<br />

1<br />

0<br />

-1<br />

-2<br />

-3<br />

-4<br />

ttl-high.m: driver<br />

UNDEFINED LEVEL<br />

-5<br />

0 1 2 3 4 5 6 7 8 9 10<br />

t, units of line delay<br />

Figure 26: Waveforms for a TTL driver/receiver pair, 0 to high transition, 50 W line<br />

V, volts<br />

23<br />

10<br />

9<br />

8<br />

7<br />

6<br />

5<br />

4<br />

3<br />

2<br />

1<br />

0<br />

-1<br />

-2<br />

-3<br />

-4<br />

ttl-high.m: receiver<br />

UNDEFINED LEVEL<br />

-5<br />

0 1 2 3 4 5 6 7 8 9 10<br />

t, units of line delay

4.5.1 A FEW OTHER EXAMPLES OF BERGERON DIAGRAMS<br />

4.5.1.1 HIGH TO LOW TRANSITION ON THE PREVIOUS TTL DRIVER-RECEIVER PAIR<br />

(50 Ω <strong>LINE</strong>)<br />

The Bergeron diagram and the corresponding waveforms are given below:<br />

V, volts<br />

5<br />

4.5<br />

4<br />

3.5<br />

3<br />

2.5<br />

2<br />

1.5<br />

1<br />

0.5<br />

0<br />

-0.5<br />

-1<br />

-1.5<br />

-2<br />

-2.5<br />

ttl-low.m: Bergeron`s diagram for TTL driver/receiver pair and a 50 ohms line<br />

driver "low"<br />

receiver<br />

-3<br />

-50 -45 -40 -35 -30 -25 -20 -15 -10 -5 0 5 10 15 20 25 30<br />

I, ma<br />

START POINT<br />

driver "high"<br />

END POINT<br />

Figure 27: Bergeron diagram for a TTL driver/receiver pair, high to low transition, 50 W line<br />

V, volts<br />

10<br />

9<br />

8<br />

7<br />

6<br />

5<br />

4<br />

3<br />

2<br />

1<br />

0<br />

-1<br />

-2<br />

-3<br />

-4<br />

ttl-low.m: driver<br />

UNDEFINED LEVEL<br />

-5<br />

0 1 2 3 4 5 6 7 8 9 10<br />

t, units of line delay<br />

V, volts<br />

-5<br />

0 1 2 3 4 5 6 7 8 9 10<br />

t, units of line delay<br />

Figure 28: Waveforms for a TTL driver/receiver pair, high to low transition, 50 W line<br />

Note that the delay to a guarantied 0 at the load is 3 line delays instead of 1, and that there is a<br />

slight undershoot.<br />

24<br />

10<br />

9<br />

8<br />

7<br />

6<br />

5<br />

4<br />

3<br />

2<br />

1<br />

0<br />

-1<br />

-2<br />

-3<br />

-4<br />

ttl-low.m: receiver<br />

UNDEFINED LEVEL

4.5.1.2 BOTH TRANSITIONS ON THE PREVIOUS TTL DRIVER-RECEIVER PAIR (25 Ω<br />

<strong>LINE</strong>)<br />

The Bergeron diagram and the corresponding waveforms are given below for a 25W line<br />

V, volts<br />

5<br />

4.5<br />

4<br />

3.5<br />

3<br />

2.5<br />

2<br />

1.5<br />

1<br />

0.5<br />

0<br />

-0.5<br />

-1<br />

-1.5<br />

-2<br />

-2.5<br />

ttl-25.m: Bergeron`s diagram for TTL driver/receiver pair and a 25 ohms line<br />

driver "low"<br />

receiver<br />

-3<br />

-50 -45 -40 -35 -30 -25 -20 -15 -10 -5 0 5 10 15 20 25 30<br />

25<br />

I, ma<br />

driver "high"<br />

Figure 29: Bergeron diagram for a TTL driver/receiver pair, both transitions, 25W line

V, volts<br />

V, volts<br />

10<br />

9<br />

8<br />

7<br />

6<br />

5<br />

4<br />

3<br />

2<br />

1<br />

0<br />

-1<br />

-2<br />

-3<br />

-4<br />

10<br />

9<br />

8<br />

7<br />

6<br />

5<br />

4<br />

3<br />

2<br />

1<br />

0<br />

-1<br />

-2<br />

-3<br />

-4<br />

high transition: driver<br />

UNDEFINED LEVEL<br />

-5<br />

0 1 2 3 4 5 6 7 8 9 10<br />

t, units of line delay<br />

low transition: driver<br />

UNDEFINED LEVEL<br />

-5<br />

0 1 2 3 4 5 6 7 8 9 10<br />

t, units of line delay<br />

Figure 30: Waveforms for a TTL driver/receiver pair, both transitions, 25W line<br />

V, volts<br />

V, volts<br />

26<br />

10<br />

9<br />

8<br />

7<br />

6<br />

5<br />

4<br />

3<br />

2<br />

1<br />

0<br />

-1<br />

-2<br />

-3<br />

-4<br />

-5<br />

0 1 2 3 4 5 6 7 8 9 10<br />

10<br />

9<br />

8<br />

7<br />

6<br />

5<br />

4<br />

3<br />

2<br />

1<br />

0<br />

-1<br />

-2<br />

-3<br />

-4<br />

high transition: receiver<br />

UNDEFINED LEVEL<br />

t, units of line delay<br />

low transition: receiver<br />

UNDEFINED LEVEL<br />

-5<br />

0 1 2 3 4 5 6 7 8 9 10<br />

t, units of line delay

Note that the delay to a guarantied 1 at the load is 3 line delays, and to a 0 is 5 line delays instead<br />

of 1. A 25Ω line equivalent is obtained when many receivers are regularly connected along the<br />

line (such as in memory address and data lines). Each receivers adds to the line distributed<br />

capacitance.<br />

4.5.1.3 LIMIT CASE OF A 0Ω DRIVER DRIVING A SHORT THROUGH A 100Ω <strong>LINE</strong><br />

The Bergeron diagram and the corresponding waveforms are given below:<br />

V, volts<br />

short.m: Bergeron`s diagram for a 0 ohm driver driving a short through a 100 ohms line<br />

10<br />

9<br />

8<br />

7<br />

6<br />

5<br />

4<br />

3<br />

2<br />

1<br />

0<br />

-1<br />

-2<br />

-3<br />

-4<br />

driver "high"<br />

receiver = short<br />

START POINT<br />

-5<br />

-500 -400 -300 -200 -100 0<br />

I, ma<br />

100 200 300 400 500<br />

Figure 31: Bergeron diagram for a 0W driver driving a short through a 100W line<br />

We see that the first current wave is 5V/100Ω = 50ma. There is a reflected wave of 50 ma for a<br />

total of 100 ma which comes back towards the source where another 50 ma adds up, and so on. The<br />

short builds itself up by 50 ma on every time interval, which corresponds one line delay.<br />

27

4.6 EFFECT OF SIGNAL RISE TIME<br />

-demo-<br />

So far we have only considered sources with 0 nsec rise time. This is not the case in real life<br />

where rise times range from below 1 nsec for ECL devices to 1-2 nsec for the fastest CMOS devices to<br />

10-20 nsec for the slowest CMOS devices. As can be seen below, on a worst case situation of low<br />

impedance driver and high impedance receiver, when the rise time reaches 4 times the line delay, the<br />

waveform is almost monotonous. It is probably reasonable to use a factor 4, i.e. the line delay should be<br />

smaller than 1/4 the rise time tr to keep ringing small enough. At 12 cm/nsec, the line length in cm should<br />

be shorter than 12 × 1/4 tr or 3 × tr. The number to remember is 3 cm maximum per nsec of rise time.<br />

Figure 32: The effect of rise time<br />

28

5 PRACTICAL SITUATIONS<br />

To see transmission line effects with the rising times we are dealing with nowadays, be prepared<br />

to use a >300 MHz scope, with possibly an active high impedance probe. The measurement is ruined by<br />

using a ground wire and disturbed by using the probe hook. Remove the hook to keep only the tip and<br />

use the small spring as a ground connection to be connected to the ground plane less than 1 cm from the<br />

signal being probed. A trick I use often, is short (1 cm) pieces of wire which I wirewrap around the tip<br />

and the spring and which I solder to the points of interest to keep my hands free. Of course, it is nice to<br />

be able to see these effects, but it is much better to avoid them in the first place, as we show below.<br />

5.1 ACMOS, HCMOS AND OTHER DEVICES CHARACTERISTICS<br />

Old HCMOS devices (1980…) have delays of the order of 25 nsec and rise times of the order of 16<br />

nsec, so that transmission line effects start to appear for line delays of 16 nsec x 3 cm/nsec, or 48 cm on<br />

a G10 board. The drivers have a symmetrical up and down drive capability and an output resistance of ~<br />

120 ohms. Inputs and outputs are clamped with diodes (~1.4V clamping voltage observed). Inputs have<br />

high impedance (< 10 uA leakage).<br />

ACMOS devices have delays of the order of 8 nsec and rise times of the order of 2 nsec, so that<br />

transmission line effects start to appear for line delays of 2 nsec x 3 cm/nsec, or 6 cm on a G10 board.<br />

The drivers have a symmetrical up and down drive capability and an output resistance of 23 ohms<br />

maximum guaranteed to be able to drive a 50 ohms line; the wave that leaves the driver has an<br />

amplitude of 50/(22+50) = 70% of VCC which is the minimum input to guarantee a high level. If<br />

necessary, many drivers from the same chip can be paralleled. Inputs and outputs are clamped with<br />

Schotky diodes (~ .8V clamping voltage observed). Inputs have high impedance (< 10 uA leakage).<br />

Popular ICs and FPGAs nowadays use 3.3 volts I/Os with TTL levels (2.0V high) input<br />

characteristics. Most inputs are high impedance inputs, with ESD protection diodes which may help<br />

quench reflections. Drivers are often not very well characterized; most of the time also, the typical drive<br />

is much higher than the guaranteed minimum. In fact, the rise times nowadays are typically 2 nsec or<br />

faster, and the drive on large ICs or CPUs is typically ~20 to 50 ohms, depending on signals. As we will<br />

see soon, these source resistances are well suited for most situations.<br />

There are now a large number of new families on the market, each with its advantages in terms of speed,<br />

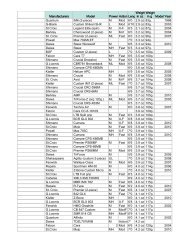

noise, drive, etc. A few of them are listed in the table below:<br />

Family<br />

name<br />

Company Power supply Drive Speed<br />

HC Many 5V 4 ma 24 nsec<br />

AC Many 5 / 3.3V 24 / 12 ma 3.5 / 5 nsec<br />

AHC Texas Instruments 5/ 3.3 V 8 / 4 ma 5.5 / 8.3 nsec<br />

VHC Fairchild 5 / 3.3 V 8 / ? ma 10.5 / ? nsec<br />

VCX Fairchild 3.3 / 2.5 V 24 ma 2.5 / 3.2 nsec<br />

LCX Fairchild 3.3 V 24 ma 6.5 nsec<br />

LVX Fairchild 3.3 V 4 ma 12 nsec<br />

LVQ Fairchild 3.3 V 12 ma 9.5 nsec<br />

LVT Fairchild 3.3 V 32 ma 4.1 nsec<br />

ALVC Philips 3.3 / 2.5 / 1.2 V 24 ma 2.0 nsec at 3 V<br />

29

LVDS (Low Voltage Differential Signaling) sets a new standard altogether. It is a way to communicate<br />

data at very high rates (gigabit/sec) using very low power by means of a differential low voltage (~ 350<br />

mV) swing. It has been standardized as ANSI/EIA/TIA-644 and is supported by many semiconductor<br />

vendors. The figure below illustrates LVDS:<br />

Figure 33: LVDS (Low Voltage Differential Signaling)<br />

It is most interesting to draw the Bergeron diagram for such a differential driver.<br />

30

5.2 PCB's USUAL IMPEDANCES<br />

From the microstrip and strip line charts in appendix 2, we have the following typical<br />

impedances and capacitances, starting from the fact that the PCB's are often 100 mil thick with 8, 10 or<br />

12 layers (=> ~10 mil between layers). 1 mil = 1/1000 inch = .0254 mm.<br />

Z0<br />

(ohms)<br />

√εr × Z0<br />

Microstrip<br />

W/h<br />

Figure 34: Microstrip and stripline<br />

Stripline<br />

W/b = W/2h<br />

Stripline<br />

W/h<br />

31<br />

Microstrip<br />

W (mil) for<br />

h = 10 mil<br />

Stripline<br />

W (mil) for<br />

h = 10 mil<br />

Microstrip<br />

capacity<br />

(pF/m) for<br />

h = 10 mil<br />

Stripline<br />

capacity<br />

(pF/m) for<br />

h = 10 mil<br />

25 54 5 1.5 3 50 30 229 324<br />

50 108 1.5 .4 .8 15 8 112 153<br />

60 130 1.0 .25 .5 10 5 91 133<br />

75 163 .5 .13 .26 5 2.6 64 108<br />

100 217 .2 - - 2 - 47 83<br />

Table 1: Usual PCB trace impedances and capacitances<br />

We see that to obtain large impedances (> 50Ω), the dielectric thickness must be increased. High<br />

impedances are easier to obtain on a microstrip, on the PCB top or bottom layer, but the signals are not<br />

as well shielded. With a minimum trace width of 5 mil, we see that one can obtain Zo up to 75 Ω on the<br />

top layer (microstrip) and 60 Ω on the internal layers (stripline).<br />

One must keep in mind that ICs input are capacitive, and when many are connected across a line (such<br />

as an address bus line), the effective line impedance decreases. For example, consider a 60 Ω strip line<br />

with ten 5 pF IC inputs uniformly distributed along its 20 cm length. The line intrinsic capacitance is<br />

26.6 pF (from 133 pF/m (see above table) multiplied by .2m). From 26.6, it increases to 76.6 (=26.6 +<br />

10*5). Since Zo = √L/C, Zo decreases by 1.71 (=√76.6/26.6) to 35 Ω.

5.3 DESCRIPTION OF THE TWO MAIN TYPES OF SIGNALS<br />

The two main types of signals are 1) “data”, 2) “clock” or “edge sensitive” signals. Each type of signal<br />

has different requirements: whereas clock signals must show a monotonous transition from the low to<br />

high and high to low states, the only thing we are concerned about data signals is the final time to<br />

stabilize to a valid<br />

lo<br />

Voltage<br />

Voltage<br />

Not acceptable<br />

“CLOCK” SIGNALS<br />

Minimum logic<br />

“1” value<br />

Maximum logic<br />

“0” value<br />

“DATA” SIGNALS<br />

Total turn-on time Total turn-on time<br />

Minimum logic<br />

“1” value<br />

Maximum logic<br />

“0” value<br />

32<br />

Acceptable<br />

clock vs data signals requirements.vsd<br />

Time<br />

Acceptable<br />

(weak driver) Acceptable if overshoot not too high<br />

w or high state. This is illustrated below:<br />

(strong driver)<br />

Time

5.4 ONE DRIVER, ONE RECEIVER, clock or data signals<br />

5.4.1 Worst case of a strong driver and high impedance receiver with no termination<br />

demo<br />

Figure 35: Strong driver, no termination<br />

As we see below, this topology does not provide a monotonous transition and is thus<br />

unacceptable for clock signals. For data signal, it could be acceptable if the excessive overshoot<br />

does not cause the receiver IC to misbehave.<br />

33

V, volts<br />

V, volts<br />

strong.m: Bergeron`s diagram for a strong driver, high impedance receiver, 50 ohms line<br />

10<br />

9<br />

8<br />

7<br />

6<br />

5<br />

4<br />

3<br />

2<br />

1<br />

0<br />

-1<br />

-2<br />

driver "high" curve<br />

receiver curve<br />

= vertical line<br />

-3<br />

-140 -120 -100 -80 -60 -40 -20 0<br />

I, ma<br />

20 40 60 80 100 120 140<br />

34<br />

START POINT, t < 0<br />

Figure 36: Strong driver and high impedance receiver Bergeron diagram<br />

10<br />

9<br />

8<br />

7<br />

6<br />

5<br />

4<br />

3<br />

2<br />

1<br />

0<br />

-1<br />

-2<br />

-3<br />

-4<br />

strong-high: driver<br />

UNDEFINED LEVEL<br />

-5<br />

0 1 2 3 4 5 6 7 8 9 10<br />

t, units of line delay<br />

V, volts<br />

10<br />

9<br />

8<br />

7<br />

6<br />

5<br />

4<br />

3<br />

2<br />

1<br />

0<br />

-1<br />

-2<br />

-3<br />

-4<br />

strong-high: receiver<br />

UNDEFINED LEVEL<br />

-5<br />

0 1 2 3 4 5 6 7 8 9 10<br />

t, units of line delay<br />

Figure 37: Strong driver and high impedance receiver waveforms

5.4.2 Diodes termination (like ACMOS) demo<br />

Figure 38: Strong driver, diode termination<br />

A termination with diodes has many qualities, even if it is not as good as a resistor termination.<br />

1) If they are part of the receiver, there is no extra hardware (such as ACMOS)<br />

2) Most of the energy put in the transmission line goes back to the supply through the diodes instead of<br />

being wasted.<br />

3) For multiple receivers, as we will see later, all one has to care is to drive the line hard and connect the<br />

receivers along a single main line.<br />

At 3.3V or lower though, it is not as useful as at 5V, because of the non-negligible turn-on offset<br />

voltage (~ .5V).<br />

35

V, volts<br />

V, volts<br />

strong-d.m: Bergeron`s diagram for a strong driver, diodes terminated receiver, 50 ohms line<br />

10<br />

10<br />

-1<br />

-2<br />

-3<br />

-4<br />

9<br />

8<br />

7<br />

6<br />

5<br />

4<br />

3<br />

2<br />

1<br />

0<br />

-1<br />

-2<br />

driver "high" curve<br />

receiver curve<br />

= vertical line<br />

START POINT, t < 0<br />

-3<br />

-140 -120 -100 -80 -60 -40 -20 0<br />

I, ma<br />

20 40 60 80 100 120 140<br />

Figure 39: Strong driver and diodes terminated receiver Bergeron diagram<br />

9<br />

8<br />

7<br />

6<br />

5<br />

4<br />

3<br />

2<br />

1<br />

0<br />

strong-diodes high: driver<br />

UNDEFINED LEVEL<br />

-5<br />

0 1 2 3 4 5 6 7 8 9 10<br />

t, units of line delay<br />

V, volts<br />

-5<br />

0 1 2 3 4 5 6 7 8 9 10<br />

Figure 40: Strong driver and diodes terminated receiver waveforms<br />

36<br />

10<br />

9<br />

8<br />

7<br />

6<br />

5<br />

4<br />

3<br />

2<br />

1<br />

0<br />

-1<br />

-2<br />

-3<br />

-4<br />

strong-diodes high: receiver<br />

UNDEFINED LEVEL<br />

t, units of line delay

5.4.3 Series resistor at the source demo<br />

(Only useful if R source < line impedance)<br />

Figure 41: Series termination at the source<br />

The series resistor is chosen so that the total source impedance is equal to the line impedance. The<br />

voltage wave that travels down the line is 2.5V high. The high impedance receiver sees 5V because of<br />

the positive reflection. The reflection is entirely absorbed when it comes back to the driver. N.B.:<br />

another receiver which would be connected in the middle of the line would temporarily see a 2.5V<br />

level and may glitch. The waveforms are shown below.<br />

Figure 42: Waveforms for series termination at the source<br />

37

5.4.4 Parallel resistor at the load demo<br />

(Only useful if R source is small enough so that 5V × Zo/(R+Zo) > 3.5V (guaranteed<br />

high level)<br />

Figure 43: Parallel termination at the load<br />

The parallel resistor is chosen equal to the line impedance. The voltage wave that travels down<br />

the line is > 3.5V high. The high impedance receiver sees 3.5V because there is no reflection..<br />

N.B.: another receiver which would be connected in the middle of the line would see a ><br />

3.5V level and would work correctly. On the average, the power dissipation is<br />

5 2 /50Ω × ½ = ¼ watt! The waveforms are shown below.<br />

See section 7.1.1 for a "real life" example<br />

Figure 44: Waveforms for parallel termination at the load<br />

38

5.4.5 Combination resistor+capacitor at the load demo<br />

Same as a resistor only, except that the power dissipation is halved:<br />

Figure 45: Parallel termination at the load with capacitor<br />

The parallel resistor is chosen equal to the line impedance. The voltage wave that travels down<br />

the line is > 3.5V high. The high impedance receiver sees 3.5V because there is no reflection..<br />

N.B.: another receiver which would be connected in the middle of the line would see a ><br />

3.5V level and would work correctly. The RC value should be larger than ~ 2 × longest period<br />

without transition. On the average, the power dissipation is (2.5) 2 /50Ω = 1/8 watt! The<br />

waveforms are shown below.<br />

Figure 46: Waveforms for parallel termination at the load with capacitor<br />

39

5.5 ONE DRIVER, MANY RECEIVERS, clock signals<br />

5.5.1 Good topology:<br />

Ideally, one should have a driver that has a low enough source resistance to drive a logic "1"<br />

level (or "0") on the first wave, and one should have all receivers (high impedance) connected with short<br />

stubs (

There are two problems with this situation, and surprisingly, the problems are more acute for the<br />

receivers nearest to the driver; for the first receiver, for example,<br />

1) The delay to a logical guaranteed level "1" due to the line is ~5 nsec rather than 0. (If the<br />

driver is weaker even more reflections may be needed.<br />

2) Before the first reflection comes back, the line is left at 3 V, in an intermediate state for which,<br />

due to noise, multiple transitions at the receiver output may occur, things like:<br />

For clock lines, which are edge sensitive signals, such a behavior will cause failures.<br />

Here are some possible solutions:<br />

1) Use 2 or more drivers from the same chip connected in parallel.<br />

2) Try to physically connect the receivers together (even if far from the driver)<br />

3) Put a small resistor (20Ω) in the middle of the transmission line, forcing a small positive<br />

reflection to come back right away, providing a cleaner edge.<br />

Figure 49: Helping with a small serial resistor<br />

5.5.2 Preferred topology: (especially for clock lines which need to reach all receivers at<br />

about the same time, i.e., without skew)<br />

Figure 50: Preferred topology for one driver, many receivers<br />

41

5.5.3 Dangerous topology demo<br />

Consider the following "star" connection:<br />

Figure 51: One driver, many receivers; dangerous star topology<br />

At node A, there is a discontinuity in the line impedance: a wave coming from any branch will<br />

see 50Ω||50Ω = 25Ω. There will be a negative reflection (25-50)/(25+50) = -1/3 = -33% in the<br />

branch and a transmission of 1 - 1/3 = 2/3 = 66% in the 2 other branches. If we go through the<br />

pain of adding up all the reflections, we get:<br />

Figure 52: One driver, many receivers; dangerous star topology waveforms<br />

Obviously, receiver 1 will not operate reliably because of the negative reflection back<br />

from node A.<br />

42

5.6 DATA, CONTROL AND ADDRESS BUSSES<br />

In real life, such as with data and address busses, there are many drivers and receivers connected to the<br />

same net, only one driver being active at a time. Clearly, the simple model "one to one" developed above<br />

does not apply, if the devices are not connected in a daisy chain. It is almost impossible in that case to<br />

have guaranteed nice monotonous transitions; anyway, on address and data busses, these are not<br />

required. What we need to know though, is the stabilization delay on the net such as the one in Figure 53<br />

below, because this delay must be subtracted from our timing margins.<br />

CPU<br />

DRIVER<br />

RECEIVER 1<br />

RECEIVER 0<br />

RAM<br />

RECEIVER 4<br />

DISPLAY<br />

CONTROLLER<br />

43<br />

RECEIVER 2<br />

FLASH<br />

RECEIVER 3<br />

EEPROM<br />

2004/jan/25 multipl.vsd<br />

Figure 53: Example of multipath net<br />

Three practical questions arise:<br />

1) What is the ideal source impedance<br />

2) What is the routing strategy that will give us the smallest stabilization time ?, a star ?, a daisy chain ?<br />

3) What will then be the worst case stabilization time (for any of the devices) ?<br />

This seemingly intractable problem can be solved for all practical purposes using the daisy chain and a<br />

little mathematics.<br />

Let us start by the daisy chain routing shown in the picture above in GREEN. We have already analyzed<br />

this simple system. and we know that the receiver closest to the driver is probably the one which will<br />

incur the largest delay. Let us assume, as a typical case, that we have a 20 cm long transmission line<br />

with an effective impedance is 50 ohms, after adding the effect of the distributed receivers capacitance<br />

(see section 5.2). The following waveforms illustrate what the closest (blue line) and the farthest (red<br />

line) receivers (# 0 & # 4) will see. We use the MATHCAD program given in Appendix 3 (section 7.5<br />

and we consider 5 source impedances R: R = 5 such that R/Zo = 1/10, R = 25 such that R/Zo = ½, R =<br />

50 such that R/Zo = 1, R = 100 such that R/Z0 = 2, R = 500 such that R/Zo = 10. Typical value for the<br />

driver are in fact from 15 to 50 ohms. We also assume there is no clamping at any receiver.

voltage<br />

voltage<br />

voltage<br />

Vd( 5, t)<br />

Vl( 5, t)<br />

1.5<br />

3.5<br />

Vd( 25, t)<br />

Vl( 25, t)<br />

1.5<br />

3.5<br />

Vd( 50, t)<br />

Vl( 50, t)<br />

1.5<br />

3.5<br />

10<br />

8<br />

6<br />

4<br />

2<br />

0 5 . 10 9<br />

0<br />

10<br />

8<br />

6<br />

4<br />

2<br />

0 5.10 9<br />

0<br />

10<br />

8<br />

6<br />

4<br />

2<br />

0 5.10 9<br />

0<br />

Line impedance = 50 ohms, Rsource = 5 ohms<br />

Transmission line model<br />

44<br />

1 . 10 8<br />

t<br />

time (sec)<br />

1.5 . 10 8<br />

Line impedance = 50 ohms, Rsource = 25 ohms<br />

Transmission line model<br />

1.10 8<br />

t<br />

time (sec)<br />

1.5 .10 8<br />

Line impedance = 50 ohms, Rsource = 50 ohms<br />

Transmission line model<br />

1.10 8<br />

t<br />

time (sec)<br />

1.5 .10 8

voltage<br />

voltage<br />

Vd( 100, t)<br />

Vl( 100, t)<br />

1.5<br />

3.5<br />

Vd( 500, t)<br />

Vl( 500, t)<br />

1.5<br />

3.5<br />

10<br />

8<br />

6<br />

4<br />

2<br />

0 5 .10 9<br />

0<br />

10<br />

8<br />

6<br />

4<br />

2<br />

0 5 .10 9<br />

0<br />

Line impedance = 50 ohms, Rsource = 100 ohms<br />

Transmission line model<br />

45<br />

1 .10 8<br />

t<br />

time (sec)<br />

1.5.10 8<br />

Line impedance = 50 ohms, Rsource = 500 ohms<br />

Transmission line model<br />

1 .10 8<br />

t<br />

time (sec)<br />

1.5.10 8<br />

To have the fastest stabilization time, one would use a very strong driver and terminate the line into 50<br />

ohms. Then the near receiver would stabilize in 0 nsec and the far receiver in one line delay. This is<br />

impractical though, because the termination would dissipate too much power, and drivers that strong<br />

would probably use too much real estate on the IC die. The next best stabilization time is twice as long<br />

and is obtained when the source impedance is about equal to the line impedance; the near receiver now<br />

stabilizes in 2 line delays and the far receiver in 1 line delay, like before. CPUs and FPGAs usually have<br />

source impedances between 25 and 50 ohms for that purpose.

Consider now another imaginary situation where a driver must be connected to n receivers using lines of<br />

total delay Td, while being free to move the receivers around. One could use a daisy chain as before, and<br />

obtain 2Td as a stabilization time. Or one could use 2 lines of length Td/2, or 3 lines of length Td/3, or<br />

even n lines of length Td/n. This is illustrated below:<br />

DRIVER 1<br />

DRIVER<br />

RECEIVER 1<br />

2001/oct/16.ds4<br />

RECEIVER 0<br />

RECEIVER 0<br />

DRIVER<br />

CASE 1: one to one net<br />

line delay = Td<br />

CASE 2: one to two nets<br />

line delay = Td/2<br />

line delay = Td/2<br />

DRIVER<br />

line delay = Td<br />

CASE 3: one to n nets<br />

RECEIVER 0<br />

line delay = Td/n<br />

line delay = Td/n<br />

line delay = Td/n<br />

46<br />

RECEIVER 1<br />

RECEIVER 2<br />

RECEIVER 1<br />

RECEIVER 2<br />

RECEIVER n<br />

CASE 4: one to n nets with random routing<br />

RECEIVER 0<br />

RECEIVER 3<br />

RECEIVER 2<br />

Figure 54: Increasingly complex routing<br />

RECEIVER 1<br />

total line delay = Td<br />

total line delay = Td<br />

total line delay = Td<br />

multipl1.ds4

Intuitively, we see that the driver sees a lower impedance as n increases; on the other hand, the<br />

reflections come back faster and compensate this effect. Again, we simulate this using again the<br />

MathCad program. The "voltage versus time" graphs show what happens when the net of length "Td" is<br />

split in n stubs (1, 2, 6 and 100) of length "Td/n".. The limit for n going to infinity is a simple formula.<br />

R = 25<br />

R = 50<br />

R = 100<br />

voltage (volts)<br />

voltage (volts)<br />

voltage (volts)<br />

Vd( 1 , 25,<br />

t )<br />

Vd( 2 , 25,<br />

t )<br />

Vd( 6 , 25,<br />

t )<br />

Vi( 25, t )<br />

3.5<br />

Vd( 1 , 50,<br />

t )<br />

Vd( 2 , 50,<br />

t )<br />

Vd( 6 , 50,<br />

t )<br />

Vi( 50, t )<br />

3.5<br />

Vd( 1 , 100,<br />

t )<br />

Vd( 2 , 100,<br />

t )<br />

Vd( 6 , 100,<br />

t )<br />

Vi( 100 , t )<br />

3.5<br />

6<br />

4<br />

2<br />

0<br />

6<br />

4<br />

2<br />

0<br />

6<br />

4<br />

2<br />

0<br />

0 5 10 9<br />

0 5 10 9<br />

0 5 10 9<br />

Transmission line model<br />

1 10<br />

t<br />

8<br />

time (sec)<br />

Transmission line model<br />

1 10<br />

t<br />

8<br />

time (sec)<br />

Transmission line model<br />

1 10<br />

t<br />

8<br />

time (sec)<br />

Figure 55: Driving in parallel n 50 ohms lines (n = 1,2,6, ¥) of length 20/n cm with a source<br />

impedance of 25, 50 and 100 ohms<br />

47<br />

1.5 10 8<br />

1.5 10 8<br />

1.5 10 8<br />

2 10 8<br />

2 10 8<br />

2 10 8

Looking at the simulation waveforms, we see that the case corresponding to the “one to one” net (red<br />

lines) is the one that gives the longest delays (case 1, Error! Reference source not found.). It also<br />

seems reasonable to extrapolate that even if the stubs are not the same length, or connected differently as<br />

in case 4, Error! Reference source not found., the situation at any point along the net will be better<br />

than for the “one to one” net.<br />

Even if the above reasoning does not constitute a mathematical proof, it seems highly reasonable to<br />

answer the three practical questions raised at the beginning of this section the following way:<br />

1) The ideal source impedance is the effective transmission line impedance (taking into account the<br />

distributed receiver capacitances)<br />

2) The optimum routing is the one that yields the minimum total length, irrespective of the net<br />

configuration (star, daisy chain, etc)<br />

3) The worst case stabilization time is twice the path delay evaluated with the total net length<br />

The results could not be simpler or easier to implement: most modern drivers have source impedance of<br />

the order of the expected net impedances (25-50 ohms); the routing software should only care about<br />

minimizing the total net length, and twice the total net length is easy enough to implement. A typical 20<br />

20cm<br />

cm net thus incurs a stabilization time of 3.3 nsec = * 2<br />

12cm/<br />

ns<br />

We confirmed these results with experimentation, using six 50 ohms coaxial cables totaling 43 meters<br />

(Td = 231 nsec), and trying all 4 cases in Error! Reference source not found. for R = 25, 50, and 100<br />

ohms. The many waveforms shown on the scope correspond to different measuring points along the<br />

cables.<br />

Figure 56: Scope waveforms obtained when driving nets with peculiar topologies<br />

See next 3 pages<br />

(<br />

48

DRIVER<br />

RECEIVER 0<br />

DRIVER<br />

CASE 1: one to one net<br />

CASE 2: one to two nets<br />

RECEIVER 0<br />

DRIVER<br />

RECEIVER 0<br />

DRIVER<br />

SOURCE RESISTANCE R = 25 ohms, half the line impedance<br />

line delay = Td = 231 nsec<br />

line delay = Td/2<br />

line delay = Td/2<br />

2001/oct/18<br />

RECEIVER 1<br />

RECEIVER 1<br />

RECEIVER 2<br />

CASE 3: one to 6 nets<br />

line delay ~= Td/6<br />

line delay ~= Td/6<br />

line delay ~= Td/6<br />

CASE 4: one to 4 nets<br />

~ random<br />

line delay ~= Td/6<br />

RECEIVER 0<br />

line delay ~= Td/3<br />

Td/6<br />

line delay ~= Td/6<br />

Td/6<br />

Td/6<br />

RECEIVER 4<br />

RECEIVER 1<br />

RECEIVER 2<br />

RECEIVER 6<br />

RECEIVER 1<br />

RECEIVER 2<br />

RECEIVER 3<br />

49<br />

limit for n => ¥<br />

limit for n => ¥<br />

limit for n => ¥<br />

limit for n => ¥<br />

multi25.ds4

SOURCE RESISTANCE R = 50 ohms, same as the line impedance<br />

DRIVER<br />

RECEIVER 0<br />

DRIVER<br />

CASE 1: one to one net<br />

CASE 2: one to two nets<br />

RECEIVER 0<br />

DRIVER<br />

RECEIVER 0<br />

DRIVER<br />

line delay = Td = 231 nsec<br />

line delay = Td/2<br />

line delay = Td/2<br />

2001/oct/18<br />

RECEIVER 1<br />

RECEIVER 1<br />

RECEIVER 2<br />

CASE 3: one to 6 nets<br />

line delay ~= Td/6<br />

line delay ~= Td/6<br />

line delay ~= Td/6<br />

CASE 4: one to 4 nets<br />

~ random<br />

line delay ~= Td/6<br />

RECEIVER 0<br />

line delay ~= Td/3<br />

Td/6<br />

line delay ~= Td/6<br />

Td/6<br />

Td/6<br />

RECEIVER 4<br />

RECEIVER 1<br />

RECEIVER 2<br />

RECEIVER 6<br />

RECEIVER 1<br />

RECEIVER 2<br />

RECEIVER 3<br />

50<br />

limit for n => ¥<br />

limit for n => ¥<br />

limit for n => ¥<br />

limit for n => ¥<br />

limit for n => ¥<br />

multi50.ds4

SOURCE RESISTANCE R = 100 ohms, twice the line impedance<br />

DRIVER<br />

RECEIVER 0<br />

DRIVER<br />

CASE 1: one to one net<br />

CASE 2: one to two nets<br />

RECEIVER 0<br />

DRIVER<br />

RECEIVER 0<br />

DRIVER<br />

line delay = Td = 231 nsec<br />

line delay = Td/2<br />

line delay = Td/2<br />

2001/oct/18<br />

RECEIVER 1<br />

RECEIVER 1<br />

RECEIVER 2<br />

CASE 3: one to 6 nets<br />

line delay ~= Td/6<br />

line delay ~= Td/6<br />

line delay ~= Td/6<br />

CASE 4: one to 4 nets<br />

~ random<br />

line delay ~= Td/6<br />

RECEIVER 0<br />

line delay ~= Td/3<br />

Td/6<br />

line delay ~= Td/6<br />

Td/6<br />

Td/6<br />

RECEIVER 4<br />

RECEIVER 1<br />

RECEIVER 2<br />

RECEIVER 6<br />

RECEIVER 1<br />

RECEIVER 2<br />

RECEIVER 3<br />

51<br />

limit for n => ¥<br />

limit for n => ¥<br />

limit for n => ¥<br />

limit for n => ¥<br />

limit for n => ¥<br />

limit for n => ¥<br />

limit for n => ¥<br />

limit for n => ¥<br />

multi100.ds4

6 RULES OF THUMB<br />

6.1 RULES OF THUMB TO MANAGE <strong>TRANSMISSION</strong> <strong>LINE</strong> <strong>EFFECTS</strong><br />

These rules to be followed in descending order of priority:<br />

6.1.1 Use low voltage devices if possible (3.3V, 2.5V, 1.8V).<br />

6.1.2 Do not use faster devices than required; faster devices have shorter rise times<br />

and more crosstalk. (ACMOS rise times are 8 times shorter than HCMOS, 2 versus<br />

16 nsec). Use devices from families where OEC (Output Edge Control) has been<br />

implemented.<br />