UltraSim - Celestry Design Technologies, Inc.

UltraSim - Celestry Design Technologies, Inc.

UltraSim - Celestry Design Technologies, Inc.

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

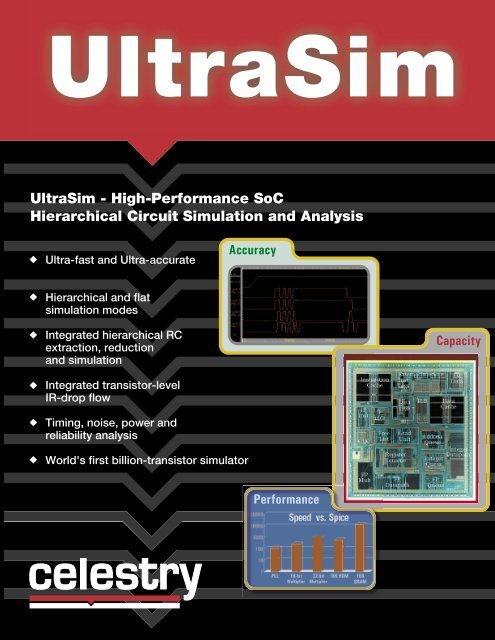

<strong>UltraSim</strong><br />

<strong>UltraSim</strong> - High-Performance SoC<br />

Hierarchical Circuit Simulation and Analysis<br />

Ultra-fast and Ultra-accurate<br />

Hierarchical and flat<br />

simulation modes<br />

Integrated hierarchical RC<br />

extraction, reduction<br />

and simulation<br />

Integrated transistor-level<br />

IR-drop flow<br />

Timing, noise, power and<br />

reliability analysis<br />

World's first billion-transistor simulator<br />

Accuracy<br />

Performance<br />

Capacity

<strong>UltraSim</strong><br />

<strong>UltraSim</strong> Overview<br />

<strong>UltraSim</strong> is a high-performance, full-chip, hierarchical circuit simulator that combines SPICEprecise<br />

accuracy and virtually unlimited capacity for memory, digital, and mixed-signal IC<br />

designs. <strong>UltraSim</strong> addresses critical deep submicron (DSM) analysis issues such as timing,<br />

noise, power, IR drop, and reliability, including hot-carrier effects. It is the first commercially<br />

available solution to successfully simulate a billion-transistor memory circuit.<br />

How <strong>UltraSim</strong> Does It<br />

<strong>UltraSim</strong> features <strong>Celestry</strong>'s universal ODE solver engine<br />

and proprietary adaptive-hierarchy compaction technology<br />

to handle your largest memory or system-on-chip (SoC)<br />

designs. Using the same simulation engine as in hierarchical<br />

mode, <strong>UltraSim</strong> is as adept at running flat simulations as<br />

the best circuit simulators on the market today.<br />

<strong>Celestry</strong>'s industry leading knowledge of device modeling<br />

and device physics is the foundation for the unique<br />

technological advantage <strong>UltraSim</strong> holds. With an available<br />

best-in-class RC reduction engine from <strong>Celestry</strong>'s widely<br />

adopted Nautilus-RCR product, <strong>UltraSim</strong> can further<br />

boost the capacity and performance of the post-layout<br />

simulation by several orders of magnitude. The tight<br />

integration to the hierarchical RC extraction makes<br />

<strong>UltraSim</strong> the only complete full-chip transistor-level<br />

post-layout verification solution.<br />

<strong>UltraSim</strong> Benefits:<br />

◆ Speeds up full-chip simulation 10x to 1,000x<br />

User-selectable accuracy to within 1% of SPICE<br />

◆ Virtually unlimited simulation capacity<br />

Handles large memory circuits like one gigabyte DRAMs<br />

◆ Handles all types of designs<br />

DRAM, SRAM, Flash, logic and mixed-signal SoCs<br />

◆ The only integrated solution for complete hierarchical and flat circuit analysis<br />

Most accurate RC extraction and RC reduction available<br />

for both hierarchical and flat designs<br />

◆ The only complete transistor-level silicon accurate sign-off solution<br />

<strong>Inc</strong>ludes timing, power, noise, IR drop and reliability analysis

<strong>UltraSim</strong> Features:<br />

◆ Only Fast-SPICE simulator with reliability analysis:<br />

HCI, EM, and NBTI (hot-carrier degradation,<br />

electromigration, negative bias temperature<br />

instability and aged simulation)<br />

◆ Unmatched hierarchical-mode<br />

simulation with adaptive<br />

hierarchy-compaction<br />

technology to achieve high<br />

capacity<br />

◆ Universal ODE solver engine to<br />

achieve high performance<br />

without sacrificing accuracy<br />

◆ Superior flat-mode simulation<br />

with SPICE-precise accuracy<br />

GDSII<br />

Full<br />

Chip<br />

<strong>UltraSim</strong>’s Integrated Flows<br />

Transistor Level<br />

IR Drop / Hierarchical<br />

Post Layout Flow<br />

Nautilus<br />

RCH<br />

Hier<br />

Netlist<br />

<strong>UltraSim</strong><br />

NRCR<br />

Nautilus<br />

VT VT<br />

Timing,<br />

Noise,<br />

Power,<br />

Reliability<br />

◆ Unparalleled native support for widely used models including BSIM3v3, HVMOS,<br />

GP BJT, BTASOI, BSIMPD, BSIM4, Mextram, HICUM, MOS9, MOS11, HCI (hot-carrier<br />

injection), and NBTI.<br />

◆ The most complete circuit analysis available in one simulator, including timing, power,<br />

noise, IR drop, and reliability<br />

◆ Available built-in best-in-class RC reduction with S-parameter technology<br />

◆ Integration of hierarchical layout extraction and simulation that avoids the inefficiencies<br />

and potential risks of hierarchy rebuilt from a flattened netlist<br />

◆ C-level interface (UCI) for behavioral modeling<br />

◆ Ability to add device models or reliability models via the <strong>UltraSim</strong> Model (UCI) and<br />

Reliability Interfaces (UMI)<br />

◆ Support for Solaris and HP 64 bit platforms<br />

◆ Offers the only all-in-one hierarchical circuit analysis solution in the market<br />

<strong>UltraSim</strong> Specifications:<br />

◆ Input: pre- or post-layout SPICE, DSPF, SPEF,<br />

VCD (Value Change Dump file), digital vector file,<br />

and GDSII<br />

◆ Output: nWave waveform file (.fsdb), measure<br />

result file (.mt0), and standard SPICE<br />

IR drop / EM<br />

<strong>UltraSim</strong>

Why <strong>UltraSim</strong>?<br />

Until now, when you wanted simulation results with<br />

SPICE accuracy you had to trade off circuit size,<br />

simulation performance, or both, causing costly<br />

design sign-off delays. With <strong>Celestry</strong>, you no longer<br />

need to sacrifice accuracy, capacity, or performance.<br />

This means you can enjoy benefits not available with<br />

other tools:<br />

◆ Virtually unlimited capacity.<br />

◆ Ultra-accurate and Ultra-fast simulation.<br />

◆ Hierarchical and flat circuit designs in<br />

a single simulator<br />

<strong>UltraSim</strong> is a fast, full-chip hierarchical simulator that<br />

can handle billion transistor memory designs and<br />

above, as well as multi-million transistor logic and<br />

mixed-signal circuits. <strong>UltraSim</strong> combines SPICE<br />

accuracy and virtually unlimited capacity at ultra-fast<br />

speed for your SoC designs. It contains critical DSM<br />

analysis solutions that include timing, noise, power, IR<br />

drop and reliability improvements, and eliminates the<br />

need to use multiple simulation and analysis tools. It<br />

is the industry's only integrated solution offering<br />

hierarchical extraction, RC reduction, and hierarchical<br />

simulation for both hierarchical and flat designs.<br />

<strong>Celestry</strong> <strong>Design</strong> <strong>Technologies</strong>, <strong>Inc</strong>.<br />

<strong>Celestry</strong> is the leading provider of physical design and analysis products<br />

that enable integrated circuit designers to achieve optimal performance from<br />

semiconductor process technologies. The Company offers software and<br />

services to electronic and semiconductor companies involved with the design<br />

of chips that are used in networking, communication, multimedia and<br />

computing products.<br />

Worldwide Headquarters<br />

<strong>Celestry</strong> <strong>Design</strong> <strong>Technologies</strong>, <strong>Inc</strong>.<br />

2560 Junction Avenue,<br />

San Jose, CA 95134-1902, U.S.A.<br />

Phone: (408) 451-1210<br />

Fax: (408) 451-1211<br />

Email: info@celestry.com<br />

http://www.celestry.com