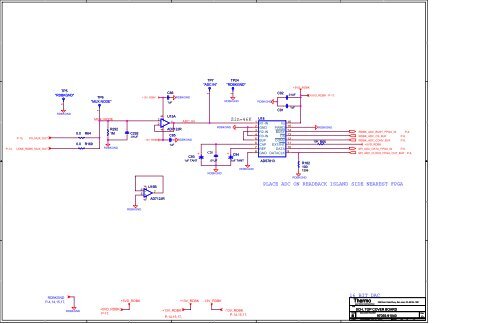

5 5 4 4 3 D D RDBKGND MUX_NODE +13V_RDBK RDBKGND ADC_IN C C P-14, P-15, PS_MUX_OUT LENS_RDBK_MUX_OUT TP5 "RDBKGND" 1 1 -13V_RDBK RDBKGND RDBKGND B B A A RDBKGND P-4,14,15,17, RDBKGND 0.0 R64 0.0 R169 TP6 "MUX NODE" 1 1 R292 1M RDBKGND +5VD_RDBK P-17, C292 .01UF RDBKGND 6 5 3 2 4 8 U15B - 7 + AD712JR 4 8 - + C86 1uF U15A 1 AD712JR C85 1uF +5VD_RDBK +13V_RDBK -13V_RDBK +13V_RDBK P-14,15,17, C93 1uF TANT TP7 "ADC IN" 1 1 3 RDBKGND + C28 + + .01UF TP24 "RDBKGND" 1 1 RDBKGND Zin=46K + C94 + 1uF TANT C94 1uF TANT RDBKGND -13V_RDBK P-14,15,17, RDBKGND U18 1 R1-IN 2 GND 3 R2-IN 4 R3-IN 5 BUF 6 CAP 7 REF 8 GND ADS7813 C92 C91 .01UF 1uF DATACLK 9 DATA 10 EXT/INT 11 CONV 12 CS 13 BUSY 14 PWRD 15 Vs 16 2 +5VD_RDBK RDBKGND 2 R182 100 1206 +5VD_RDBK P-17, RDBKGND 10K R65 1 /RDBK_ADC_BUSY_FPGA_IN P-8, /RDBK_ADC_CS_BUF P-8, /RDBK_ADC_CONV_BUF P-8, +5VD_RDBK SPI_ADC_DATA_FPGA_IN P-6, SPI_ADC_CLOCK_FPGA_OUT_BUF P-6, PLACE ADC ON READBACK ISLAND SIDE NEAREST FPGA 16 BIT DAC <strong>Thermo</strong> 355 River Oaks Pkwy, San Jose, CA 95134-1991 ELECTRON CORPORATION Title Size Document Number Rev B SCH, TOP COVER BOARD 97055-91040 D Date: Wednesday, July 27, 2005 Sheet 16 of 17 1

5 5 4 P-4,13,15, +15V +13V_RDBK P-4,13,15, -13.3V +/- 0.3V -15V -13V_RDBK P-4,13,15, P-4,13,15, +15V VOUT C12 + 10uF 25V tant AGND AGND P-4,13,15, AGND +13V_RDBK RDBKGND RDBKGND P-14,15,16, P-4,13,15, P-4,13,15, -15V AGND AGND Ref=1.21V R2 R1 R26 221 -13V_RDBK RDBKGND RDBKGND P-14,15,16, Ref=1.25V Iadj=55/120uA Iadj=60nA RDBKGND RDBKGND 2 3 VIN TAB 4 U3 LM1084IS-ADJ + C11 R119 10uF 25V tant 121 3 OUT R121 10K R120 2.21K C61 0.1 50V R25 590 1206 5 U4 C60 0.1 50V +C13 +C13 10uF 25V tant LM2991S 6 TAB C14 10uF 25V tant 4 3 D D C C P-4,13,15, +15V +5VD_RDBK B B P-3,4,6,7,8,9,10,15, C53 .33UF DGND +15V AGND RDBKGND RDBKGND +5VD_RDBK RDBKGND P-4,14,15,16, A A DGND ADJ 1 8 VIN VOUT 1 U16 LM78L05ACM GND1 GND2 GND3 GND4 2 3 6 7 DGND P-3,4,6,7,8,9,10,15, +5VD_RDBK P-16, RDBKGND P-4,14,15,16, RDBKGND = READBACK SECTION LOCAL GROUND R28 590 1206 C89 0.1 50V READBACK SECTION LOCAL REGULATORS PD1 1 PD4 1 3 R276 10K 10K R278 10K R274 .01UF C146 -13V_RDBK 2 3 - + U40A 1 AD712JR 4 8 10K R280 VIN 2 EN 4 GND 1 ADJ Vout = Vref x (1+R2/R1) Iadj=60nA Vref = 1.21V -13.3V +/- 0.3V PROTOTYPING AREA +13V_RDBK 1 PD2 2 10K R281 RDBKGND RDBKGND 2 PD3 1 PD6 1 + R277 10K 10K R279 LOCAL READBACK POWER 1 <strong>Thermo</strong> 355 River Oaks Pkwy, San Jose, CA 95134-1991 ELECTRON CORPORATION Title Size Document Number Rev B 10K R275 .01UF C147 6 5 U40B - 7 + AD712JR 4 8 SCH, TOP COVER BOARD 1 PD5 97055-91040 D Date: Wednesday, July 27, 2005 Sheet 17 of 17 1

- Page 1 and 2:

X Y Y X 90 o S3 S3 S3 Line Voltage

- Page 3 and 4:

SPI,VacOK, SYSRst, HVCTRL 5 5 4 4 3

- Page 5 and 6:

5 * ONLY +5.5 VCC USED ON THIS PAGE

- Page 7 and 8:

3 of 4 PWR REG, CONN 5 5 4 4 3 D D

- Page 9:

5 5 4 4 3 3 2 1 THIS DOCUMENT CONTA

- Page 12 and 13:

10 10 9 9 8 8 7 7 6 J J I I H H G G

- Page 14 and 15:

10 10 9 9 8 8 7 7 6 J J I I H H G G

- Page 16 and 17:

5 5 4 4 3 D D C C J1 CON6 1 2 3 4 5

- Page 18:

5 5 4 4 3 3 2 2 1 THIS DOCUMENT CON

- Page 21 and 22:

5 5 4 4 3 D D J1 CON6 1 2 3 4 5 6 Y

- Page 26 and 27:

A A B TP107 THIS DOCUMENT CONTAINS

- Page 28 and 29:

A A B +5V +5V C144 .01UF D D 1DIR S

- Page 30 and 31:

5 5 4 4 3 D CANARY_LED_FPGA_OUT [4]

- Page 32 and 33:

A Digital Valve Section A B +24V-AU

- Page 34 and 35:

A A B +11.75V +11.75V 4 SPARE GAS P

- Page 36 and 37:

A 4 TC- IS ALUMEL TC+ IS CHROMEL [1

- Page 38 and 39:

A A B ( 17.8 to 14.7 KHz ) +5V +15V

- Page 40 and 41:

A A -13.4V 8 4 B 6 6 C55 + + 1K .01

- Page 42 and 43:

5 5 4 4 3 +5V [18] /INJECT_WASTE_LE

- Page 44 and 45:

+60V A TP69 +24V-AUX +24V-AUX A B 4

- Page 46 and 47:

+5V D A A SHUTDOWN_BUF B 2DIR 4 [5]

- Page 48 and 49:

5 5 4 4 3 D CANARY_LED_FPGA_OUT [4]

- Page 50 and 51:

A A B 4 4 FROM FPGA SECTION Digital

- Page 52 and 53:

A A +11.75V B 4 7 + 5 4 - 6 +11.75V

- Page 54 and 55:

A A B 4 4 TC- IS ALUMEL TC+ IS CHRO

- Page 56 and 57:

A A B 4 4 3 3 +15VIN_IG C85 10uF 25

- Page 58 and 59:

A A -13.4V B 4 4 [11] [10] [12] [13

- Page 60 and 61:

[18] [18] +5V +5V 5 5 D D 4 4 3 D D

- Page 75 and 76:

5 5 4 4 ACQU_SP1_DR ACQU_SP1_RFS AC

- Page 77 and 78:

5 5 4 4 3 D D MALDI CABLE CONNECTOR

- Page 79 and 80:

5 5 4 4 3 D D C C B B A A 3 +5V FPG

- Page 81 and 82:

5 5 4 4 3 D D C C +3.3V VDDL ( ~ 2.

- Page 83 and 84:

PA[0:31] 5 5 4 4 3 D D TS211 TS214

- Page 85 and 86:

5 5 PPC_D[0:63] PPC_A[10:31] MODCK[

- Page 87 and 88:

5 RC RC24 D 6 RC 5 RC 100pF-47ohm R

- Page 89 and 90:

5 5 4 4 3 D D CLK_DDS_X3 DDS1_/WR D

- Page 91 and 92:

5 5 4 4 3 D D CLK_FPGA /SRESET /SYS

- Page 93 and 94:

5 5 4 4 3 D D IO_DIR IO_DIR 0 free

- Page 95 and 96: 5 5 4 4 3 D D L0D[0..3] L0ACK L0CLK

- Page 97 and 98: 5 SCAN_SP0_DT U25-1 DS90LV047A U27B

- Page 99 and 100: 5 5 4 4 L0D[0..3] L4D[0..3] 3 D D

- Page 101 and 102: 5 5 4 4 3 3 2 2 1 1 D D C C B B A A

- Page 103 and 104: 5 5 4 4 3 D TURBO POWER +24V Tgnd J

- Page 105: 5 5 4 4 3 3 2 2 1 1 D D C C B B A A

- Page 113 and 114: 5 4 3 2 1 D +5V (NOT LOADED) +/SYS_

- Page 115 and 116: 5 +3.3V 4 3 D +3.3V +3.3V D D D (3.

- Page 117 and 118: 5 4 3 2 1 D C B A [2,10] [3] [3,10]

- Page 119 and 120: 5 5 +150V -150V 4 4 3 D [6] LT_FRON

- Page 121 and 122: [5] FOUT_GT[0..11] FOUT_GT[0..11] 5

- Page 123 and 124: 5 5 4 4 3 R102 ENABLE TP13 /FORCE_8

- Page 125 and 126: 5 5 4 4 3 D D C 10K C ENABLE TTL LE

- Page 127 and 128: 5 4 3 [19] [19] 10K R348 ANALOG_IN1

- Page 129 and 130: 5 4 8 4 - + 3 +13.4V -2.5V_REF2 "8K

- Page 131 and 132: 5 P. C. B. TOP COVER TABLE OF CONTE

- Page 133 and 134: 5 4 CONNECTOR- SPI AND CONTROL 5 4

- Page 135 and 136: 5 LENS D-C FROM ANALOG BOARD 5 4 4

- Page 137 and 138: 5 5 4 4 3 D D (CONFIG DONE) IO_TDO

- Page 139 and 140: 5 PAGE 9 LOCAL POWER & UNUSED FPGA

- Page 141 and 142: FROM PAGE 5 P-5, P-5, M1_DC M0_DC 5

- Page 143 and 144: 5 5 4 4 3 D D P-4,15,17, +15V C C +

- Page 145: 5 SIGNAL READBACKS MUX P-4,11,12, +

- Page 149 and 150: 5 AUXILIARY AC SIGNAL "WAMP" FROM A

- Page 151 and 152: 5 +5VISOL_EXT +5ISOL (2/3A) 1 2 (5/

- Page 153 and 154: 5 5 4 4 3 D D TP61 1 1 2 1 2 1 2 2

- Page 155 and 156: 5 5 4 4 3 D D (2/2A) (2/2A) AUXIN-

- Page 157 and 158: (4/3B,8/1A,8/1A) +18VLOCAL 5 5 4 4

- Page 159 and 160: 5 5 4 4 3 D D GND GND VCC_UNF CLK-

- Page 161 and 162: 5 5 4 4 3 D +5V D AGND [2,3] [3] DA

- Page 163 and 164: 5 5 +15V 4 4 3 - SEE PAGE 1 D +VDF

- Page 165 and 166: AGND 2 5 C37 1 100nF +5V 4 3 2 D [4

- Page 168 and 169: 5 5 4 4 CPU/Digital PCB L0_D[0..7]

- Page 170 and 171: 5 5 4 4 3 D D GND_EARTH J16 J15 C 1

- Page 172 and 173: 5 5 Source PCB 4 4 3 D D J1 A1 1 A2

- Page 189: THIS DOCUMENT CONTAINS PROPRIETARY