You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

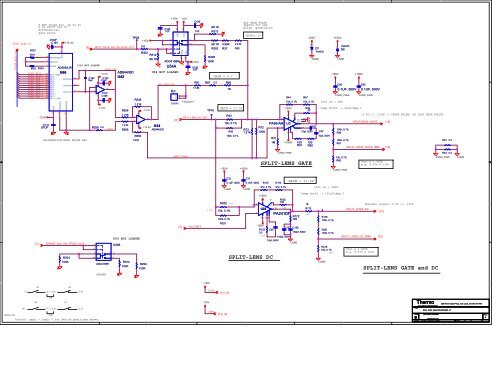

FOUT_SL[0..11]<br />

5<br />

5<br />

4<br />

4<br />

ARET_PA85<br />

3<br />

2<br />

+15V +5V<br />

D<br />

9.8mV steps min. up to 4v<br />

0.2% @100v for 4v<br />

differential,<br />

C183<br />

.1UF<br />

gain error<br />

+15V<br />

FOUT_SL[0..11]<br />

+13.4V<br />

[5] SPLIT_GATE_SW_ON_FPGA_OUT<br />

R333<br />

49.9<br />

R312<br />

10<br />

BIPOFFSET<br />

68.1K<br />

5<br />

REFOUT<br />

-15V<br />

C190 NOT LOADED<br />

D<br />

D<br />

49.9 R334<br />

SGATE_DRV<br />

FOUT_SL11<br />

AD844/SO<br />

U54 NOT LOADED<br />

+13.4V<br />

FOUT_SL10<br />

FOUT_SL9<br />

U42<br />

FOUT_SL8<br />

20VSPAN<br />

FOUT_SL7<br />

FOUT_SL6<br />

BUF_SGATE_DRV<br />

FOUT_SL5<br />

5 +<br />

FOUT_SL4<br />

12<br />

FOUT_SL3<br />

3 -<br />

FOUT_SL2<br />

FOUT_SL1<br />

FOUT_SL0<br />

"SGDRV"<br />

ALT GATE PULSE<br />

approx 20v neg<br />

68.1K<br />

pulse generation<br />

R313<br />

GAIN=1.33<br />

-150V +150V<br />

68.1K 4.99K 2.21K<br />

1N4005<br />

R303 R37 R38<br />

D7<br />

D6<br />

1N4005<br />

LGND<br />

LGND<br />

-150V +150V<br />

GAIN = 5.7<br />

R67 0.0<br />

LGND_PA85 LGND_PA85<br />

init os = 2mV<br />

D<br />

-13.4V<br />

-13.4V<br />

GAIN = 11.22<br />

-150V<br />

temp drift = 50uV/deg C<br />

C<br />

-13.4V<br />

C171<br />

.01UF<br />

ARET1<br />

+13.4V<br />

[6]<br />

SPLIT_LENS_DC_SET<br />

R42<br />

R72<br />

100K<br />

5<br />

-<br />

PA85/AM U3<br />

4<br />

+<br />

mt2<br />

10<br />

mt1<br />

9<br />

OUT<br />

1<br />

cc2<br />

8 C51<br />

10pf, 500V<br />

(0 TO +/- 130V) + (GATE PULSE) OR (ALT GATE PULSE)<br />

SPLITLENS_GATE [19]<br />

C<br />

CALIBRATION/GATE PULSE DAC<br />

100k, 0.1%<br />

+150V 100<br />

R51<br />

100<br />

R52<br />

SPLIT_LENS_GATE_RBK [16]<br />

LGND_PA85<br />

R23 0.0<br />

14<br />

10VSPAN 13<br />

DACOUT 11<br />

7<br />

REFIN<br />

16<br />

BIT12_LSB<br />

BIT11<br />

17 BIT10<br />

18 BIT9<br />

19 BIT8<br />

20 BIT7<br />

21 BIT6<br />

22 BIT5<br />

23 BIT4<br />

24 BIT3<br />

25 BIT2<br />

26 BIT1_MSB<br />

NC<br />

16<br />

I2<br />

AD565AJR<br />

U66<br />

27<br />

.01UF<br />

C156<br />

C66<br />

0.1UF, 500V<br />

R255<br />

TP16<br />

R49<br />

22<br />

R259 0.0<br />

1.21K<br />

1.21K<br />

R256<br />

R43<br />

10k, 0.1%<br />

C52<br />

R250<br />

1.21K<br />

10pf, 500V<br />

R24 0.0<br />

14<br />

NO<br />

2<br />

C2<br />

3<br />

C180<br />

.1UF<br />

TP55<br />

.01UF<br />

15<br />

C1<br />

C181<br />

0.0<br />

1<br />

I1<br />

R302<br />

ADG413BR<br />

U54A<br />

C182<br />

.1UF<br />

C190 C150<br />

10pF<br />

.01UF<br />

R68<br />

17.8k<br />

TL1<br />

1<br />

1<br />

2<br />

2<br />

R249<br />

1.21K<br />

TLOOP2<br />

R292<br />

100K<br />

R66<br />

C65<br />

1K<br />

0.1UF, 500V<br />

R44<br />

R47<br />

51k, 0.1% 51k, 0.1%<br />

3<br />

5<br />

12<br />

U34<br />

AD844/SO<br />

R73<br />

1.21K<br />

100k, 0.1%<br />

R48<br />

R71<br />

1M<br />

100k, 0.1%<br />

R61<br />

temp drift = 130uV/deg C<br />

B 0805<br />

+150V<br />

R135<br />

100<br />

Nominal output: 0 TO +/- 130V<br />

B<br />

9.09k<br />

1206<br />

1206<br />

SPLIT_LENS_DC<br />

[19]<br />

[5] A13_RET<br />

-150V<br />

[5] SPARE_SW_ON_FPGA_OUT 8<br />

I2<br />

U54 NOT LOADED<br />

NC<br />

0805<br />

LGND<br />

SPLIT-LENS DC<br />

R216<br />

15k, 0.1%<br />

0805<br />

SPLIT_LENS_DC_RBK<br />

Vout x 0.0698<br />

e.g. 9.07v @ 130v<br />

[16]<br />

LGND<br />

11<br />

7<br />

C2<br />

NO 6<br />

R202<br />

5<br />

-<br />

1K<br />

10k, 0.1%<br />

100k, 0.1%<br />

U22 OUT<br />

21<br />

7<br />

+ PA241DF<br />

R172<br />

100<br />

R173<br />

R176<br />

100k, 0.1%<br />

R203<br />

R122<br />

0.0<br />

C90<br />

C127 C128<br />

150pf, 500V<br />

R201<br />

100k, 0.1%<br />

R304<br />

9<br />

I1<br />

10<br />

C1<br />

U54B<br />

150pf, 500V<br />

10pf, 500V<br />

100K<br />

ADG413BR<br />

R314<br />

100K<br />

R293<br />

100K<br />

A +150V<br />

A<br />

S1 S2<br />

(3) (2)(15)<br />

IN<br />

(14)<br />

S4<br />

S3<br />

(6) (7)(10)<br />

(11)<br />

ADG413B<br />

IN<br />

Control input = Logic 0 for Switch positions shown.<br />

VEE<br />

9<br />

REFGND<br />

6<br />

VCC 4<br />

PWRGND<br />

15<br />

14<br />

7<br />

SPRARE<br />

14 7<br />

-<br />

+<br />

VDD 13<br />

GND<br />

5<br />

VCC 12<br />

VSS<br />

4<br />

-150V<br />

+150V<br />

-150V<br />

-150V<br />

[7,8,19]<br />

[7,8,19]<br />

+150V<br />

3<br />

6<br />

V-<br />

V+<br />

cc1<br />

3<br />

7<br />

2<br />

cL<br />

SPLIT-LENS GATE<br />

13<br />

V+<br />

V-<br />

12<br />

CP1<br />

CP2<br />

17<br />

19<br />

15<br />

CL<br />

1<br />

2 1<br />

2<br />

15k, 0.1%<br />

R65<br />

LGND_PA85<br />

C32<br />

0.1UF, 500V<br />

C31<br />

0.1UF, 500V R175 R174<br />

GAIN = 11.22<br />

LGND<br />

LGND<br />

51k, 0.1% 51k, 0.1%<br />

init os = 30mV<br />

2<br />

Vout x 0.0698<br />

e.g. 9.07v @ 130v<br />

SPLIT-LENS GATE and DC<br />

1<br />

LGND_PA85<br />

LGND<br />

<strong>Thermo</strong> 355 River Oaks Pkwy, San Jose, CA 95134-1991<br />

ELECTRON CORPORATION<br />

Title<br />

SCH, PCB, ANALOG BOARD, LT<br />

Size B<br />

Document Number 97055-91030<br />

Rev<br />

B<br />

Date: Friday, April 07, 2006<br />

Sheet 9 of 19<br />

1