in PDF Format - Embedded-Control-Europe.com

in PDF Format - Embedded-Control-Europe.com

in PDF Format - Embedded-Control-Europe.com

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Stop with bor<strong>in</strong>g presentations!,<br />

Long before there were <strong>com</strong>puters<br />

there were bad presentations. And<br />

there still are. All of you attend<strong>in</strong>g<br />

presentations regularly experience<br />

this by suffer<strong>in</strong>g bor<strong>in</strong>g hours<br />

where conference speakers fail to<br />

use your time and theirs wisely.<br />

Most of the presentations are too<br />

detailed for the audience, use visuals<br />

that are far too <strong>com</strong>plex, and<br />

generally show a lack of passion<br />

from the orator.<br />

When you th<strong>in</strong>k of technical pre-<br />

Michael Moesslang<br />

sentations, you may th<strong>in</strong>k of dark<br />

rooms, masses of slides, and a<br />

voice at the front of the room narrat<strong>in</strong>g <strong>in</strong> detail the facts for the audience.<br />

However, there are def<strong>in</strong>itely exceptions and ways to deliver<br />

a speech that manage to reach the goal content-wise and at the<br />

same time persuade and enterta<strong>in</strong> the audience. The worst belief is<br />

that your presentation has to be like presentations have always been<br />

<strong>in</strong> your <strong>com</strong>pany, as that is the standard. Be<strong>in</strong>g standard - another<br />

word is mediocre - never leads to be<strong>in</strong>g conv<strong>in</strong>c<strong>in</strong>g. And isn’t this<br />

what it is all about? To really conv<strong>in</strong>ce your audience? Lots of technicians<br />

th<strong>in</strong>k they are not <strong>in</strong> sales and therefore they do not need to<br />

be conv<strong>in</strong>c<strong>in</strong>g. So very wrong! To conv<strong>in</strong>ce an audience is sell<strong>in</strong>g observations,<br />

conclusions, and projections. That also is sales, isn’t it?<br />

To reach your audience and have it leave satisfied and impressed after<br />

your presentation, you’d better th<strong>in</strong>k about break<strong>in</strong>g several of these<br />

standard patterns and relate to some of the rules of human <strong>com</strong>munication.<br />

One of these is to speak <strong>in</strong> a clear and understandable<br />

way with as few technical abbreviations or terms as possible. Never<br />

assume that your audience has the same level of technical knowledge<br />

as yourself. Slides filled with masses of text <strong>in</strong> small fonts do not support<br />

but rather destroy the impact of your words. Visuals are far better<br />

and should clearly show what you wish to po<strong>in</strong>t out. Never forget<br />

that your audience will see the visual - maybe a technical illustration<br />

or a spreadsheet - for the very first time. They will need time<br />

to understand and are not able to listen to you dur<strong>in</strong>g that process.<br />

People cannot read and listen at the same time. To get and keep an<br />

alert audience you should speak with suspense and use loops. A loop<br />

is a teas<strong>in</strong>g announcement creat<strong>in</strong>g suspense. In the follow<strong>in</strong>g the audience<br />

will wait curiously for the later clarification of facts and therefore<br />

stay with you.<br />

If you are go<strong>in</strong>g to get up <strong>in</strong> front of your audience and say that the<br />

design of your strategy matters, that the design of your software or<br />

hardware matters, that your content matters, then at the very least the<br />

structure and visuals you use also need to be the result of credible design.<br />

Then, and only then, can you give presentations that are better<br />

than the rest out there. And w<strong>in</strong> over your audience.<br />

Yours s<strong>in</strong>cerely,<br />

Michael Moesslang<br />

VIEWPOINT<br />

Viewfullarticleonl<strong>in</strong>eathttp://www.<strong>Embedded</strong>-Know-how.<strong>com</strong><br />

3 November 2009<br />

V-10_2009-TM-4805<br />

SH7216<br />

Ultra Fast Flash Microcontroller<br />

The perfect s<strong>in</strong>gle-chip solution for automation,<br />

servo motor and <strong>in</strong>verter applications.<br />

72 different devices offer various <strong>com</strong>b<strong>in</strong>ations of<br />

functionality, memory capacity and package.<br />

Performance:<br />

� Superskalar SH2A-Core 200 MHz/400 DMIPS<br />

� Float<strong>in</strong>g-Po<strong>in</strong>t-Unit 400 MFLOPS<br />

� 1 MB S<strong>in</strong>gle-Cycle <strong>Embedded</strong> Flash<br />

� 128 KB SRAM<br />

Peripherals:<br />

� Multi-functional Timer Units<br />

� 100 MHz Complementary PWM<br />

� Fast 12-bit A/D Converter<br />

Connectivity:<br />

� Ethernet MAC<br />

� CAN<br />

� USB 2.0 Full Speed<br />

Renesas the no.1 supplier of<br />

microcontroller products offers<br />

best <strong>in</strong> class Flash technology,<br />

proven quality and long life time support.<br />

You will like it – once you try it!<br />

Get <strong>in</strong> contact with MSC to evaluate the SH7216 now!<br />

Visit our ToolGuide-Webshop:<br />

www.msc-toolguide.<strong>com</strong><br />

MSC Vertriebs GmbH<br />

+49 7249 910-520 · micros-renesas@msc-ge.<strong>com</strong><br />

www.msc-ge.<strong>com</strong>/ad/micros-renesas

CONTENTS<br />

Viewpo<strong>in</strong>t 3<br />

Cover Story<br />

High performance semiconductors<br />

paved the way for electric bicycles 6<br />

Industrial <strong>Control</strong><br />

Mak<strong>in</strong>g <strong>in</strong>dustrial systems safer<br />

by meet<strong>in</strong>g the IEC 60730 standards 9<br />

Tools & Software<br />

Design kits for PCBs featur<strong>in</strong>g<br />

embedded Atom processors 12<br />

Rapid prototyp<strong>in</strong>g us<strong>in</strong>g software<br />

configuration management 14<br />

Tools & Software<br />

Different design patterns for<br />

<strong>in</strong>tegrat<strong>in</strong>g Simul<strong>in</strong>k with Stateflow 18<br />

Micros & DSPs<br />

S<strong>in</strong>gle-chip coherent multiprocess<strong>in</strong>g<br />

boosts embedded performance 20<br />

Accelerat<strong>in</strong>g early stages of the design<br />

cycle with i.MX processors 24<br />

FPGAs, PLDs & ASICs<br />

The drive to lower power opens up<br />

new FPGA applications 26<br />

Flexible power system management<br />

capabilities for embedded systems 29<br />

Low-power FPGA solutions for<br />

graphics applications featur<strong>in</strong>g LCDs 31<br />

Highly configurable embedded 32-bit<br />

RISC processor for FPGA applications 33<br />

Product News 36<br />

Cover Photo<br />

Inf<strong>in</strong>eon Technologies<br />

November 2009 4<br />

High performance semiconductors<br />

paved the way for electric bicycles PAGE 6<br />

This article describes the technical progress <strong>in</strong> electronics and<br />

power electronics which enables nowadays e-bikes as mass products<br />

for green personal transportation.<br />

Mak<strong>in</strong>g <strong>in</strong>dustrial systems safer<br />

by meet<strong>in</strong>g the IEC 60730 standards PAGE 9<br />

This article discusses the different classes of the IEC 60730 standards<br />

for appliances and <strong>in</strong>dustrial control and shows how MCU<br />

manufacturers can help by deliver<strong>in</strong>g hardware features, such as<br />

<strong>in</strong>dependent watchdogs, CRC eng<strong>in</strong>es, ECC and software periodic<br />

test rout<strong>in</strong>es to ga<strong>in</strong> IEC 60730 <strong>com</strong>pliance.<br />

Rapid prototyp<strong>in</strong>g us<strong>in</strong>g software<br />

configuration management PAGE 14<br />

Software configuration management<br />

contributes powerfully to<br />

rapid prototyp<strong>in</strong>g of both hardware<br />

and software for embedded<br />

systems, especially with the <strong>com</strong>munication<br />

problems aris<strong>in</strong>g from<br />

far-flung design teams and -<br />

system architects. This article describes latest techniques such as<br />

lazy copy<strong>in</strong>g and reverse delta archiv<strong>in</strong>g.<br />

S<strong>in</strong>gle-chip coherent multiprocess<strong>in</strong>g<br />

boosts embedded performance PAGE 20<br />

This article expla<strong>in</strong>s how the MIPS32 1004K coherent process<strong>in</strong>g<br />

system br<strong>in</strong>gs together MIPS multi-thread<strong>in</strong>g and coherent SMP<br />

<strong>in</strong> a s<strong>in</strong>gle IP block to provide scalable, high-density embedded<br />

<strong>com</strong>put<strong>in</strong>g power.<br />

The drive to lower power opens up<br />

new FPGA applications PAGE 26<br />

Power is often a more important<br />

design consideration today than<br />

performance. Portable, powerconscious<br />

electronics demands<br />

low-power <strong>com</strong>ponents of every<br />

k<strong>in</strong>d, a demand <strong>in</strong>creas<strong>in</strong>gly met<br />

by FPGAs. This article highlights<br />

the trend and technology by<br />

examples drawn from many fields.<br />

Flexible power system management<br />

capabilities for embedded systems PAGE 29<br />

This article shows how programmable<br />

logic devices are well suited<br />

to enable flexible and efficient<br />

power management functions,<br />

especially for battery-powered<br />

embedded systems.

®<br />

The INTEGRITY RTOS<br />

Certified and Deployed Technology<br />

The INTEGRITY RTOS is deployed and certified to:<br />

Avionics: DO-178B Level A, certified: 2002<br />

Industrial: IEC 61508 SIL 3, certified: 2006<br />

Medical: FDA Class III, approved: 2007<br />

Security: EAL6+ High Robustness, certified: 2008<br />

France:<br />

Israel:<br />

Sweden:<br />

Please contact your local office<br />

for your free Certification Information Pack.<br />

+33 (0) 143 143 700<br />

+972 (0)9 9584060<br />

+46 (0)8 750 82 70<br />

www.ghs.<strong>com</strong><br />

Germany: +49 (0)228 43 30 777<br />

Netherlands: +31 (0)33 4613363<br />

UK: +44 (0)1844 267950<br />

Copyright © 2009 Green Hills Software, Inc. Green Hills, the Green Hills logo and INTEGRITY are trademarks of Green Hills Software, Inc. <strong>in</strong> the U.S.and/or<br />

<strong>in</strong>ternationally. All other trademarks are the property of their respective owners.

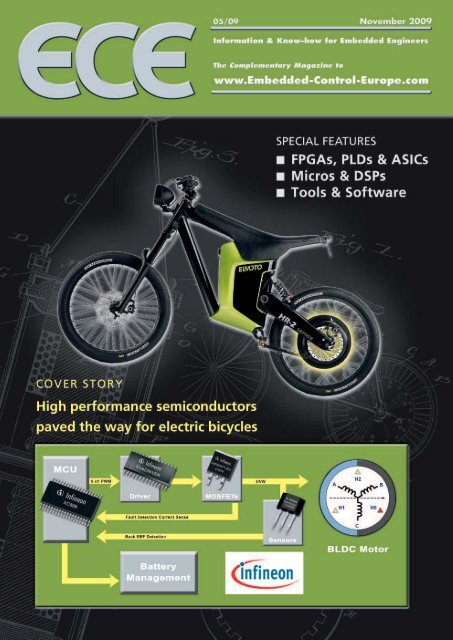

COVER STORY<br />

High performance semiconductors<br />

paved the way for electric bicycles<br />

By Juergen Hoika, Inf<strong>in</strong>eon Technologies<br />

November 2009<br />

This article describes<br />

the technical progress<br />

<strong>in</strong> electronics and power<br />

electronics which enables<br />

nowadays e-bikes as mass<br />

products for green personal<br />

transportation.<br />

■ Electrical drives are not new <strong>in</strong> transport:<br />

Trams and tra<strong>in</strong>s have been runn<strong>in</strong>g on electricity<br />

for a long time. Electrically driven vehicles<br />

have been around s<strong>in</strong>ce the 1830s and more<br />

than 100 years have now passed s<strong>in</strong>ce the <strong>in</strong>vention<br />

of the electric bicycle. In 1895, Ogden<br />

Bolton, Jr. applied for the first patent for a battery-operated<br />

bicycle with a 6-pole brush<br />

motor built <strong>in</strong>to the rear wheel. Development<br />

and <strong>com</strong>mercialization of the electric bicycle<br />

have <strong>com</strong>e a long way <strong>in</strong> those 110 years. From<br />

a technological po<strong>in</strong>t of view, the breakthrough<br />

undoubtedly came with the availability of<br />

long-lived accumulators - such as the lithiumpolymer<br />

battery - and with the <strong>in</strong>crease <strong>in</strong> the<br />

power and efficiency of electric motors brought<br />

about by the use of electronics. Electric bikes are<br />

part of a wide range of Light Electric Vehicles<br />

(LEVs). Generally designed for one person and<br />

small cargo capacity, electric bike range, speed,<br />

and costs are moderate, provid<strong>in</strong>g clean, quiet,<br />

convenient and efficient local transportation.<br />

What is that market? Worldwide, bicycles and<br />

scooters are the number one mode of transportation.<br />

An estimated one billion bicycles are<br />

<strong>in</strong> daily use, and more than 100 million new bicycles<br />

enter the world market each year. Ch<strong>in</strong>a,<br />

for example, has 34 bicycles per 100 <strong>in</strong>habitants<br />

and has a market for more than 30 million bicycles<br />

annually. So it is no surprise, that the<br />

<strong>com</strong>mercialization of the electric bicycle has<br />

been driven ma<strong>in</strong>ly by its <strong>in</strong>troduction and subsidization<br />

<strong>in</strong> Ch<strong>in</strong>a. The production figure of<br />

only 40,000 electric bicycles <strong>in</strong> Ch<strong>in</strong>a <strong>in</strong> 1998<br />

rose to 10 million with<strong>in</strong> 7 years. By 2008 this<br />

figure had almost doubled. What caused this<br />

breakthrough for the electric bicycle <strong>in</strong> Ch<strong>in</strong>a?<br />

These conveyances became the favorite means<br />

of transport for the Ch<strong>in</strong>ese populace because<br />

they offer a cheap, convenient form of personal<br />

mobility as an attractive alternative to public<br />

transport and the push-bike. In Ch<strong>in</strong>a,<br />

electric bicycles are subsidized by national and<br />

many local governments, thanks to their low<br />

energy consumption and freedom from emission<br />

– a particularly important aspect <strong>in</strong><br />

Ch<strong>in</strong>a`s overloaded urban areas. They have already-<br />

quite literally - overtaken the conventional<br />

bicycle <strong>in</strong> some cities.<br />

In <strong>Europe</strong>, the electric bicycle suffered from a<br />

negative image for many years. It was heavy, and<br />

was regarded as un-sportsmanlike, and found a<br />

place more as an aid than as a means of transport<br />

<strong>in</strong> its own right. In view of the stream of<br />

announcements of new, so-called “Pedelecs”<br />

(Pedal Electric Cycles), these times seem to be<br />

over at last. Cities <strong>in</strong> <strong>Europe</strong> are also beg<strong>in</strong>n<strong>in</strong>g<br />

to <strong>in</strong>vest <strong>in</strong> this means of transport. In Switzerland,<br />

too, the Elektrovelo is boom<strong>in</strong>g, thanks to<br />

the NewRide subsidization programme; <strong>in</strong> Austria,<br />

the Klima:aktiv-Programme subsidizes the<br />

purchase of a Pedelec to the tune of up to € 400,<br />

6<br />

Figure 1. Us<strong>in</strong>g the benefits of<br />

high performance semiconductors<br />

electric bicycles provide<br />

clean, quiet, convenient and<br />

efficient local transportation<br />

and <strong>in</strong> numerous German cities, such as<br />

Stuttgart and Kaiserslautern, new mobility concepts<br />

<strong>in</strong>volv<strong>in</strong>g electric bicycles are be<strong>in</strong>g<br />

launched. New bus<strong>in</strong>ess concepts are emerg<strong>in</strong>g.<br />

Personal mobility is be<strong>com</strong><strong>in</strong>g a service, analogous<br />

to mobile <strong>com</strong>munications. Companies<br />

such as Movelo rent out Pedelecs, and also offer<br />

battery exchange <strong>in</strong> <strong>in</strong>terest<strong>in</strong>g holiday resorts<br />

and urban areas. This way, users pay for mobility<br />

as required, and do not have to worry about<br />

servic<strong>in</strong>g, such as battery ma<strong>in</strong>tenance. Electric<br />

bicycles have also been <strong>in</strong> service <strong>in</strong> a <strong>com</strong>mercial<br />

environment for years; <strong>in</strong> many countries,<br />

mail is already be<strong>in</strong>g delivered by Pedelec.<br />

The technical breakthrough for electric bicycles<br />

came with the use of electronics. These control<br />

electric motors efficiently, thus optimiz<strong>in</strong>g<br />

performance and battery life. The most frequently<br />

used topography <strong>in</strong> series production<br />

of electric bicycles today is a brushless DC<br />

motor (BLDC) with Hall sensors. A basic electric<br />

bicycle runs on a BLDC motor, is powered<br />

by batteries and controlled from an ECU (<strong>Embedded</strong><br />

<strong>Control</strong> Unit). The BLDC motor for the<br />

electric bicycle is of the standard three phase<br />

trapezoidal type, typically rated at a few hundred<br />

watts and the battery voltage is usually<br />

36V or 48V. Almost all the electronics <strong>in</strong> the<br />

electric bicycle are found <strong>in</strong> the ECU, it conta<strong>in</strong>s<br />

the <strong>in</strong>verter circuit for the motor; temperature<br />

sensor; fault detection; SMPS; analogue and dig-

MAKING ONE OF THESE?<br />

...THEN YOU NEED THREADX<br />

ThreadX is Express Logic's small, fast,<br />

T H R<br />

E<br />

A<br />

D<br />

royalty-free RTOS that powers over<br />

500 million electronic devices, with<br />

millions more produced each month. That's because ThreadX is easy-to-use,<br />

mak<strong>in</strong>g your development job easier and more likely to f<strong>in</strong>ish on time or even<br />

ahead of schedule. Developers of consumer, medical, network<strong>in</strong>g, <strong>in</strong>dustrial,<br />

aerospace, and automotive electronics products rely on ThreadX for their<br />

RTOS. Call today to f<strong>in</strong>d out how ThreadX can help you br<strong>in</strong>g your next<br />

electronic product to market faster. Make it better - make it with ThreadX.<br />

For a free evaluation copy, call one of our <strong>Europe</strong>an<br />

Offices or visit www.rtos.<strong>com</strong><br />

Express<br />

Logic (UK) ( UUK)Ltd<br />

Ltd<br />

4b 4b Empire<br />

Court Cour t<br />

Prospect<br />

Hill<br />

Redditch B97 4DA 4D DA<br />

UK<br />

Tel: Teel:<br />

+44 (0) 152 1527 27 597007<br />

Fax: +44 (0) 1527 152 27 597701<br />

Email: <strong>in</strong>fo@expresslogic.co.uk<br />

<strong>in</strong>fo@expr resslogic.co.uk<br />

Express<br />

Logic GmbH G GmbH<br />

Hanover Office:<br />

Am Saegewerk 2a<br />

D-29308 DD-29308 29308 W WW<strong>in</strong>sen<br />

<strong>in</strong>se en<br />

Germany<br />

Tel: Teel:<br />

+49 5143 911-303 9<br />

Fax: +49 +49 5143 911-305<br />

Email <strong>in</strong>fo@expresslogic.de<br />

Express<br />

Logic<br />

GGmbH<br />

mmbH<br />

Munich Office:<br />

Eichbaumstr. Eichbaumstr.80<br />

80<br />

D-85635 DD-85635 85635 Siegertsbrunn<br />

Sieger ts sbr unn<br />

Germany<br />

Tel: Teel:<br />

+49 8102 784-5865 78 84-5865<br />

Fax: +49 8102 784-5866 78 84-5866<br />

Email: sales@expresslogic.de<br />

• Small S Small<br />

footpr<strong>in</strong>t<br />

• Low LLow<br />

over overhead head<br />

•Full • F Full<br />

source<br />

code<br />

• Easy-to-use<br />

E Easy-to-use<br />

•• Field-proven<br />

F Field-proven<br />

•• Low LLow<br />

cost<br />

•Royalty-free<br />

• R Royalty-free<br />

Copyright © 2008, Express<br />

Logic, , Inc.<br />

ThreadX Thrr<br />

eadX is a rregistered<br />

egistered<br />

trademark of Ex Express xpress<br />

Logic, Inc. All other trademarks trademar rks are<br />

the property<br />

of their respective<br />

owners.

COVER STORY<br />

Figure 2. Market forecast for electric bicycles <strong>in</strong> Ch<strong>in</strong>a, iSuppli, June 2009<br />

Figure 3. Block diagram of a BLDC motor control <strong>in</strong> a Pedelec<br />

ital I/Os; and f<strong>in</strong>ally the controller itself. Some<br />

ECUs have advanced features such as remote<br />

controlled alarm and electric horn as well. All of<br />

these as well as the wir<strong>in</strong>g are usually packed<br />

<strong>in</strong>to a robust and very <strong>com</strong>pact metal box.<br />

Inf<strong>in</strong>eon is the lead<strong>in</strong>g <strong>com</strong>pany <strong>in</strong> the area of<br />

semiconductors for electric bicycles. In about<br />

every second electric bicycle worldwide, the<br />

motor is controlled by an 8-bit microcontroller<br />

of Inf<strong>in</strong>eon XC800 family. One reason for this<br />

is that the product characteristics are tailormade<br />

for this application at low cost. The special<br />

functions <strong>in</strong> the microcontroller (fast<br />

ADC, Capture/Compare unit, etc.) make for<br />

particularly fast signal recognition and signal<br />

generation to switch the <strong>in</strong>dividual phase currents<br />

of the motor. The cyclist notices this by<br />

the excellent performance of the electric bicycle<br />

<strong>in</strong> every load state. Another reason is high<br />

quality and reliability as products are build on<br />

automotive proven technologies.<br />

Figure 4. Reference design of the control unit<br />

Further essential elements of the motor<br />

electronics are the robust, <strong>in</strong>telligent power<br />

semiconductors. The Inf<strong>in</strong>eon EiceDRIVER<br />

portfolio <strong>in</strong>cludes full-bridge drivers to control<br />

power devices such as IGBTs or MOS transistors<br />

<strong>in</strong> 3-phase systems with a block<strong>in</strong>g voltage<br />

of up to 600V. Based on Silicon-On-Insulator<br />

(SOI) technology, these devices are very resistant<br />

to negative transient voltages. Unlike standard<br />

monolithic high-voltage IC technology,<br />

Inf<strong>in</strong>eon SOI th<strong>in</strong>-film technology does not<br />

have parasitic thyristor structures. The result is<br />

outstand<strong>in</strong>g robustness aga<strong>in</strong>st latch-up when<br />

exposed to extreme temperature and voltage<br />

conditions. Furthermore, they switch off<br />

automatically <strong>in</strong> many error modes to prevent<br />

destruction of the electronics or the motor.<br />

The e-bike is one example of the broad range of<br />

applications which benefits from the unique<br />

features of the OptiMOS2 or OptiMOS3 power<br />

MOSFETs, offer<strong>in</strong>g a <strong>com</strong>b<strong>in</strong>ation of the lowest<br />

available on-state resistance <strong>in</strong> <strong>com</strong>parable<br />

packages and lowest gate drive requirements.<br />

These MOSFETs feature excellent switch<strong>in</strong>g<br />

performance, they help to <strong>in</strong>crease power density<br />

<strong>in</strong> the application and consequently they<br />

save energy. In addition these MOSFETs provide<br />

the highest immunity to dynamic turn-on.<br />

Hall sensors from Inf<strong>in</strong>eon, such as the<br />

TLE4946, were developed specifically for motor<br />

control applications, and are characterized <strong>in</strong><br />

November 2009 8<br />

the electric bicycle by their precision and immunity<br />

to <strong>in</strong>terference signals. Inf<strong>in</strong>eon have<br />

been offer<strong>in</strong>g solutions for electronics <strong>in</strong> electric<br />

bicycles for over three years now. Meanwhile<br />

there is a second generation of a reference<br />

system available, that <strong>com</strong>prises both the reference<br />

circuit with all active and passive <strong>com</strong>ponents,<br />

and a reference platform for software<br />

development. The software library for electric<br />

bicycles <strong>in</strong>cludes functions such as evaluation of<br />

<strong>in</strong>put units, battery voltage monitor<strong>in</strong>g, and<br />

measurement of phase currents.<br />

On the electronics side, the semiconductor<br />

<strong>com</strong>ponents will provide designers with sufficient<br />

<strong>com</strong>put<strong>in</strong>g performance, <strong>in</strong>creased switch<strong>in</strong>g<br />

efficiency, and more safety and diagnosis<br />

functionstocreateanewclassofelectricbicycles.<br />

The 8-bit XC800 microcontroller series offers<br />

derivatives with a vector <strong>com</strong>puter, which<br />

allows implementation of Field Oriented<br />

<strong>Control</strong> (FOC) for the price of a standard 8-bit<br />

microcontroller. Thanks to FOC, non-sensor<br />

topologies <strong>in</strong> the electric drives of the Pedelecs<br />

are possible, and the efficiency of the motor is<br />

further <strong>in</strong>creased. If even more processor<br />

performance needed <strong>in</strong> motor scooters and<br />

motorcycles, Inf<strong>in</strong>eon offers the 16-bit microcontroller<br />

series XE166 with the same peripheral<br />

functions, for example signal generation<br />

(Capture Compare Unit), as <strong>in</strong> the XC800 series.<br />

This creates a scalable development platform.<br />

The mentioned reference system is under<br />

cont<strong>in</strong>uous further development, <strong>in</strong> order to<br />

shorten the development times for the motor<br />

control unit with the help of more software<br />

functions. In addition to this, Inf<strong>in</strong>eon offers<br />

the auto-code generator DAvE Drive, which<br />

generates, with just a few mouse-clicks, block<strong>com</strong>mutation<br />

or FOC code that is optimized to<br />

the microcontroller architecture.<br />

Electric drives for bicycles know no limits. The<br />

next generation <strong>in</strong> the upper performance<br />

range is go<strong>in</strong>g <strong>in</strong>to mass production: the socalled<br />

E-Scooter. The electric motor has also<br />

found its way <strong>in</strong>to the motor-cycl<strong>in</strong>g world. The<br />

12th of June 2009 saw the first “Zero Emission<br />

Motorcycle Race”. The w<strong>in</strong>ner was Chris Heath<br />

on a Native TTGXP, which reached 160km/h on<br />

the legendary Isle of Man circuit. New bus<strong>in</strong>ess<br />

models, like the rent<strong>in</strong>g of electric bicycles <strong>in</strong><br />

urban areas and holiday resorts, will certa<strong>in</strong>ly<br />

remove any obstacles <strong>in</strong> the run-up to Pedelec<br />

mobility with regard to the charg<strong>in</strong>g and ma<strong>in</strong>tenance<br />

of batteries. It will be excit<strong>in</strong>g to see<br />

what <strong>in</strong>terest<strong>in</strong>g k<strong>in</strong>ds of electric-powered<br />

bicycle will <strong>com</strong>e on the market <strong>in</strong> the <strong>com</strong><strong>in</strong>g<br />

months and years, and what concepts cities and<br />

towns will offer consumers with regard to<br />

personal mobility with Pedelecs. The technological<br />

prerequisites to support the next generations<br />

of e-bikes are all already <strong>in</strong> place. ■

Mak<strong>in</strong>g <strong>in</strong>dustrial systems safer<br />

by meet<strong>in</strong>g the IEC 60730 standards<br />

By Dugald Campbell, Freescale<br />

This article discusses the different<br />

classes of the IEC 60730 standards<br />

for appliances and <strong>in</strong>dustrial control<br />

and shows how MCU manufacturers<br />

can help by deliver<strong>in</strong>g hardware features,<br />

such as <strong>in</strong>dependent<br />

watchdogs, CRC eng<strong>in</strong>es, ECC and<br />

software periodic test rout<strong>in</strong>es to<br />

ga<strong>in</strong> IEC 60730 <strong>com</strong>pliance.<br />

■ With the <strong>in</strong>troduction of the International<br />

Electrotechnical Commission IEC 60730 standards<br />

series, household appliance and <strong>in</strong>dustrial<br />

control manufacturers now have to consider <strong>in</strong>troduc<strong>in</strong>g<br />

new design enhancements to their<br />

automatic electronic controls that ensure their<br />

<strong>com</strong>ponents’ safe and reliable operation. IEC<br />

60730 standards series on automatic electrical<br />

controls for household and similar use, Part 1,<br />

is one of many standards used by large appliance<br />

manufacturers. IEC 60730 is also referenced<br />

by other standards for other systems,<br />

such as boiler ignition systems (EN 297) and<br />

medical electrical equipment (IEC 60601), that<br />

cover general requirements for basic safety and<br />

essential performance.<br />

IEC 60730 discusses mechanical, electrical,<br />

electronic, environmental, endurance, EMC<br />

and abnormal operation of AC appliances. IEC<br />

60730 Annex H: Requirements for Electronic<br />

<strong>Control</strong>s, specifically relates to microcontrollers<br />

(MCUs), detail<strong>in</strong>g new test and diagnostic<br />

methods to ensure the safety of embedded control<br />

hardware and software for automatic systems.<br />

Its focus is to provide measures to ensure<br />

that the embedded software design functions<br />

safely and reliably if a fault condition occurs<br />

with<strong>in</strong> the system sub-<strong>com</strong>ponents, such as<br />

CPU, memory, <strong>in</strong>terrupts, program counter,<br />

<strong>com</strong>munication <strong>in</strong>terfaces and software<br />

program flow.<br />

Today the majority of automatic electronic controls<br />

use s<strong>in</strong>gle-chip MCUs (microprocessors<br />

with embedded memory and <strong>in</strong>put/output<br />

peripherals). Manufacturers develop real-time<br />

embedded software that executes with<strong>in</strong> the<br />

MCU and provides the hidden <strong>in</strong>telligence that<br />

controls an electro-mechanical device. Measures<br />

detailed <strong>in</strong> IEC 60730 are critical to help<br />

ensure that such an electro-mechanical device<br />

INDUSTRIAL CONTROL<br />

will not be hazardous to users. IEC 60730/EN<br />

60335 segments automatic control products<br />

<strong>in</strong>to three different classifications. Class A: not<br />

<strong>in</strong>tended to be relied upon for the safety of the<br />

equipment, Class B: to prevent unsafe operation<br />

of the controlled equipment. Class C: to prevent<br />

special hazards.<br />

Class A controls are deemed not hazardous if<br />

the software malfunctions, and thus IEC 60730<br />

does not require the manufacturer to implement<br />

system checks. A class B system likely has<br />

automatic controls where a possible hazard<br />

could occur and result <strong>in</strong> harm to a human<br />

be<strong>in</strong>g. Generally, the controls are characterized<br />

by how the class B system is implemented and<br />

if the critical safety system features some form<br />

of redundancy (<strong>in</strong> hardware and/or software).<br />

If the automatic control relies on a specific safety<br />

function and there is no redundancy, then<br />

the system will likely be deemed class C. If the<br />

9 November 2009

INDUSTRIAL CONTROL<br />

automatic controls directly control an explosive<br />

substance, such as gasol<strong>in</strong>e, the system will be<br />

deemed class C. The various <strong>com</strong>ponents of an<br />

embedded system that must be tested are summarized<br />

<strong>in</strong> Table H.11.12.7. of IEC 60730<br />

Annex H. For each of the listed class B and class<br />

C <strong>com</strong>ponents, optional measures are given for<br />

the manufacturer to deploy with<strong>in</strong> the automatic<br />

system. Table 1 summarizes the required<br />

<strong>com</strong>ponents that need to be tested and monitored<br />

to ensure the system meets class B specifications.<br />

CPU registers can be monitored by<br />

us<strong>in</strong>g a periodic test rout<strong>in</strong>e that writes a 0xAA<br />

pattern followed by a 0x55 pattern to verify no<br />

register bits are stuck at a 1 or 0 state. A CPU<br />

program counter can be similarly tested with a<br />

0x55/0xAA pattern by plac<strong>in</strong>g small rout<strong>in</strong>es at<br />

addresses 0x5555.. and 0xAAA.. that have return<br />

from subrout<strong>in</strong>e <strong>in</strong>structions (RTS). The CPU<br />

should execute these rout<strong>in</strong>es and then exam<strong>in</strong>e<br />

the contents <strong>in</strong> the stack po<strong>in</strong>ter.<br />

Interrupt handl<strong>in</strong>g and execution is verified by<br />

a method called <strong>in</strong>dependent time base monitor<strong>in</strong>g.<br />

This requires a regular periodic check<br />

from a time base <strong>in</strong>dependent of the CPU<br />

clock. An example is hav<strong>in</strong>g a real-time <strong>in</strong>terrupt<br />

clocked by an <strong>in</strong>dependent 1 kHz oscillator<br />

that <strong>in</strong>cludes a check on token counters of<br />

all <strong>in</strong>terrupts utilized. If any irregularity is discovered,<br />

then the CPU is forced <strong>in</strong>to a rout<strong>in</strong>e<br />

that places the application <strong>in</strong> a safe state. The<br />

clock or the CPU clock is also required to be<br />

checked by an <strong>in</strong>dependent time-base monitor.<br />

An <strong>in</strong>dependent clocked timer, such as a realtime<br />

<strong>in</strong>terrupt, can be used to make timestamps<br />

at regular <strong>in</strong>tervals from a CPU clocked timer.<br />

Additionally, Freescale MCUs feature a watchdog<br />

counter that is clocked by an <strong>in</strong>dependent<br />

timebase. This feature provides an additional<br />

check if the CPU clock stops, ensur<strong>in</strong>g that an<br />

asynchronous reset occurs to place the system<br />

November 2009<br />

<strong>in</strong> a safe state. Watchdogs that are clocked from<br />

the same source as the CPU cannot provide this<br />

protection. For <strong>in</strong>variable memory (flash), the<br />

manufacturer is required to check for s<strong>in</strong>gle bit<br />

faults, which can be performed us<strong>in</strong>g a modified<br />

checksum rout<strong>in</strong>e. The ma<strong>in</strong> issue here is<br />

that there is no <strong>com</strong>mon method or rout<strong>in</strong>e for<br />

deploy<strong>in</strong>g a modified checksum. Manufacturers<br />

have taken the approach of deploy<strong>in</strong>g the<br />

program memory cycle redundancy check<strong>in</strong>g<br />

(CRC) signatures because it is well understood<br />

and has a reliable mechanism for identify<strong>in</strong>g<br />

s<strong>in</strong>gle-bit errors. After all bytes have been read,<br />

each byte is run through a CRC calculation.<br />

Once that calculation is made, it can be <strong>com</strong>pared<br />

to a so-named golden CRC signature to<br />

verify no s<strong>in</strong>gle faults exist. Freescale has created<br />

a hardware CRC eng<strong>in</strong>e that will provide a<br />

fast method of creat<strong>in</strong>g a 16-bit CRC.<br />

For small memory footpr<strong>in</strong>ts, the CRC can be<br />

calculated <strong>in</strong> software with<strong>in</strong> a reasonable time<br />

frame. Variable memory (RAM) can be verified<br />

as hav<strong>in</strong>g no DC faults by execut<strong>in</strong>g a periodic<br />

test us<strong>in</strong>g the well-known March C or March X<br />

test pattern. These March patterns require a lot<br />

of execution time for most embedded systems,<br />

and the designer must segment the RAM <strong>in</strong>to favorable<br />

sizes, check<strong>in</strong>g each segment <strong>in</strong> sequence.<br />

Freescale has developed March C and<br />

March X tests for HCS08 and MC56F80xx controllers,<br />

which can help speed up the development<br />

of a class B system. The March X pattern is<br />

a subset of March C where only steps 1, 2, 5 and<br />

6 are executed, thus sav<strong>in</strong>g CPU execution time.<br />

Components 4.3 address<strong>in</strong>g, 5.0 <strong>in</strong>ternal data<br />

path and 5.2 address<strong>in</strong>g (table 1) are covered by<br />

implement<strong>in</strong>g the above variable and <strong>in</strong>variable<br />

periodic test rout<strong>in</strong>es. 6.0 external <strong>com</strong>munication<br />

refers to protocols that are used to <strong>in</strong>terface<br />

with <strong>com</strong>ponents external to the automatic<br />

control system, such as UART <strong>com</strong>munication<br />

between a control board and a motor<br />

control board. There are several optional measures<br />

to ensure reliable <strong>com</strong>munication, such as<br />

add<strong>in</strong>g a 16-bit CRC to data transferred via the<br />

10<br />

<strong>com</strong>munication port and transfer redundancy,<br />

which is simply send<strong>in</strong>g data twice. A tim<strong>in</strong>g<br />

<strong>com</strong>ponent, as <strong>in</strong> the wrong po<strong>in</strong>t <strong>in</strong> time, and<br />

sequence of external data exchanges can be reliably<br />

checked us<strong>in</strong>g <strong>in</strong>dependent time slot<br />

monitor<strong>in</strong>g, the same as used for <strong>in</strong>terrupts.<br />

Components 7.0 periphery, 7.2.1 analog I/O<br />

and 7.2.2 analog multiplexers (table 1) require<br />

the manufacturer to carry out plausibility<br />

checks prior to application use. These employ<br />

a number of techniques, <strong>in</strong>clud<strong>in</strong>g mak<strong>in</strong>g<br />

upper/lower limits on ADC <strong>in</strong>puts, redundant<br />

ADC <strong>in</strong>puts to check multiplexer, and short circuit<br />

and open circuit tests of adjacent p<strong>in</strong>s to a<br />

safety-critical signal l<strong>in</strong>e. Subject<strong>in</strong>g a system<br />

design to all the measures described will provide<br />

IEC 60730 Class B <strong>com</strong>pliance.<br />

Table 2 summarizes the required <strong>com</strong>ponents<br />

that need to be tested and monitored to ensure<br />

the system meets class C specifications. For class<br />

C systems there is one additional <strong>com</strong>ponent<br />

that needs to be tested and more str<strong>in</strong>gent<br />

measures placed on four of the exist<strong>in</strong>g <strong>com</strong>ponents.<br />

The additional <strong>com</strong>ponent is 1.2<br />

CPU <strong>in</strong>struction decod<strong>in</strong>g and execution,<br />

which is required to check that the CPU is decod<strong>in</strong>g<br />

the <strong>in</strong>structions used to perform the<br />

safety feature. Table H.11.12.7 of IEC 60730<br />

Annex H provides three optional measures to<br />

test for this <strong>com</strong>ponent: Dual CPU implementation<br />

with <strong>com</strong>parison, <strong>in</strong>ternal hardware detection,<br />

and periodic self-test us<strong>in</strong>g equivalence<br />

class test.<br />

Freescale Power Architecture products, such as<br />

the MPC5510 family, have dual CPU cores that<br />

can execute simultaneously, and the execution<br />

results can be <strong>com</strong>pared prior to execut<strong>in</strong>g a<br />

safety function. Internal hardware detection<br />

through error code correction (ECC) is provided,<br />

which uses a form of parity when read<strong>in</strong>g<br />

program <strong>in</strong>structions and can automatically<br />

correct s<strong>in</strong>gle parity errors. This feature can be<br />

found on S12X family members, such as the<br />

MC9S12XE100, as well as the MPC5510 fami-

Table 1. Class B <strong>com</strong>ponents that need test<strong>in</strong>g<br />

and monitor<strong>in</strong>g<br />

ly, which has ECC on both flash and RAM<br />

memory. For 8-bit S08 CPU, a CPU <strong>in</strong>struction<br />

test is developed that can be executed prior to<br />

runn<strong>in</strong>g power-up on the end application.<br />

This test rout<strong>in</strong>e requires approximately 2<br />

Kbytes of program memory, but it is modular,<br />

which allows remov<strong>in</strong>g tests for <strong>in</strong>structions<br />

that are not utilized by the safety application.<br />

Execution time for the full test is 3666 CPU<br />

BUS cycles (183.3 s at 20MHz). TÜV SÜD has<br />

validated and certified this test rout<strong>in</strong>e to be<br />

IEC 60730-<strong>com</strong>pliant, and the test rout<strong>in</strong>e is<br />

available for Freescale customers. In addition to<br />

the extra <strong>com</strong>ponent to be tested, there are four<br />

<strong>com</strong>ponents of class C systems that require<br />

more str<strong>in</strong>gent test<strong>in</strong>g: CPU register test, variable<br />

memory (RAM), <strong>in</strong>variable memory<br />

(flash), and external <strong>com</strong>munications.<br />

CPU register test requires the manufacturer to<br />

check for DC faults on the CPU registers, which<br />

can be ac<strong>com</strong>plished us<strong>in</strong>g a walk<strong>in</strong>g 1s and<br />

walk<strong>in</strong>g 0s pattern. The last figure <strong>in</strong> this article<br />

shows a walk<strong>in</strong>g 1s pattern on an 8-bit register.<br />

By execut<strong>in</strong>g this pattern and confirm<strong>in</strong>g<br />

Industrial Comput<strong>in</strong>g & Communications Forum<br />

At SPS/IPC/DRIVES, the Boards & Solutions<br />

team is runn<strong>in</strong>g the Industrial Comput<strong>in</strong>g &<br />

Communications Forum - a 3-day programme<br />

with presentations about technical trends,<br />

product <strong>in</strong>novations, strategies and applications.<br />

Major Topics of the ICC Forum are:<br />

✓ Industrial PCs, Panel PCs, Box PCs<br />

✓ Industrial Communications<br />

✓ Small Form Factor Boards<br />

✓ Tools & Software for <strong>in</strong>dustrial applications<br />

The Industrial Comput<strong>in</strong>g & Communications<br />

Forum is located <strong>in</strong> Hall 8, Stand 528<br />

close to the gateway to Hall 7. It is a theater-<br />

Table 2. Class C <strong>com</strong>ponents that need test<strong>in</strong>g<br />

and monitor<strong>in</strong>g<br />

the data at each step, all DC faults will be exposed.<br />

A walk<strong>in</strong>g 0s pattern is similar to the<br />

walk<strong>in</strong>g 1s pattern with all data <strong>in</strong>verted, and it<br />

should also be performed. Variable memory<br />

(RAM) test<strong>in</strong>g requires the same techniques as<br />

used for the CPU register (walk<strong>in</strong>g 1s and walk<strong>in</strong>g<br />

0s to check for DC faults). For RAM arrays<br />

of >2 Kbtes, execut<strong>in</strong>g such a test can be time<br />

consum<strong>in</strong>g. However, the manufacturer can<br />

split the RAM array <strong>in</strong>to small segments (32 to<br />

128 bytes), and each RAM segment can be tested<br />

<strong>in</strong> sequence while execut<strong>in</strong>g the application.<br />

Note that the manufacturer will likely need to<br />

pause the application while it tests each application<br />

and disable <strong>in</strong>terrupts to ensure no program<br />

variables are <strong>in</strong>advertently corrupted.<br />

Freescale has developed a walk<strong>in</strong>g 1s and walk<strong>in</strong>g<br />

0s RAM test for the HC9S08AC60 MCU,<br />

which segments the RAM <strong>in</strong>to 48-byte segments.<br />

This is modular software, however, and<br />

can be easily modified to support larger or<br />

smaller RAM arrays. Invariable memory (flash)<br />

style presentation area with free access for all<br />

exhibition visitors.<br />

11<br />

INDUSTRIAL CONTROL<br />

for class C systems requires the user to look for<br />

99.6 percent coverage of all bits. This can be covered<br />

by ECC or by a 32-bit CRC. Optionally, redundant<br />

memory can be deployed where the<br />

CPU can periodically check that both arrays<br />

<strong>com</strong>pare. For external <strong>com</strong>munications <strong>com</strong>ponents<br />

meet<strong>in</strong>g class C specifications, the<br />

manufacturer is required to implement either a<br />

32-bitCRCtodatatransfersordeploydataredundancy,<br />

where the data is sent at least twice<br />

and the redundant data is modified <strong>in</strong> some<br />

form,suchas<strong>in</strong>vert<strong>in</strong>gthesecondpieceofdata.<br />

Another option is to use <strong>com</strong>parison or redundant<br />

functional channels with <strong>com</strong>parison. By<br />

us<strong>in</strong>g two <strong>com</strong>munications ports and send<strong>in</strong>g<br />

the data on both ports, the software can <strong>com</strong>pare<br />

the received data to ensure they match.<br />

Periodic test rout<strong>in</strong>es for Freescale MCUs were developed<br />

that users can deploy <strong>in</strong> their application<br />

code. These developed rout<strong>in</strong>es have each been<br />

certified by a certification body, such as VDE or<br />

TÜVSÜD,tomeetIEC60730requirements.■<br />

Product News<br />

■ Rutronik: low-power high-precision<br />

op amps<br />

Microchip Technology presents three new families<br />

of low-power, high-precision operational<br />

amplifiers broaden<strong>in</strong>g the portfolio of high precision<br />

op amps with Ga<strong>in</strong> Bandwidth Product<br />

from 10kHz to 50MHz. The new products are<br />

available at distributor Rutronik now.<br />

News ID 450<br />

■ Toshiba: 32nm mSATA and half-slim<br />

SSD modules<br />

Toshiba Electronics <strong>Europe</strong> has announced a<br />

series of solid state drive modules us<strong>in</strong>g the<br />

latest generation Toshiba 32nm MLC NAND<br />

flash. The Toshiba SG2 modules are offered <strong>in</strong><br />

two types, one based on the new low-profile<br />

m<strong>in</strong>i-SATA <strong>in</strong>terface standard and the other<br />

aHalf-Slimtype,whichusesaSATAconnector.<br />

The drives are available <strong>in</strong> 30GB and<br />

62GB modules. Volume production will start<br />

<strong>in</strong> October.<br />

News ID 486<br />

■ Fujitsu: graphics SoC with <strong>in</strong>tegrated<br />

dual APIX l<strong>in</strong>k<br />

Fujitsu has announced the MB86R02 ‘Jade D’,<br />

the latest device <strong>in</strong> its ‘Jade’ SoC family,<br />

which <strong>in</strong>corporates 32-bit ARM926EJ-S CPU<br />

core and the <strong>com</strong>pany’s graphics processor<br />

‘Coral PA’. Based on Fujitsu’s proprietary<br />

90nm CMOS process technology, ‘Jade D’ is<br />

optimised for automotive applications requir<strong>in</strong>g<br />

high CPU performance <strong>com</strong>b<strong>in</strong>ed<br />

with sophisticated 2D/3D graphics.<br />

News ID 549<br />

November 2009

TOOLS &SOFTWARE<br />

Design kits for PCBs featur<strong>in</strong>g<br />

embedded Atom processors<br />

By Dirk Mueller, FlowCAD<br />

This article describes the<br />

issues <strong>in</strong> PCB design associated<br />

with the latest fast embedded<br />

processors. Design kits<br />

<strong>in</strong>clud<strong>in</strong>g all design rules and<br />

a reference board are offered<br />

by most semiconductor <strong>com</strong>panies,<br />

normally subject to<br />

non-disclosure agreements.<br />

■ With the new generation of embedded<br />

processors like Intel Atom, the PCB design<br />

process moves to another level of <strong>com</strong>plexity.<br />

The numbers of design constra<strong>in</strong>ts are dramatically<br />

<strong>in</strong>creased and the tolerances of these<br />

design rules are gett<strong>in</strong>g tighter and tighter.<br />

M<strong>in</strong>iaturization also adds a new dimension to<br />

the design challenges. In the past it was possible<br />

to build an embedded PC from scratch, but<br />

today it is crucial to implement and reuse<br />

proven models and reference designs from<br />

semiconductor vendors like Intel, Xil<strong>in</strong>x, etc, <strong>in</strong><br />

order to reach design closure without miss<strong>in</strong>g<br />

project deadl<strong>in</strong>es. With today’s high performance<br />

semiconductors, differential high speed<br />

must not only control differential impedance<br />

and parallelism of the two tracks, but the signals<br />

must also be controlled <strong>in</strong> length for each track,<br />

and match the length of all other tracks <strong>in</strong> the<br />

same bus <strong>in</strong>clud<strong>in</strong>g control signals.<br />

In a typical Atom design you f<strong>in</strong>d a memory<br />

control hub, which is connected via the 64-bit<br />

wide front side bus to the microcontroller. External<br />

<strong>com</strong>munication is made through a PCIexpress<br />

<strong>in</strong>terface and the DDR2 memory is<br />

connected through a one-hundred-bit wide<br />

memory <strong>in</strong>terface to each memory <strong>com</strong>ponent.<br />

In embedded systems, the dimensions of a PCB<br />

are similar to the size of a credit card. Real es-<br />

tate on the board is limited also by the given locations<br />

of the Com Express connector and the<br />

mount<strong>in</strong>g holes. To make the design process<br />

really challeng<strong>in</strong>g the manufactur<strong>in</strong>g costs<br />

have to be low, so the number of layers available<br />

for the designer to select from is typically reduced<br />

to below ten.<br />

Many semiconductor <strong>com</strong>panies offer their<br />

customers design kits under a non–disclosure<br />

agreement. These kits <strong>in</strong>clude the def<strong>in</strong>ition of<br />

all required design rules, and these rules are<br />

managed <strong>in</strong> a constra<strong>in</strong>t management system,<br />

where each value for the net length, impedance<br />

and delta[CDSI1] to the other nets <strong>in</strong> a group<br />

are collected. To get the real value of the electrical<br />

net, the length from the last transistor on<br />

the CPU chip has to be measured to the first<br />

<strong>in</strong>put buffer from the [CDSI2] memory control<br />

hub. S<strong>in</strong>ce the chips are not mounted directly<br />

onto the PCB, the <strong>in</strong>ternal length of the signal<br />

<strong>in</strong>side the IC has to be added to this calculation.<br />

This value is called p<strong>in</strong> delay. This value always<br />

existed, but the tolerances were bigger, so the <strong>in</strong>ternal<br />

p<strong>in</strong> delay could be ignored to calculate<br />

length of signals. In modern designs two th<strong>in</strong>gs<br />

have changed: the tolerances are reduced due to<br />

<strong>in</strong>creases <strong>in</strong> the front side bus speed i.e. 533<br />

MHz, and the topology is made with signals<br />

which have to be of the same length. So the p<strong>in</strong><br />

November 2009 12<br />

Figure 1. Example of an<br />

embedded module based<br />

on Atom processor<br />

delay can no longer be ignored and each <strong>in</strong>dividual<br />

value for each p<strong>in</strong> has to be respected.<br />

Spac<strong>in</strong>g of decoupl<strong>in</strong>g capacitors to the Vcc and<br />

GND p<strong>in</strong>s of the IC is gett<strong>in</strong>g smaller if the<br />

transmission speed is <strong>in</strong>creas<strong>in</strong>g. The efficient<br />

distance for a ceramic capacitor with a low<br />

equivalent series resistance is only several millimeters,<br />

so the placement of these <strong>com</strong>ponents<br />

should rema<strong>in</strong> the same as the orig<strong>in</strong>al floor<br />

plann<strong>in</strong>g of the reference design kit. In the constra<strong>in</strong>t<br />

manager this maximum spac<strong>in</strong>g can be<br />

attached to the capacitor and <strong>in</strong>dividual p<strong>in</strong>s of<br />

an IC, so dur<strong>in</strong>g placement of the capacitor the<br />

designer gets a visual feedback if the <strong>com</strong>ponent<br />

is placed too far away. A wrong placement<br />

would reduce the power <strong>in</strong>tegrity (PI) and<br />

destabilize the <strong>com</strong>plete power delivery system,<br />

which can result <strong>in</strong> malfunction of the module.<br />

Memory modules like DDR2 have to be connected<br />

to the memory hub controller. These<br />

connections of the address and data busses have<br />

very <strong>com</strong>plex structures and detailed rules<br />

how to connect the <strong>in</strong>dividual signals. Such a<br />

structure is called topology. For one DDR2 signal,<br />

the signal will split like a tree <strong>in</strong>to different<br />

branches. The impedance for parts of the<br />

branch has to be different because of signal <strong>in</strong>tegrity<br />

(SI) requirements. After a split the two<br />

new branches have to be matched <strong>in</strong> length to

Figure 2. Design rules are managed <strong>in</strong> a constra<strong>in</strong>t manager<br />

Figure 3: DDR2 topology<br />

each other. After two splits the last four branches have to be matched <strong>in</strong><br />

length. In a 64-bit wide data bus the length of all nets have to be matched,<br />

consequently the total number of <strong>com</strong>b<strong>in</strong>ed matched length rules is huge<br />

and nearly impossible to manage manually. In Allegro PCB editor and<br />

constra<strong>in</strong>t manager the control of such a <strong>com</strong>plex task is implemented<br />

<strong>in</strong> an efficient and user-friendly way. From the design kit the requirements<br />

for a s<strong>in</strong>gle net are stored <strong>in</strong> the constra<strong>in</strong>t manager (match<strong>in</strong>g <strong>in</strong>clud<strong>in</strong>g<br />

tolerances). In a second step the match<strong>in</strong>g rules between all nets <strong>in</strong><br />

a bus (and groups of nets <strong>in</strong> the bus) are def<strong>in</strong>ed as a second hierarchy<br />

of rules, and <strong>in</strong>clude also the specified tolerances. This <strong>com</strong>plete rule set<br />

for DDR2 is def<strong>in</strong>ed <strong>in</strong> one topology. While the def<strong>in</strong>ition is stored <strong>in</strong> the<br />

constra<strong>in</strong>t manager, the PCB editor will give onl<strong>in</strong>e feedback if a value is<br />

violat<strong>in</strong>g the specification. Allegro PCB editor will also display the value<br />

of the tolerances <strong>in</strong> a visual way, so the adjustment of all matched groups<br />

is made fast and flawless.<br />

An Atom design kit <strong>in</strong>cludes a <strong>com</strong>plete multi-page schematic of a tested<br />

reference design <strong>in</strong> OrCAD capture format or alternatively <strong>in</strong> Allegro<br />

design entry HDL. So if you start the first Atom design, you do not have<br />

to start from scratch, but can reuse the <strong>com</strong>ponent symbols as well as<br />

several pages of the reference design. In the kit is also a <strong>com</strong>plete layout<br />

of a reference design made <strong>in</strong> Allegro PCB editor. With this design, you<br />

can see how the fan-out of the Atom CPU was made and how decoupl<strong>in</strong>g<br />

capacitors were placed under and around the CPU. The processor fan-out<br />

is only one task of a design. You will also f<strong>in</strong>d structures for the power<br />

delivery system, which power regulators were used and how the power<br />

delivery system was designed to fulfil the <strong>com</strong>plex demand of the CPU.<br />

All def<strong>in</strong>itions of the PCB footpr<strong>in</strong>t can be extracted from the reference<br />

design and stored <strong>in</strong> the local library, which saves a lot of time. ■<br />

TOOLS &SOFTWARE<br />

13 November 2009

TOOLS &SOFTWARE<br />

Rapid prototyp<strong>in</strong>g us<strong>in</strong>g software<br />

configuration management<br />

By Dave Robertson, Perforce Software<br />

■ Over time, faster and better tools and processes<br />

have steadily shortened the time-to-market<br />

for new embedded systems. As ever more projects<br />

<strong>in</strong>volve the collaboration of <strong>in</strong>creas<strong>in</strong>g<br />

numbers of different design teams and third<br />

parties spread across the world, produc<strong>in</strong>g<br />

work<strong>in</strong>g prototypes is be<strong>com</strong><strong>in</strong>g as much a logistical,<br />

as a technological, challenge. New development<br />

techniques have emerged that try to<br />

give more control <strong>in</strong> this area. Methods such as<br />

agile development view the entire development<br />

process as a series of small step releases, where<br />

the software evolves and is cont<strong>in</strong>uously updated.<br />

Increas<strong>in</strong>gly used by enterprise software<br />

development teams, Agile is mak<strong>in</strong>g some <strong>in</strong>roads<br />

<strong>in</strong>to embedded projects as it can provide<br />

extra value to customers.<br />

However, the sheer global scale of some embedded<br />

systems development projects, and the<br />

quantity and size of the data and variants <strong>in</strong>volved,<br />

takes this beyond merely a process problem.<br />

One way these challenges can be addressed<br />

is with software configuration management<br />

(SCM) systems. Designed for traditional software<br />

development, modern SCM systems can<br />

handle large numbers of files and variants for<br />

globally distributed eng<strong>in</strong>eer<strong>in</strong>g teams. They<br />

also enable rapid prototyp<strong>in</strong>g <strong>in</strong>volv<strong>in</strong>g multiple<br />

sites and many hundreds of collaborat<strong>in</strong>g<br />

developers. It is rare to <strong>com</strong>e across a new product<br />

that is built <strong>com</strong>pletely from scratch. More<br />

November 2009<br />

Software configuration management<br />

contributes powerfully<br />

to rapid prototyp<strong>in</strong>g of<br />

both hardware and software<br />

for embedded systems, especially<br />

with the <strong>com</strong>munication<br />

problems aris<strong>in</strong>g from farflung<br />

design teams and -<br />

system architects. This article<br />

describes latest techniques<br />

such as lazy copy<strong>in</strong>g and<br />

reverse delta archiv<strong>in</strong>g.<br />

likely there is a mixture of reliable <strong>com</strong>modity<br />

<strong>com</strong>ponents - hardware and software - with<br />

new proprietary IP and custom logic that cements<br />

all the parts together. The location of the<br />

teams and track<strong>in</strong>g the large quantity of items<br />

<strong>in</strong>volved means that pull<strong>in</strong>g all the pieces together<br />

<strong>in</strong> a timely way to produce a work<strong>in</strong>g<br />

prototype or early release candidates is a major<br />

issue.<br />

Prototypes <strong>in</strong>creas<strong>in</strong>gly require the management<br />

of many different types of file - the output<br />

from EDA tools, hardware design schematics,<br />

software source code and so on, along with<br />

track<strong>in</strong>g their use and reuse. As the development<br />

progresses, the files go through many revisions<br />

and are <strong>com</strong>b<strong>in</strong>ed <strong>in</strong> a range of different<br />

configurations. The capture, organisation<br />

and management of this <strong>com</strong>plex array of <strong>in</strong>formation<br />

and ensur<strong>in</strong>g the right versions of<br />

the right files are where they need to be, be<strong>com</strong>es<br />

non-trivial. This often leads to a significant<br />

reduction <strong>in</strong> productivity dur<strong>in</strong>g the<br />

prototyp<strong>in</strong>g stage as well as the overall development<br />

time.<br />

At its simplest, an SCM system tracks and manages<br />

the digital files created <strong>in</strong> the design and<br />

development process. Basic features of the system<br />

<strong>in</strong>clude version control, change history, and<br />

track<strong>in</strong>g the files that have been checked out of<br />

the system for edit<strong>in</strong>g. The more advanced sys-<br />

14<br />

Figure 1. Many variants and<br />

prototypes can be born out of<br />

a good idea.<br />

tems provide configuration management, the<br />

act of record<strong>in</strong>g an arbitrary collection of files<br />

and their versions that have some special significance<br />

to the project and may need to be recalled<br />

or recreated at some future po<strong>in</strong>t. To help<br />

with the strenuous demands of an embedded<br />

systems development, an SCM system needs to<br />

support rapid prototyp<strong>in</strong>g and distributed<br />

development teams.<br />

There are many contributors <strong>in</strong>volved <strong>in</strong> develop<strong>in</strong>g<br />

the f<strong>in</strong>ished hardware and software.<br />

Software developers and hardware eng<strong>in</strong>eers<br />

have already received a mention. But there are<br />

also documentation writers and testers, too.<br />

And, for truly <strong>in</strong>tegrated teams, the team may<br />

<strong>in</strong>clude the web designers build<strong>in</strong>g the product<br />

pages, and the market<strong>in</strong>g folks produc<strong>in</strong>g collateral<br />

and so on. Their <strong>com</strong>b<strong>in</strong>ed output <strong>in</strong>volves<br />

the need to handle the wide range of file<br />

types that the tools of the team generate - from<br />

graphical behavioural models, through the<br />

VHDL for the hardware design and C text files<br />

for the middleware and applications, to the<br />

EDA design files for the hardware and the libraries<br />

and <strong>com</strong>piled b<strong>in</strong>ary code for the software.<br />

And not forgett<strong>in</strong>g all the test and verification<br />

files for both the hardware and software.<br />

To be effective, the SCM system has to be both<br />

fast and secure, but also easy to use so as to have<br />

m<strong>in</strong>imal impact on the day-to-day activities of

Figure 2. Propagat<strong>in</strong>g bug fixes and new features between variants is a management challenge.<br />

Figure 3. Lazy copy<strong>in</strong>g uses fact that variant is identical to orig<strong>in</strong>al to save space when branch<strong>in</strong>g.<br />

users.Sav<strong>in</strong>gchangestofilesmustbequickand<br />

easy, otherwise users will avoid us<strong>in</strong>g or pay lip<br />

service to the system and the time and management<br />

advantages are missed. Similarly, the<br />

latest revisions from teams and third parties<br />

around the world should be available as soon as<br />

possible otherwise time is lost by hav<strong>in</strong>g to sort<br />

out <strong>com</strong>pet<strong>in</strong>g revisions. All the revisions have<br />

to be stored safely and securely with the m<strong>in</strong>imum<br />

of cost <strong>in</strong> storage space and retrieval time.<br />

At the start, it is nearly impossible to predict<br />

howdeeporbroadthescopeofaproductwill<br />

be<strong>com</strong>e. If the IP be<strong>in</strong>g developed be<strong>com</strong>es a<br />

<strong>com</strong>mercial success, there will be high demand<br />

for new variants for use <strong>in</strong> different environments<br />

or applications. As the scope <strong>in</strong>creases <strong>in</strong><br />

scale, the SCM system will need to cope. Two<br />

techniques SCM systems use to address this are<br />

lazy copy<strong>in</strong>g and reverse delta archiv<strong>in</strong>g.<br />

Lazy copy<strong>in</strong>g recognises that when a variant is<br />

first created it is identical to the orig<strong>in</strong>al. A<br />

po<strong>in</strong>ter to the orig<strong>in</strong>al is all that is created,<br />

rather than a physical copy. As the variant is<br />

modified new storage is reserved, and then only<br />

15<br />

TOOLS &SOFTWARE<br />

to record the differences between it and the<br />

orig<strong>in</strong>al. This applies to a variant consist<strong>in</strong>g of<br />

any number of files so ensur<strong>in</strong>g m<strong>in</strong>imal storage<br />

space requirements. Reverse delta archiv<strong>in</strong>g<br />

is where the historical record of a file just consists<br />

of the latest version of a file stored <strong>in</strong> its entirety<br />

along with the difference - or delta - between<br />

it and the previous version, and the version<br />

before that and so on. Older versions are<br />

recreated by tak<strong>in</strong>g the latest and apply<strong>in</strong>g the<br />

relevant deltas <strong>in</strong> reverse order until the required<br />

version is recreated. This technique<br />

recognises that the most <strong>com</strong>monly accessed<br />

versions are usually the most recent and also<br />

that the differences between versions are often<br />

fairly small. Like lazy copy<strong>in</strong>g, the reverse delta<br />

technique aids performance by reduc<strong>in</strong>g both<br />

disk space needs and <strong>com</strong>putation time as the<br />

size of the project <strong>in</strong>creases.<br />

So, by avoid<strong>in</strong>g the creation of a physical copy,<br />

variants constitut<strong>in</strong>g any number of files can be<br />

created quickly - a key advantage <strong>in</strong> fast prototyp<strong>in</strong>g,<br />

where system architects and product developers<br />

can be work<strong>in</strong>g on separate ideas<br />

alongside the ma<strong>in</strong> development stream. These<br />

November 2009

TOOLS &SOFTWARE<br />

prototype developments have to be isolated<br />

from all other development streams until all or<br />

parts of them are ready to be <strong>in</strong>troduced back<br />

<strong>in</strong>to the ma<strong>in</strong> design. This can be a problem for<br />

some SCM systems, but is a vital requirement to<br />

allow eng<strong>in</strong>eers to <strong>in</strong>novate and prototype <strong>in</strong><br />

the way they want to. Aga<strong>in</strong>, lazy copy<strong>in</strong>g<br />

helps by mak<strong>in</strong>g it straightforward for just the<br />

differences to be copied back <strong>in</strong>to the ma<strong>in</strong><br />

development stream from the variant.<br />

With the relative ease that differences can be<br />

moved backwards and forwards between variant<br />

streams, feature enhancements, bug track<strong>in</strong>g<br />

and resolution is simplified too. New features<br />

added, or bugs resolved dur<strong>in</strong>g development,<br />

can be applied easily and propagated<br />

around the various development areas, and a<br />

<strong>com</strong>plete audit trail is preserved with<strong>in</strong> the<br />

SCM system.<br />

Increas<strong>in</strong>g product <strong>com</strong>plexity has seen architects<br />

and developers be<strong>com</strong><strong>in</strong>g more focused on<br />

<strong>in</strong>novation <strong>in</strong> their specialist areas. To deliver<br />

products, it is <strong>com</strong>monplace that third-party IP<br />

is used for some elements of both hardware,<br />

such as processor and <strong>in</strong>terface IP, and software,<br />

with drivers and middleware. So, for rapid pro-<br />

■ IAR: ZigBee tool for sens<strong>in</strong>g and control<br />

applications<br />

IAR Systems and Ember have teamed together<br />

to deliver a reliable and easy to use ZigBee development<br />

and debugg<strong>in</strong>g platform for sens<strong>in</strong>g<br />

and control applications such as smart meter<strong>in</strong>g<br />

and home automation. Ember recently<br />

launched the EM35x InSight Development<br />

Kit. The EM35x Insight Development Kit is<br />

built around ARM Cortex-M3 processor technology<br />

and <strong>com</strong>es with the latest version of IAR<br />

<strong>Embedded</strong> Workbench for ARM, a <strong>com</strong>pletely<br />

<strong>in</strong>tegrated development environment for embedded<br />

applications.<br />

News ID 489<br />

■ pls: UDE supports VaST’s virtual processor<br />

models and tools<br />

pls Programmierbare Logik & Systeme and<br />

VaST Systems have established a cooperation<br />

with the goal to further simplify the simulation<br />

of automotive software applications by <strong>in</strong>terfac<strong>in</strong>g<br />

their products. Developers use VaST tools<br />

totyp<strong>in</strong>g benefits to be felt, these third party elements<br />

have to be <strong>in</strong>tegrated <strong>in</strong>to the prototype<br />

as easily as possible. With agile development<br />

techniques and a cont<strong>in</strong>uous development<br />

cycle, new versions of third party IP can be fed<br />

<strong>in</strong> from the software team and third party partners<br />

almost cont<strong>in</strong>uously. With the right SCM<br />

system, all these <strong>in</strong>puts can be added to a safe<br />

area where eng<strong>in</strong>eers can look at the latest <strong>com</strong>ponent<br />

versions and assess whether they can be<br />

used <strong>in</strong> the prototype. They can also access the<br />

latest hardware elements and test them out to<br />

see whether they are appropriate to be <strong>in</strong>cluded<br />

<strong>in</strong> the prototype.<br />

Large organisations often struggle to ma<strong>in</strong>ta<strong>in</strong><br />

the pace of <strong>in</strong>novation that they had when they<br />

were smaller. Develop<strong>in</strong>g prototypes <strong>in</strong> either<br />

hardware or software usually requires br<strong>in</strong>g<strong>in</strong>g<br />

together far-flung design teams and system architects,<br />

and deal<strong>in</strong>g with the <strong>in</strong>herent <strong>com</strong>munication<br />

challenges. Mak<strong>in</strong>g this a fast and<br />

efficient process can be a struggle. SCM systems<br />

are also be<strong>in</strong>g used to speed up the prototyp<strong>in</strong>g<br />

process dramatically by l<strong>in</strong>k<strong>in</strong>g sites and teams<br />

around the world, rather than hav<strong>in</strong>g to have a<br />

prototype handled by one team <strong>in</strong> one place.<br />

NVIDIA, for <strong>in</strong>stance, uses SCM to l<strong>in</strong>k <strong>in</strong>ter-<br />

Product News<br />

to create and simulate virtual prototypes for application<br />

software development and to perform<br />

precise architecture performance analysis. Their<br />

ability to run real software applications at<br />

near real-time speeds before hardware availability<br />

reduces time-to-market.<br />

News ID 443<br />

■ The MathWorks: Simul<strong>in</strong>k <strong>Control</strong> Design<br />

with improved PID tun<strong>in</strong>g features<br />

The MathWorks announces the availability of<br />

Simul<strong>in</strong>k <strong>Control</strong> Design 3.0, equipped with<br />

new features that automate the process of tun<strong>in</strong>g<br />

proportional-<strong>in</strong>tegral-derivative controllers.<br />

These features are be<strong>in</strong>g released along with<br />

new PID <strong>Control</strong>ler blocks <strong>in</strong> Simul<strong>in</strong>k.<br />

News ID 493<br />

■ W<strong>in</strong>d River adds CGL 4.0 <strong>com</strong>pliance<br />

for MIPS architectures<br />

W<strong>in</strong>d River announces that W<strong>in</strong>d River L<strong>in</strong>ux<br />

3.0 for MIPS architectures <strong>com</strong>plies with the<br />

Carrier Grade L<strong>in</strong>ux (CGL) 4.0 specification<br />

November 2009 16<br />

nal teams across multiple discipl<strong>in</strong>es and multiple<br />

global sites along with third party developers,<br />