Digital Systems Laboratory - Eskişehir Osmangazi Üniversitesi

Digital Systems Laboratory - Eskişehir Osmangazi Üniversitesi

Digital Systems Laboratory - Eskişehir Osmangazi Üniversitesi

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

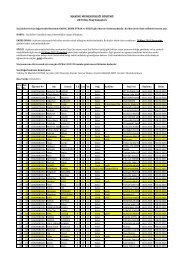

In the lab use two 7476 ICs to implement 4-bit asynchronous counter as shown in Figure 3. Connect Qoutputs of flip-flops to logic indicator lamps/LEDs of the CADET. Connect all clear (CLR) and preset(PRE) inputs to logic 1. Connect the CP input to the pulse output of the CADET and check the counter forproper operation.Write down the count sequence in Table 16. Identify this count sequence (up or down). Comment on whathappens after the application of 15 pulses to CP input.Table 16 Count sequence for the 4-bit ripple counter.34