Digital Systems Laboratory - Eskişehir Osmangazi Üniversitesi

Digital Systems Laboratory - Eskişehir Osmangazi Üniversitesi

Digital Systems Laboratory - Eskişehir Osmangazi Üniversitesi

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

<strong>Eskişehir</strong> <strong>Osmangazi</strong> University<strong>Digital</strong> <strong>Systems</strong> <strong>Laboratory</strong>Rev 3.01February 2011

LIST OF EXPERIMENTS1. BINARY AND DECIMAL NUMBERS2. DIGITAL LOGIC GATES3. INTRODUCTION TO LOGICWORKS4. BOOLEAN ALGEBRA5. CODE CONVERSION6. ADDERS/SUBTRACTORS7. MULTIPLEXERS8. FLIP-FLOPS9. COUNTERS AND SEQUENTIAL LOGIC10. LOGIC DESIGN USING VERILOG HDL AND XILINX ISE11. COMBINATIONAL LOGIC DESIGN WITH GATE LEVEL MODELING IN HDL12. CENTRAL PROCESSING UNITThere are no laboratory classes for the experiments 2, 3, 4 and 12.ExperimentDate1 28 February-4 March 20115 7-11 March 20116 14-18 March 20117 28 March-1 April 20118 4-8 April 20119 11-15 April 201110 18-22 April 201111 25-29 April 20112

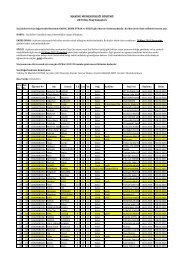

<strong>Digital</strong> <strong>Systems</strong> <strong>Laboratory</strong> 2011LIST OF THE ITEMS REQUIRED FOR THE LAB.1. Breadboard2. Integrated CircuitsIC Number Description Experiment # Quantity7400 Quadruple 2-input NAND gates 5,6,8,9 27402 Quadruple 2-input NOR gates 07404 Hex Inverter 5,6,7,9 17408 Quadruple 2-input AND gates 6,9 17410 Triple 3-input NAND gate 4 5 17420 Dual 4-input NAND gates 4 5,6 17432 Quadruple 2-input OR gates 07447 BCD-to-seven segment decoder 5,7 17476 Dual JK master-slave flip-flop 8,9 27483 4-bit binary adder 6 17485 4-bit magnitude comparator 6 17486 Quadruple 2-input XOR gates 5,6 17493 4-bit ripple counter 1 174151 8x1 multiplexer 7 174153 Dual 4x1 multiplexer 2 7 2DisplaySeven-segment LED display,common anode5,7 13

<strong>Digital</strong> <strong>Systems</strong> <strong>Laboratory</strong> 2011LABORATORY REGULATIONS AND SAFETY RULESThe following Regulations and Safety Rules must be observed in all concerned laboratory location.1. It is the duty of all concerned who use any electrical laboratory to take all reasonable steps tosafeguard the HEALTH and SAFETY of themselves and all other users and visitors.2. Be sure that all equipment is properly working before using them for laboratory exercises. Any defectiveequipment must be reported immediately to the Lab. Instructors or Lab. Technical Staff.3. Students are allowed to use only the equipment provided in the experiment manual.4. Power supply terminals connected to any circuit are only energized with the presence of the Instructoror Lab. Staff.5. Avoid any part of your body to be connected to the energized circuit and ground.6. Switch off the equipment and disconnect the power supplies from the circuit before leaving thelaboratory.7. Observe cleanliness and proper laboratory house keeping of the equipment and other relatedaccessories.8. Make sure that the last connection to be made in your circuit is the power supply and first thing to bedisconnected is also the power supply.9. Equipment should not be removed, transferred to any location without permission from the laboratorystaff.10. Students are not allowed to use any equipment without proper orientation and actual hands onequipment operation.11. Smoking and drinking in the laboratory are not permitted.All these rules and regulations are necessary precaution in Electronic <strong>Laboratory</strong> to safeguard thestudents, laboratory staff, the equipment and other laboratory users.4

<strong>Digital</strong> gates in IC packages with identification numbers and pin assignments5

IC Type 7493 Ripple Counter6

<strong>Digital</strong> <strong>Systems</strong> <strong>Laboratory</strong> 2011Lab 1: Binary and Decimal NumbersObjectiveTo demonstrate the count sequence of binary number and the binary-coded decimal (BCD)representation.Apparatus7493 4-bit ripple counterCADET trainerDual-trace OscilloscopeProcedureBinary Count1. Turn off the power switch.2. Connect the IC type 7493 as shown in Fig. 1.3. Turn the power on and observe the four logic indicators/LED. The 4-bit number in the out isincremented by one for every pulse generated by pushing the pushbutton.4. Disconnect the input of the counter at pin 14 and connect it to the Function Generator (lead TTL).5. Set frequency selector to “time 1” (1 Hz). This will provide an automatic binary count.6. Increase the frequency of the clock to 10 kHz or higher and connect its output to an oscilloscope.Observe the clock output on the oscilloscope and sketch its waveform.BCD Count1. Turn off the power switch.2. Connect the IC type 7493 as shown in Fig.2.3. Turn the power on and observe the four logic indicator lamps/LEDs. The 4-bit number in the indicatorsis incremented by one for every pulse generated by pushing the pushbutton following the sequence 0, 1,2, 3, 4, 5, 6, 7, 8, 9, 1, 2, 3, ….4. Disconnect the input of the counter and connect it to TTL output of the function generator. Setfrequency selector to “time 1” (1 Hz). This will provide an automatic binary count.Fig. 1 Binary counterFig. 2 BCD counter7

Other CountsR1 and R2 are the reset inputs of the IC type 7493. By connecting one or two outputs to the reset inputsR1 and R2, the counter can count from 0 to a variety of final count. In Figure 2, if R1 is connected to QAinstead of QB, the resulting count will be from 0000 to 1000, which is the one less than 1001 (QD=1 andQA=1).Count Binary0 00001 00012 0010….….7 01118 10009 0 10010000 Resets the counter (R1=QA, R2=QD)1 00012 0010Utilizing your knowledge of how R1 and R2 affect the final count, find out which outputs should beconnected to the resets inputs to count 0000 to the following counts:a. 0101b. 0111c. 10111. Turn of the power switch.2. Connect the 7493 IC to count from 0 to one of the final counts given above.3. Verify the count by applying pulses from the pushbuttons and observing the output count in the logicindicators/LEDs.8

<strong>Digital</strong> <strong>Systems</strong> <strong>Laboratory</strong> 2011Lab 2 : <strong>Digital</strong> Logic GatesObjectives• To study the basic logic gates: AND, OR, INVERT, NAND, and NOR.• To study the representation of these functions by truth tables, logic diagrams and Booleanalgebra.• To observe the pulse response of logic gates.• To measure the propagation delay of logic gates.Apparatus7400 Quadruple 2-input NAND gates7402 Quadruple 2-input NOR gates7404 Hex Inverters (x2)7408 Quadruple 2-input AND gates7432 Quadruple 2-input OR gates7486 Quadruple 2-input XOR gateCADET trainerDual-trace oscilloscopeTheoryANDORINVERTNANDA multi-input circuit in which the output is 1 only if all inputs are 1.The symbolicrepresentation of the AND gate is shown in Fig. 3a.A multi-input circuit in which the output is 1 when any input is 1. The symbolicrepresentation of the OR gate is shown in Fig. 3b.The output is 0 when the input is 1, and the output is 1 when the input is 0. The symbolicrepresentation of an inverter is shown in Fig. 3c.AND followed by INVERT. The symbolic representation of the NAND gate is shown in Fig3d.NOR OR followed by INVERT as shown in Fig. 3e.EX-ORTruth TableThe output of the Exclusive –OR gate, is 0 when it’s two inputs are the same and it’soutput is 1 when its two inputs are different, Fig. 3f.Representation of the output logic levels of a logic circuit for every possible combinationof levels of the inputs. This is best done by means of a systematic tabulation.a. Two input AND gate b. Two input OR gate c. Inverter9

d. Two input NAND gate e. Two input XOR gate f. Two input NOR gatePart 1: Logic FunctionsI. AND, OR, NAND, and NOR gates.Fig. 3 Symbols for digital logic gates1. Use one gate for each IC 7400 (NAND), 7402 (NOR), 7408 (AND), 7432 (OR), 7486 (XOR). Each hasinput pins, 1 and 2, and output pin 3.2. Connect pin 1 to switch S1-1, pin 2 to switch S1-2, and pin 3 to LED-1 for every gate as shown in Fig. 4as an example for the NAND gate.Fig. 4 Two input NAND gate3. Using logic switches S1-1 and S-2, apply the logic levels 0 and 1 to gate inputs (pin 1, pin 2), in thesequence shown in table 1. Record the output logic levels (see LED-1) in Table 1. Repeat the recordingsfor each gate. Remember: LED ON = Logic 1, (High) LED OFF = Logic 0 (Low)Table 1Pin 1 Pin 2 Pin 34. Use an inverter gate from IC 7404 whose input pin is pin 1 and whose output pin is pin 2.Fig. 5 Inverter gate5. Using logic switches S1-1, apply the logic levels 0 and 1 in the sequence shown in Table 2. Record theoutput logic levels in Table 2.Table 2Pin 1 Pin 2011010

Part-2: Response of Logic Gates:Connect the circuits of Fig. 6 and 7 and write the corresponding truth tables 3 and 4, respectively.Fig. 6 Fig. 7Table 3 Table 4A B C D E0 00 11 0A B C D0 00 11 0Part 3: Propagation Delay in Logic Gates:Connect all inverters inside two 7404 ICs in cascade. The output will be the same as the input except thatit will be delayed by the time it takes the signal to propagate through all six inverters. Set S2 to 100 kHzand apply clock pulses to the input of the first inverter (connect pin 1 to j14) record the wave forms anddetermine the time delay from the input to the sixth inverter. This is done with a dual trace oscilloscope byapplying the input clock pulses to one of the channels and the output of the sixth inverter to the secondchannel and measuring the delay between the two signals as shown in Fig 8. By using measured delaybetween two signals calculate the propagation delay for each inverter gate.Fig. 8 Propagation delay11

Part 4: Review Questions:1. Write a truth table for each circuit. Derive Boolean expressions for all outputs.2. A burglar alarm for a car has a normally low switch on each of four doors. If any door is opened theoutput of that switch goes HIGH. The alarm is set off with an active-LOW output signal. What type of gatewill provide this logic? Support your answer with an explanation.12

<strong>Digital</strong> <strong>Systems</strong> <strong>Laboratory</strong> 2011Lab 3 : Introduction to LogicWorksLogicWorks Tutorial is available at the web page.13

<strong>Digital</strong> <strong>Systems</strong> <strong>Laboratory</strong> 2011Lab 4 : Boolean AlgebraObjectives• To verify the rules and regulations of Boolean Algebra• To simplify and modify Boolean logic functions by means of Demorgan’s theorem.• To design and implement a logic circuit.Apparatus7400 Quadruple 2 input NAND gates.7402 Quadruple 2 input NOR gates7408 Quadruple 2 input AND gates7432 Quadruple 2 input OR gates7404 Hex inverters7411 Triple 3-input AND gateCADETLogicWorks or Proteus can be used in the digital circuit simulations.Theory (See chapter 2 of the textbook)1. A+0 = A2. A+1 = 13. A .0 = 04. A .1 = A5. A+A = A6. A+A’ = 17. A.A = A8. A.A’ = 09. (A’)’ = A10. A+AB = A11. A+A’B = A+B12. (A+B)(A+C) = A+BC13. A’. B’ = (A+B)’14. A’+B’ = (A.B)’Procedure 1a. Prove rule 1 using LogicWorks. The procedure is:I. Open a new design windowII. Choose “ALL LIBRARY” in the Parts PaletteIII. Put “OR” in the Filter windowIV. Select and double click on OR-2V. Move to the cursor back into the circuit window. The cursor on the screen will now be replaced by amoving image of an OR gate.VI. Position the OR gate near the center of the circuit window and click the mouse button.VII. Press the spacebar to return to point mode.VIII. Move again to the Parts Palette and type on the Filter “switch” or part of the word switch e.g. “sw”.IX. Select Binary switch and connect it to an input of the OR gate in the design window. (If you want tomove the binary switch around, press the shift key while moving it).X. Move again to the Parts Palette and select ground to be connected to the other input of the ORgate.14

XI. Using the same method get a Binary Probe and connect it to the output of the OR gateXII. Click on the binary switch to change it between 0 and 1 and notice how the rule A+0 = A issatisfied.In the lab connect the circuit as shown in the figure using the switch S1-1 and LED-1 to verify the rule.Fig.9 Verifying Rule 1b. Connect the circuit of Fig.10 in LogicWorks. Which rule does this circuit illustrate?Fig.10In the lab connect the circuit as shown in the figure using the switch S1-1 and LED-1 to verify the rule.c. Design a circuit that illustrates rule 10. Use clock generator of the CADET for A and one of the logicswitches of S1 for B. Copy the circuit from LogicWorks and paste it in your lab report.d. Rule 6 illustrates that A+A’ could be replaced with a wire to Vcc. What does rule 8 illustrate?e. Rule 11 states that A+A’B = A+B. Using LogicWorks design a circuit that illustrates each of theseexpressions.A+A’BA+BProve that these two circuits perform equivalent logic. (Connect two circuits and show that their outputsare the same).Procedure 2: Demorgan’s TheoremProof of equation (1)Using LogicWorks construct the two circuits given in Fig. 11 and 12 corresponding to the functions A’.B’and (A+B)’ respectively. Show that for all combinations of A and B, the two circuits give identical results.15

Fig.11Fig.12Proof of equation (2)Using LogicWorks construct two circuits given in Figs. 13 and 14, corresponding to the functions A’+B’and (A.B)’ A.B, respectively. Show that, for all combinations of A and B, the two circuits give identicalresults. In the lab connect these circuits and verify their operations.II. Design of a <strong>Digital</strong> CircuitConsider the following problem:Fig. 13 Fig. 14Four chairs A, B, C, and D are placed in a row. Each chair may be occupied (“1”) or empty (“0”). ABoolean function F is “1” if and only if there are two or more adjacent chairs that are empty.1. Give the truth table defining the Boolean function F2. Express F as a minterm expansion (standard sum of product)3. Express F as a maxterm expansion (standard product of sum)4. Using postulates and theorems of Boolean algebra, simplify the minterm expansion of F to a form withas few occurrences of each as possible.5. Implement the simplified Boolean function with logic gates on LogicWorks and check the operation ofthe circuit.Notes:- In LogicWorks use Binary Switches to represent the four chairs and connect the output of the circuit to aBinary Probe. Check that the Probe is “1” if and only if there are two or more adjacent chairs that areempty.- For the hardware circuit in the lab, use logic switches S1-1, S1-2, S1-3, and S1-4 to represent the chairsand connect the output of the circuit to LED-116

<strong>Digital</strong> <strong>Systems</strong> <strong>Laboratory</strong> 2011Lab 5 : Code ConversionObjectives• Design and build gray code to binary converter.• Design and build BCD-to-7 segment converter.ApparatusSeven segment display, common anode (CA).7400 quad 2-input NAND gates7410 triple 3-input NAND gates7420 dual 4-input NAND gates7404 HEX inverter7486 EX-OR gate7447 BCD-to-seven segment decoder.LogicWorks or Proteus can be used in the digital circuit simulations.TheoryThe conversion from one code to another is common in digital systems. Sometimes the output of asystem is used as the input to the other system. A conversion circuit is necessary between two systems ifeach system uses different codes for the same information. In this experiment you will design andconstruct 3-combinational circuit converters.PreLab Questions1. Gray code to Binary converterDesign a combinational circuit with 4 inputs and 4 outputs that converts a four-bit gray code number(Table 2) into an equivalent four-bit Binary number. Use Karnaugh map technique for simplification.2. BCD-to-seven Segment converterDesign a combinational circuit which would simulate the BCD-to-seven Segment decoder function for onlythe segment “a”, of the display. This can be done in the following steps:a. Write down the truth table with 4 inputs and 7 outputs (Table 5)Table 5Dec. BCD OutputsA B C D A b c d e f g0 0 0 0 01 0 0 0 12 0 0 0 03 0 0 1 14 0 1 0 05 0 1 0 16 0 1 1 07 0 1 1 18 1 0 0 09 1 0 0 117

. For only the output “a”, obtain a minimum logic function. Realize this function using NAND gates andinverters only. For example if decimal 9 is to be displayed a, b, c, d, f, g must be 0 and the others must be1 (For common anode type display units), if decimal 5 is to be displayed then a, f, g, c, d must be 0 andthe others must be 1.Procedure:1. Gray code to Binary converter:Gray code is one of the codes used in digital systems. It has the advantage over binary numbers that onlyone bit in the code word changes when going from one number to the next. (See Table 2). Construct thecircuit (PreLab Q.1) and verify its operations.Table 6Fig. 15 XOR chip 7486Decimal Gray Binary0 0000 00001 0001 00012 0011 00103 0010 00114 0110 01005 0111 01016 0101 01107 0100 01118 1100 10009 1101 100110 1111 101011 1110 101112 1010 110013 1011 110114 1001 111015 1000 1111.2. BCD-to-seven Segment converter:A light emitting Diode (LED) is a PN junction diode. When the diode is forward biased, a current flowsthrough the junction and the light is emitted. See Fig.16.Fig. 16A seven segment LED display contains 7 LEDs. Each LED is called a segment and they are identified as(a, b, c, d, e, f, g) segments Fig.17.18

Fig. 17 Decimal digits represented by the 7 segmentsThe display has 7 inputs each connected to an LED segment. All anodes of LEDs are tied together andjoined to 5 volts (this type is called common anode type). A current limiting resistance network must beused at the inputs to protect the 7-segment from overloading. BCD inputs are converted into 7 segmentinputs (a, b, c, d, e, f, g) by using a decoder, as shown in Fig.18.Fig. 18A decoder is a combinational circuit that converts binary information from n input lines to a maximum of 2n output lines. The input to the decoder is a BCD code and the outputs of the systems are the sevensegments a, b, c, d, e, f, and g. For further information and pin connections, consult the specificationsheet for decoder and 7-segment units.The 7447 BCD-to-seven segment decoder is used to drive a seven-segment LED display. The outputs, a-g, drive the corresponding segments on the seven-segment display according to the binary numberpresent at the inputs A-D, D being the most significant bit of the number. Three additional inputs, LAMPTEST, BI/RBO, and RBI are provided. The blanking input/ripple-blanking output (BI/RBO) blanks (turnsoff) the display when set LOW. Otherwise, when BI/RBO is set high, the outputs drive the displayaccording to the inputs A-D. The ripple blanking input (RBI) must be HIGH if blanking of a decimal zero isnot desired. This input is useful in blanking higher order zeroes when using several displays for a multidigitdecimal number. Finally, LAMP TEST selects (turns on) all the segments when set LOW. It is used totest the segments on the display.a. Construct the combinational circuit (PreLab Q.2) which will simulate the decoder function for only thesegment “a”, of the display.b. Connect the output “a” of your circuit to appropriate input of 7-segment display unit through a currentlimiting resistor, 330/470 Ω. By applying BCD codes verify the displayed decimal digits for thatsegment for “a” of the display.c. Replace your circuit by a decoder IC 7447 for all of the seven segments. Use current limiting resistorsat the inputs of the seven-segment display. Observe the display and record the segments that willlight up for invalid inputs sequence.d. Comment on the design if you don’t want to see any digit for invalid input sequence.19

BCD-to-Seven Segment Decoder and 7-segment display20

<strong>Digital</strong> <strong>Systems</strong> <strong>Laboratory</strong> 2011Lab 6 : Adders/SubtractorsObjectives• To construct and test various adders and subtractor circuits.• To construct and test a magnitude comparator circuit.Apparatus7486 quad 2-input XOR gates7400 quad 2-input NAND gates7404 Hex inverter7408 Quadruple 2 input AND gates7420 dual 4-input NAND gates7483 4-bit binary adder7485 4-bit magnitude comparator.LogicWorks or Proteus can be used in the digital circuit simulations.AdditionIC type 7483 is a 4-bit binary adder with fast carry. The pin assignment is shown in Fig 19. The two 4-bitinput binary numbers are A1 through A4 and B1 through B4. The 4-bit sum is obtained from S1 throughS4. Ci is the input carry and Co is the out carry. This IC can be used as an adder-subtractor as amagnitude comparator.Fig. 19 IC type 7483 4-bit adder.21

SubtractionThe subtraction of two binary numbers can be done by taking the 2’s complement of the subtrahend andadding it to the minuend. The 2’s complement can be obtained by taking the 1’s complement and adding1. To perform A - B, we complement the four bits of B, add them to the four bits of A, and add 1 to theinput carry. This is done as shown in Fig 2. Four XOR gates complement the bits of B when the modeselect M = 1 (because x .1=x’) and leave the bits of B unchanged when M = 0 (because x .0=x) thus,when the mode select M is equal to 1, the input carry Ci is equal to 1 and the sum output is A plus the 2’scomplement of B. When M is equal to 0, the input carry is equal to 0 and the sum generates A + B.Magnitude comparisonThe comparison of two numbers is an operation that determines whether one number is greater than,equal to, or less than the other number.Fig. 20 4-bit adder/subtractorThe IC 7485 is a 4 bit magnitude comparator. It compares two 4-Bit binary numbers (labeled as A and B)generates an output of 1 at one of three outputs labeled A > B, A < B, A = B. Three inputs are available forcascading comparators. See Fig.21.PreLab Questions:1. a. Design using LogicWorks a half adder circuit using only XOR gates and NAND gates. Then duringthe Lab construct the circuit and verify its operation.b. Design using LogicWorks a full adder circuit using only XOR gates and NAND gates. Then duringthe Lab construct the circuit and verify its operation.2. A magnitude comparator can be constructed by using a subtractor as in Fig 20. and an additionalcombinational circuit. This is done with a combinational circuit which has 5 inputs S1, S2, S3, S4, and Co,and three outputs X, Y, Z see Fig.22.X = 1 if A = B where S = 0000Y = 1 if A < B where Co = 0Z = 1 if A > B where Co = 1 S ≠ 0000.22

Design this logic circuit with minimum number of gates.Procedure:a. Construct the circuit of PreLab 1(a) and verify its operation.b. Construct the circuit of PreLab 1(b) and verify its operation.c. Use IC 7483 to add the two 4-bit numbers A and B shown in Table 7.Table 7A3 A2 A1 A0 B3 B2 B1 B0 Sum CarryOut1 0 0 1 0 0 1 00 1 1 0 1 0 1 11 1 0 0 1 0 1 0Input carry Ci is taken as logic 0. Show that if the input carry is 1, it adds 1 to the output sum. In the Labuse the logic switches S1-1 to S1-8 for the two numbers and use the SPDT (Single-Pole Double Throw)switch S1 for the input carry Ci. For sum and carry out, use LED-1 to LED-5.d. Connect the adder-subtractor circuit as shown in Fig 20. Perform the following operations and recordthe values of the output sum and the output carry Co.Table 8DecimalA B9 + 59 - 59 + 1310 + 66 - 109 - 9SumCarry OutC0• Show that Co =1 when sum exceeds 15.• Comment on sum and Co for the subtraction operations when A > B and A < B.e. Use IC7485 to compare the following two 4 bit numbers A and B. Record the outputs in Table 9.Table 9A B Outputs1001 01101100 11100011 01010101 010123

Fig. 21 7485 4-bit magnitude comparator.f. Construct the magnitude comparator of Fig. 22. The design of the logic circuit is described in PreLabQ2. Check the comparator action using part (e).Fig. 22 A magnitude comparator using a subtractor.24

<strong>Digital</strong> <strong>Systems</strong> <strong>Laboratory</strong> 2011Lab 7 : Design with MultiplexersObjectives• To design a combinational circuit and implement it with multiplexers.• To use a demultiplexer to implement a multiple output combinational circuit from the same inputvariables.Apparatus7404 HEX inverter74151 8x1 multiplexer74153 dual 4x1 multiplexer (x2)7447 BCD-to-Seven-Segment decoderSeven-Segment DisplayLogicWorks or Proteus can be used in the digital circuit simulations.PreLab Questions:Design the circuits described in Part 1 and Part 2.IC Description:74151 is a 8 line-to-1 line multiplexer. It has the schematic representation shown in Fig 23. Selection linesS2, S1 and S0 select the particular input to be multiplexed and applied to the output. Strobe S acts as anenable signal. If strobe =1, the chip 74151 is disabled and output y = 0. If strobe = 0 then the chip 74151is enabled and functions as a multiplexer. Table 10 shows the multiplex function of 74151 in terms ofselect lines.Table 10Strobe Select OutputLinesS S2 S1 S0 Y1 X X X 00 0 0 0 D00 0 0 1 D10 0 1 0 D20 0 1 1 D30 1 0 0 D40 1 0 1 D50 1 1 0 D60 1 1 1 D7Fig. 23 IC type 74151 Multiplexer 8 ×174153 is a dual 4 line-to-1 line multiplexer. It has the schematic representation shown in Fig 24. Selectionlines S1 and S0 select the particular input to be multiplexed and applied to the output IY{1 = 1, 2}.25

Each of the strobe signals IG {I = 1, 2} acts as an enable signal for the corresponding multiplexer.Table 11 shows the multiplex function of 74153 in terms of select lines. Note that each of the on-chipmultiplexers act independently from the other, while sharing the same select lines S1 and S0.Multiplexer 1Strobe Select lines Output1G S1 S0 1Y1 X X 00 0 0 1D00 0 1 1D10 1 0 1D20 1 1 1D3Table 11Multiplexer 2Strobe Select lines Output2G S1 S0 2Y1 X X 00 0 0 2D00 0 1 2D10 1 0 2D20 1 1 2D3Fig. 24 Chip 74153IC 7447 is a BCD to seven segment decoder driver. It is used to convert the combinational circuit outputsin BCD forms into 7 segment digits for the 7 segment LED display units. See Lab. 5.Procedure:Part I: Parity Generator:a. Design a parity generator by using a 74151 multiplexer. Parity is an extra bit attached to a code tocheck that the code has been received correctly. Odd parity bit means that the number of 1’s in the codeincluding the parity bit is an odd number. Fill the output column of the truth table in Table 12 for a 5-bitcode in which four of the bits (A, B, C, D) represents the information to be sent and fifth bit (x), representsthe parity bit. The required parity is an odd parity. The inputs B, C and D correspond to the select inputs of74151. Complete the truth table in Table 12 by filling in the last column with 0, 1, A or A’.b. Simulate the circuit using LogicWorks, use 74-151 multiplexer and Binary switches for inputs andbinary Probes for outputs. The 74151 has one output for Y and another inverted output W. Use A and A’for providing values for inputs 0-7. The internal values “A, B, C” are used for selection inputs B, C, and D.Simulate the circuit and test each input combination filling in the table shown below.26

Table 12Inputs Outputs Connect data toA B C D X0 0 0 00 0 0 10 0 1 00 0 1 10 1 0 00 1 0 10 1 1 00 1 1 11 0 0 01 0 0 11 0 1 01 0 1 11 1 0 01 1 0 11 1 1 01 1 1 1In the Lab connect the circuit and verify the operations. Connect an LED to the multiplexer output so that itrepresents the parity bit which lights any time when the four bits input have even parity.Part 2: Vote Counter:A committee is composed of a chairman (C), a senior member (S), and a member (M). The rules of thecommittee state that:• The vote of the member (M) will be counted as 2 votes• The vote of the senior member will be counted as 3 votes.• The vote of the chairman will be counted as 5 votes.Each of these persons has a switch to close (“l”) when voting yes and to open (“0”) when voting no. It isnecessary to design a circuit that displays the total number of votes for each issue. Use a seven segmentdisplay and a decoder to display the required number. If all members vote no for an issue the displayshould be blank. (Recall from Experiment #4, that a binary input 15 into the 7447 blanks all sevensegments). If all members vote yes for an issue, the display should be 0. Otherwise the display shows adecimal number equal to the number of 'yes' votes. Use two 74153 units, which include four multiplexersto design the combinational circuit that converts the inputs from the members’ switch to the BCD digit forthe 7447.In LogicWorks use +5V for Logic 1 and ground for Logic 0 and use switches for C, S, and M. Use twochips 74153 and one decoder 7446 verify your design and get a copy of your circuit with the pin numbersto Lab so that you could connect the hardware in exactly the same way.27

<strong>Digital</strong> <strong>Systems</strong> <strong>Laboratory</strong> 2011Lab 8 : Flip-FlopsObjectives:• To become familiar with flip-flops.• To implement and observe the operation of different flip-flops.Apparatus7400 quad 2-input NAND gates (2)7476 dual JK master-slave flip-flops.LogicWorks or Proteus can be used in the digital circuit simulations.Procedure1. In the pre-lab using LogicWorks construct the circuit shown in Fig.25.Fig. 25You can use generic NAND gates or 74-00 and Binary Probes to simulate LEDs. Finally, we use SPDT forthe bouncing switch. Using the simulated circuit fill in the truth table.28

S R Q Q’1 01 10 11 10 0In the lab, build the RS latch shown in Fig.26. Use SPDT switch S as a bouncing switch. Q and Q’ outputsare connected to LED’s of the CADET. Verify the truth table of SR latch experimentally.Fig. 262. Modify the basic RS latch into a D latch by adding the steering gates and the inverter shown in Fig.27Connect the D input to the pulse generator of the CADET and set it at 1 Hz. Connect the enable input to ahigh through 1k resistor. Observe the output; obtain the truth table experimentally then change the enableto a low.Is the enable an active high or an active? Leave the enable low and place a momentary short to groundfirst on one output and then on the other. What happens?Fig. 273. The 7476 is a dual JK master-slave flip-flops with preset and clear inputs. The function table given inTable 13 defines the operation of the flip-flop. The positive transition of the CLOCK (CP) pulse changesthe master flip-flop, and the negative transition changes the slave flip-flop as well as the output of thecircuit.29

Table 13Fig. 28In the lab, construct the circuit of Fig 28. Look at the data sheet for the 7476 and determine the inactivelogic required at the PRE and CLR inputs.Connect the 7476 for the SET mode by connecting J = 1, K = 0. With CLOCK (CP) = 0; test the effect ofPRE, CLR by putting a 0 on each, one at a time.Put CLR = 0, then pulse the clock (CP) by putting a HIGH then a LOW, on the clock. Does the CLR inputoverride J input?Verify the operation of the JK flip flop by experimentally obtaining the characteristic.30

<strong>Digital</strong> <strong>Systems</strong> <strong>Laboratory</strong> 2011Lab 9 : Clocked Sequential Circuits and CountersObjectives• To design, build and test synchronous sequential circuits• To design, build, and test synchronous counters• To design, build and test asynchronous countersApparatus7476 dual JK master-slave flip-flops (x2)7400 quad 2-input NAND gates7404 HEX inverter7408 quad 2-input AND gateLogicWorks or Proteus can be used in the digital circuit simulations.Pre-Lab Questions1. a. Design, construct and test a sequential circuit whose state is shown in Fig.29. Use JK flip-flops in thedesign.Fig. 29.The circuit has two flip-flops A, B, one input x and one output y. The circuit is to be designed by treatingthe unused states as don’t care conditions. The final circuit must be analyzed to ensure that it is selfcorrecting.If not suggest a solution.31

. Complete the excitation table shown in Table 14.Table 14c. Using Karnaugh maps obtain minimal expressions for the flip-flop input functions JA, KA,JB and KB.d. Simulate the circuit using LogicWorks. LogicWorks does not have the JK master-slave flip-flop IC 7476.Use instead the generic JK flip-flop as you did in Lab 8. In the Lab, build the circuit and check the outputto verify the state table values.2. a. In the pre-lab using LogicWorks and then in the lab using hardware ICs, design a 2-bit gray codecounter using JK flip-flops. The required sequence is the binary equivalent of (0-1-3-2-0). A state diagramfor this counter is given in Fig. 30.Fig. 30b. Complete the excitation table in Table 15 for the counter and obtain logic expression for the JK flip-flopinput functions.32

Table 15Procedure:1. Synchronous Sequential CircuitsBuild the sequential circuit that is designed in Pre-Lab Q1, and test the circuit by applying pulse from theCADET. Check that the output is the designed sequence.2. Synchronous CountersSynchronous counters have all clock lines tied to a common clock causing all flip-flops to change at thesame time. The count sequence of a counter can be analyzed by placing the counter into every possiblenumber in the sequence and determining the next number in the sequence state diagram is developed asthe analysis proceeds. (A state diagram is an illustration of the transitions that occur after each clockpulse).In the lab, build the 2-bit gray code counter circuit and test it by pulsing it from the CADET. Check that theoutput is the designed sequence.3. A Synchronous CountersAsynchronous counters are a series of flip-flops each clocked by the previous state, one after the other.Since all the stages of the counter are not clocked together, a ripple effect propagates as various flip-flopsare clocked. For this reason they are called ripple counters. The modulus of a counter is the number ofdifferent output states the counter may take (i.e. Mod 4 means the counter has four output states).In the pre-lab using LogicWorks construct a 4-bit asynchronous counter shown in Fig.31. (It is also calledbinary ripple counter). Use four generic JK flip-flops. Connect four Binary Probes to Q outputs. Connect allR and S inputs to Logic 1 and connect a switch to the CP input.Fig. 31. 4-bit ripple counter.33

In the lab use two 7476 ICs to implement 4-bit asynchronous counter as shown in Figure 3. Connect Qoutputs of flip-flops to logic indicator lamps/LEDs of the CADET. Connect all clear (CLR) and preset(PRE) inputs to logic 1. Connect the CP input to the pulse output of the CADET and check the counter forproper operation.Write down the count sequence in Table 16. Identify this count sequence (up or down). Comment on whathappens after the application of 15 pulses to CP input.Table 16 Count sequence for the 4-bit ripple counter.34

<strong>Digital</strong> <strong>Systems</strong> <strong>Laboratory</strong> 2011Lab 10 : Logic Design Using Verilog HDL and Xilinx ISE<strong>Laboratory</strong> Assignment #1ObjectivesThis lab is an introduction to logic design using Verilog-HDL with the Xilinx ISE 10.1i tools. No new logicdesign concepts are presented in this lab. The goals of this lab are for you to become familiar with theXilinx’s ISE Project Navigator tool for Verilog-HDL.Procedure:You will learn how to enter Verilog description of two inputs XOR gate and test your HDL definition inXilinx ISE. You should do everything described below. In the lab, you are not going to implement thedesign in a programmable logic device, therefore the lab ends after testing the circuit using ModelSim.Project Navigator OverviewThe Project Navigator is divided into four main sub-windows, as seen in Figure 32. On the top left is theSources in Project window which hierarchically displays the elements included in the project. Beneath theSources in Project window is the Processes for Current Source window which displays availableprocesses for the currently selected source. The third window at the bottom of the Project Navigator is theConsole window which displays status messages, errors, and warnings, and which is updated during allproject actions. The fourth window to the right is for viewing and editing text files. Each window may be1 resized, undocked from Project Navigator or moved to a new location within the main Project Navigatorwindow. The default layout can always be restored by selecting View Restore Default Layout.1 The experiments 10 is adopted from San Jose State University Department of Electrical Engineering, EE178 and isupdated with Xilinx ISE release 10.1i.35

Figure 32: Typical Project Navigator WindowThe Sources in Project window consists of three tabs which provide information for the user. Each tab isdiscussed in further detail below:• The Module View tab displays the project name, any user documents, the specified part typeand design flow/synthesis tool, and design source files. Each file in the Module View has anassociated icon. The icon indicates the file type (Verilog-HDL file or text file, for example). For acomplete list of possible source types and their associated icons, see the Project Navigator onlinehelp. Select Help ISE Help Contents, select the Index tab and click Source / File types. If a filecontains lower levels of hierarchy, the icon has a + to the left of the name. Verilog-HDL files havethis + to show the modules within the file. You can expand the hierarchy by clicking the +. You canopen a file for editing by double-clicking on the filename.• The Snapshot View tab displays all snapshots associated with the project currently open inProject Navigator. A snapshot is a copy of the project including all files in the working directory,and synthesis and simulation subdirectories. A snapshot is stored with the project for which it wastaken, and can be viewed in the Snapshot View. You can view the reports, user documents, andsource files for all snapshots. All information displayed in the Snapshot View is read-only. Usingsnapshots provides an excellent version control system.36

• The Library View tab displays all libraries associated with the project open in Project Navigator.The Processes for Current Source window contains the Process View tab. The Process View tab iscontext sensitive and changes based upon the source type selected in the Sources for Project window.From the Process View tab, you can run the functions necessary to define, run and view your design. TheProcess View tab provides access to the following functions:• Design Entry Utilities: Provides access to symbol generation, instantiation templates, HDLConverter, Command Line Log Files, Launch MTI, and simulation library compilation.• User Constraints: Provides access to editing location and timing constraints.• Synthesis: Provides access to Check Syntax, Synthesize, View RTL Schematic, and synthesisreports. This varies depending on the synthesis tools you use.• Implement Design: Provides access to implementation tools and design flow reports.• Generate Programming File: Provides access to the configuration tools and bitstreamgeneration.The Processes for Current Source window incorporates automake technology. This enables the user toselect any process in the flow and the software automatically runs the processes necessary to get to thedesired step. For example, when you run the Implementation process, Project Navigator also runs thesynthesis process, if necessary, because implementation is dependent on up-to-date synthesis results.The Console window displays errors, warnings, and informational messages. Errors are signified by a redbox next to the message, while warnings have a yellow box. Warning and Error messages may also beviewed separately from other console text messages by selecting either the Warnings or Errors tab at thebottom of the console window.You can navigate from a synthesis error or warning message in the Console window to the location of theerror in a source Verilog-HDL file. To do so, select the error or warning message, right-click the mouse,and from the menu select Goto Source. The Verilog-HDL source file opens and the cursor moves to theline with the error.You can also navigate from an error or warning message in the Console window to the relevant solutionrecords on the Xilinx support website. These types of errors or warnings can be identified by the web iconto the left of the error. To navigate to the solution record, select the error or warning message, right-clickthe mouse, and from the menu select Goto Solution Record. The default web browser opens and displaysall solution records applicable to this message.In the fourth window, you can access the ISE Text Editor, the ISE Language Templates, and HDLBencher Text Editor. The ISE Text Editor enables you to edit source files and to access the ISE LanguageTemplates, which is a catalog of Verilog-HDL and User Constraint File templates. You can use and modifythese templates for your own design.Design EntryThe design used in this tutorial is a simple two-input XOR. The design will be described in Verilog-HDL.Double-click the Project Navigator icon on your desktop or select Start Programs Xilinx ISE ProjectNavigator. From Project Navigator, select File New Project. The first of the New Project dialog boxes willappear, as shown in Figure 33.37

Figure 33: New Project Dialog 1 of 5You are prompted to enter a project name, a project location, and a top level module type, as shown inFigure 33. You may change the project location to another folder if you wish. Do not use file or foldernames that contain spaces. I advise all students to purchase a USB memory stick and store their work onremovable media. Even if you are doing most of your work from home, you must have some means totransport your project to the lab if you need help debugging it. Never store your projects on the labmachines. When you are satisfied with the project name and location, click “Next”.The next dialog allows you to set additional project options. The first group of settings shown in Figure 34represents the hardware target that is available to you on the Spartan-3 Starter Kit board. The secondgroup of settings represents the design entry language, synthesis tool, and simulator preferences. Set theoptions as shown in Figure 34 and click “Next”.38

Figure 34: New Project Dialog 2 of 5The following dialog box of Figure 35 gives you the opportunity to create new source files as part of thenew project process. Do not create new source files at this time, simply click “Next” to proceed.Figure 35: New Project Dialog 3 of 5The following dialog box of Figure 36 gives you the opportunity to add existing source files as part of thenew project process. Do not add existing source files at this time, simply click “Next” to proceed.39

Figure 36: New Project Dialog 4 of 5The final dialog box in the new project process, shown in Figure 37, provides a summary of the projectthat Project Navigator will create based on your settings. Review the summary to make sure it matcheswhat is shown in Figure 37. If it does not, go “Back” and correct any errors. Otherwise, click “Finish” tocomplete this process.Figure 37: New Project Dialog 5 of 5At this point, the project has been created but it does not contain any source files. Create a new sourcefile for the two-input XOR. Either select Project New Source from the main menu or use the equivalentprocess in the Processes for Current Source window. The first of the New Source dialog boxes willappear, as shown in Figure 38.40

Figure 38: New Source Dialog 1 of 3Select Verilog Module to indicate you are creating a Verilog-HDL design module. Then, provide a filename as shown in Figure 38. You should not need to change the specified location, which should beinside the project directory you created earlier. Click “Next”.The next dialog optionally allows you to specify the ports of the module. This may also be done in the texteditor, when creating the module, so skip it at this stage. Simply confirm that the settings match thoseshown in Figure 39 and click “Next”.Figure 39: New Source Dialog 2 of 341

The final dialog box of Figure 40 provides a summary of the source that Project Navigator will createbased on your settings. Review the summary to make sure it matches what is shown in Figure 40. If itdoes not, go “Back” and correct any errors. Otherwise, click “Finish” to complete this process. The newsource file will be automatically opened in the text editor.Figure 40: New Source Dialog 3 of 3In the text editor, some of the basic file structure is already in place. Keywords are displayed in blue, datatypes in red, comments in green, and values in black. This color-coding enhances readability andrecognition of typographical errors. Now, enter the two-input XOR design. You may be able to simply copyand paste this from the lab handout, but if that doesn’t work, transcribe the contents:// File: two_input_xor.v// Date: October 2006// Name://// This is the top level design for the Lab #1 assignment.// The `timescale directive specifies what the simulation time units are (1 ns here)// and what the simulator timestep should be (1 ps here).`timescale 1 ns / 1 psmodule two_input_xor (in1, in2, out);// Declare the ports for this module. Keep in mind that all inputs are implied to be// of type wire. For inout ports (not used in this example) type wire is also implied.// The output is also implied to be of type wire, unless you add an explicit "reg out;"// statement.input in1, in2;output out;// Below is a description of what this module does. You could substitute other possible// descriptions, like those presented in the Verilog review presentation.assign out = in1 ^ in2;endmodule42

At this point, you should end up with a window that looks somewhat like that shown in Figure 41. Onceyou are satisfied, save the file and close the window. It is a good idea to get in the habit of saving yourproject. There are options on the main menu to save individual files or the complete project.Figure 41: Completed DesignFunctional SimulationFunctional simulation is done before the design is synthesized to verify that the logic you have created iscorrect. This allows a designer to find and fix any bugs in the design before spending time withsubsequent steps. Project Navigator provides an integrated flow with the Modelsim simulator that allowssimulations to be run from the Project Navigator. In order to simulate the design, a test bench is requiredto stimulate the design. Create a new source file for the test bench. Either select Project New Source fromthe main menu or use the equivalent process in the Processes for Current Source window. The first of theNew Source dialog boxes will appear, as shown in Figure 42.43

Figure 42: New Source Dialog 1 of 3Select Verilog Test Fixture to indicate you are creating a Verilog-HDL testbench module. Then, provide afile name as shown in Figure 42. You should not need to change the specified location, which should beinside the project directory you created earlier. Click “Next”. The second dialog, shown in Figure 43, asksyou to identify a design module with which the test bench should be associated. Select the two-input XORdesign as shown and click “Next”.Figure 43: New Source Dialog 2 of 3The final dialog box of Figure 44 provides a summary of the source that Project Navigator will createbased on your settings. Review the summary to make sure it matches what is shown in Figure 44. If it44

does not, go “Back” and correct any errors. Otherwise, click “Finish” to complete this process. The newsource file will be automatically opened in the text editor.Figure 44: New Source Dialog 3 of 3In the text editor, some of the basic file structure is already in place. Keywords are displayed in blue, datatypes in red, comments in green, and values in black. This color-coding enhances readability andrecognition of typographical errors. Now, enter the test bench for the two-input XOR design. You may beable to simply copy and paste this from the lab handout, but if that doesn’t work, transcribe the contents:`timescale 1ns / 1ps////////////////////////////////////////////////////////////////////////////////// Company:// Engineer://// Create Date: 12:44:29 09/24/2006// Design Name: two_input_xor// Module Name: testbench.v// Project Name: Lab1// Target Device:// Tool versions:// Description://// Verilog Test Fixture created by ISE for module: two_input_xor//// Dependencies://// Revision:// Revision 0.01 - File Created// Additional Comments://////////////////////////////////////////////////////////////////////////////////45

module testbench_v;// Outputswire sig3;// Inputsreg sig1;reg sig2;// Instantiate the Unit Under Test (UUT)two_input_xor uut (.in1(sig1),.in2(sig2),.out(sig3));reg test_passed;initial begin// Let's start off assuming we are going// to pass the tests until we find a case// that contradicts!test_passed = 1'b1;// Test Case #0sig1 = 1'b0;sig2 = 1'b0;#5;$display("At time %t, sig1 = %b, sig2 = %b, output = %b.",$time, sig1, sig2, sig3);if (sig3 != 1'b0) test_passed = 1'b0;// Test Case #1sig1 = 1'b0;sig2 = 1'b1;#5;$display("At time %t, sig1 = %b, sig2 = %b, output = %b.",$time, sig1, sig2, sig3);if (sig3 != 1'b1) test_passed = 1'b0;// Test Case #2sig1 = 1'b1;sig2 = 1'b0;#5;$display("At time %t, sig1 = %b, sig2 = %b, output = %b.",$time, sig1, sig2, sig3);if (sig3 != 1'b1) test_passed = 1'b0;// Test Case #3sig1 = 1'b1;sig2 = 1'b1;#5;$display("At time %t, sig1 = %b, sig2 = %b, output = %b.",$time, sig1, sig2, sig3);if (sig3 != 1'b0) test_passed = 1'b0;// Now, print out a message with the test// results and then finish the simulation.if (test_passed) $display("Result: PASS");else $display("Result: FAIL");$stop;end46

endmoduleAt this point, you should end up with a window that looks somewhat like that shown in Figure 45. Onceyou are satisfied, save the file and close the window. It is a good idea to get in the habit of saving yourproject. There are options on the main menu to save individual files or the complete project.Figure 45: Completed Test BenchNow that you have a test bench in your project, you can perform functional simulation on the design. Thesimulation processes enable you to run simulation on the design using Modelsim. To locate the Modelsimsimulator processes, select the test bench in the Sources in Project window. Then, click the + next to theModelsim Simulator entry in the Processes for Current Source window to expand the item, this is alsoshown in Figure 45. The following simulation processes are available:• Simulate Behavioral Model. This process will start the design simulation.• Simulate Post-Translate Verilog Model. Simulates the netlist after the NGDBuild stage.• Simulate Post-Map Verilog Model. Simulates the netlist after the Map stage.• Simulate Post-Place & Route Verilog Model. Simulates the netlist after Place & Route.At this point, you will perform a functional simulation using Simulate Behavioral Model but you mustspecify the simulation process properties first. Right click on Simulate Behavioral Model, and selectSimulation Properties. The Process Properties dialog box appears, as shown in Figure 46.47

Figure 46: Simulation Process PropertiesIf you do not have all the properties shown in Figure 46, you can make them visible by canceling thedialog box, then selecting Edit Preferences from the main menu. Select the Processes tab, set theProperty Display Level to advanced, and then return to Simulation Properties. Make sure the propertiesare set as shown in Figure 46. The most interesting of these parameters is probably the simulation runtime – 1000 ns is more than sufficient for the test bench in the project. For test benches that require moresimulation time, this property should be adjusted as needed. Click “Ok”.To start the simulation, double-click Simulate Behavioral Model. Modelsim creates a work directory,compiles the source files, loads the design, and performs simulation for the time specified. Four Modelsimwindows will appear. The first, and most important, is the main Modelsim console, shown in Figure 47.This window displays messages from the simulator. These messages include notes, warnings, and errors,plus any output created by the design being simulated. You should see text output from the test bench.48

Figure 47: Modelsim Console WindowThe second window is the structure window, shown in Figure 48. This window allows you to browse thehierarchy of the test bench and the design under test. In large hierarchical designs, it is very handy.Figure 48: Modelsim Structure WindowThe third window is the signals window, shown in Figure 49. This window shows the signals that arepresent in the portion of the design selected in the structure window.49

Figure 49: Modelsim Signals WindowThe fourth and final window is the wave window, which is used to display simulated waveforms. ProjectNavigator automatically adds all top-level signals to the wave window, as shown in Figure 50. Additionalsignals are displayed in the signal window based upon the selected structure in the structure window.Figure 50: Simulated waveformsThere are two basic methods for adding signals to the wave window. You can drag and drop them fromthe signals window, or highlight them in the signals window and then select Add Wave Selected Signals.If you use this second technique, you will see that there are additional options available. When you addnew signals to the wave window, you will notice that waveforms do not automatically appear. This isbecause Modelsim did not record the simulation data for these signals. By default, Modelsim will onlyrecord data for the signals that have been added to the waveform window before or during the simulation.Therefore, when new signals are added to the waveform window, the simulation needs to be restartedand re-run for the desired amount of time. To restart and re-run the simulation, click the “RestartSimulation” button at the top of the console window. This button is shown in Figure 51.Figure 51: Restart Simulation Button50

The Restart dialog box appears, as shown in Figure 52. Simply click “Restart”. At the Modelsim prompt,you will need to manually enter the run command. Enter “run 1000 ns” and hit enter. The simulation willrun again, just like it did the first time.Figure 52: Restart DialogThe Modelsim simulator provides the capability of saving the signals list in the wave window. This can beimportant when additional signals or stimuli are added, and the simulation is restarted. In the wavewindow, select File Save Format. After restarting a simulation, you can select File Load Format in thewave window to restore.============================ STOP HERE ======================================Design SynthesisWith a functionally correct design description in Verilog-HDL, the next step is to use a synthesis tool totransform your description into a netlist. A netlist is a machine-readable schematic. In this class, we will beusing a tool called XST, which is integrated with Project Navigator and can only target Xilinx devices.Select two_input_xor in the Sources in Project window. Then, double click on the Synthesize—XSTprocess in the Processes for Current Source window. Project Navigator will synthesize the design andprint information to the Console window in the process. As an informational note, it is possible to changethe synthesis options before you synthesize by right clicking on Synthesize—XST and then selectingProperties. For this tutorial, however, leave the options at their default settings.You should not see any errors in the Console window. However, you should always review the log file,which is available for viewing if you expand the Synthesize—XST process item by clicking on the + next toit. Select View Synthesis Report. If you don’t understand a particular message, you should not simplyignore it. Instead, search the Xilinx support web site or ask the instructor. For comparison purposes, hereis a sample log file.Release 8.1i - xst I.24Copyright (c) 1995-2005 Xilinx, Inc. All rights reserved.--> Parameter TMPDIR set to ./xst/projnav.tmpCPU : 0.00 / 0.39 s | Elapsed : 0.00 / 0.00 s--> Parameter xsthdpdir set to ./xstCPU : 0.00 / 0.39 s | Elapsed : 0.00 / 0.00 s--> Reading design: two_input_xor.prjTABLE OF CONTENTS51

1) Synthesis Options Summary2) HDL Compilation3) HDL Analysis4) HDL Synthesis4.1) HDL Synthesis Report5) Advanced HDL Synthesis5.1) Advanced HDL Synthesis Report6) Low Level Synthesis7) Final Report7.1) Device utilization summary7.2) TIMING REPORT=========================================================================* Synthesis Options Summary *=========================================================================---- Source ParametersInput File Name: "two_input_xor.prj"Input Format: mixedIgnore Synthesis Constraint File : NO---- Target ParametersOutput File NameOutput FormatTarget Device: "two_input_xor": NGC: xc3s400-5-pq208---- Source OptionsTop Module Name: two_input_xorAutomatic FSM Extraction : YESFSM Encoding Algorithm : AutoFSM Style: lutRAM Extraction: YesRAM Style: AutoROM Extraction: YesMux Style: AutoDecoder Extraction : YESPriority Encoder Extraction : YESShift Register Extraction : YESLogical Shifter Extraction : YESXOR Collapsing: YESROM Style: AutoMux Extraction: YESResource Sharing: YESMultiplier Style: autoAutomatic Register Balancing : No---- Target OptionsAdd IO Buffers: YESGlobal Maximum Fanout : 500Add Generic Clock Buffer(BUFG) : 8Register Duplication : YESSlice Packing: YESPack IO Registers into IOBs : autoEquivalent register Removal : YES---- General OptionsOptimization Goal : SpeedOptimization Effort : 152

Keep Hierarchy: NORTL Output: YesGlobal Optimization : AllClockNetsWrite Timing Constraints : NOHierarchy Separator : /Bus Delimiter : Case Specifier: maintainSlice Utilization Ratio : 100Slice Utilization Ratio Delta : 5---- Other Optionslso: two_input_xor.lsoRead Cores: YEScross_clock_analysis : NOverilog2001: YESsafe_implementation : NoOptimize Instantiated Primitives : NOuse_clock_enable: Yesuse_sync_set: Yesuse_sync_reset: Yes==================================================================================================================================================* HDL Compilation *=========================================================================Compiling verilog file "two_input_xor.v" in library workModule compiledNo errors in compilationAnalysis of file succeeded.=========================================================================* HDL Analysis *=========================================================================Analyzing top module .Module is correct for synthesis.=========================================================================* HDL Synthesis *=========================================================================Synthesizing Unit .Related source file is "two_input_xor.v".Found 1-bit xor2 for signal .Unit synthesized.=========================================================================HDL Synthesis ReportMacro Statistics# Xors : 11-bit xor2 : 1=========================================================================53

=========================================================================* Advanced HDL Synthesis *==================================================================================================================================================Advanced HDL Synthesis ReportMacro Statistics# Xors : 11-bit xor2 : 1==================================================================================================================================================* Low Level Synthesis *=========================================================================Loading device for application Rf_Device from file '3s400.nph' in environment D:\Xilinx.Optimizing unit ...Mapping all equations...Building and optimizing final netlist ...Found area constraint ratio of 100 (+ 5) on block two_input_xor, actual ratio is 0.=========================================================================* Final Report *=========================================================================Final ResultsRTL Top Level Output File Name : two_input_xor.ngrTop Level Output File Name : two_input_xorOutput Format: NGCOptimization Goal : SpeedKeep Hierarchy: NODesign Statistics# IOs : 3Cell Usage :# BELS : 1# LUT2 : 1# IO Buffers : 3# IBUF : 2# OBUF : 1=========================================================================Device utilization summary:---------------------------Selected Device : 3s400pq208-5Number of Slices: 1 out of 3584 0%Number of 4 input LUTs: 1 out of 7168 0%Number of bonded IOBs: 3 out of 141 2%=========================================================================54

TIMING REPORTNOTE: THESE TIMING NUMBERS ARE ONLY A SYNTHESIS ESTIMATE.FOR ACCURATE TIMING INFORMATION PLEASE REFER TO THE TRACE REPORTGENERATED AFTER PLACE-and-ROUTE.Clock Information:------------------No clock signals found in this designTiming Summary:---------------Speed Grade: -5Minimum period: No path foundMinimum input arrival time before clock: No path foundMaximum output required time after clock: No path foundMaximum combinational path delay: 7.760nsTiming Detail:--------------All values displayed in nanoseconds (ns)=========================================================================Timing constraint: Default path analysisTotal number of paths / destination ports: 2 / 1-------------------------------------------------------------------------Delay: 7.760ns (Levels of Logic = 3)Source: in1 (PAD)Destination: out (PAD)Data Path: in1 to outGate NetCell:in->out fanout Delay Delay Logical Name (Net Name)---------------------------------------- ------------IBUF:I->O 1 0.715 0.976 in1_IBUF (in1_IBUF)LUT2:I0->O 1 0.479 0.681 Mxor_out_Result1 (out_OBUF)OBUF:I->O 4.909 out_OBUF (out)----------------------------------------Total7.760ns (6.103ns logic, 1.657ns route)(78.6% logic, 21.4% route)=========================================================================CPU : 6.69 / 7.16 s | Elapsed : 7.00 / 7.00 s-->Total memory usage is 111004 kilobytesNumber of errors : 0 ( 0 filtered)Number of warnings : 0 ( 0 filtered)Number of infos : 0 ( 0 filtered)Reading the report is a good way to find out what types of (and how many) resources the synthesis toolused. You can also catch other problems this way. For example, if you found that this design descriptionresulted in flip flops, in addition to a look-up table and I/O buffers, you had better go back and figure outwhat went wrong. This is why you must have an understanding of the hardware you are attempting to55

create when you write your design description. At this point, you should have a green checkmark next tothe Synthesize—XST process.Design ImplementationDesign implementation is the sequence of events that translates your synthesized design netlist into aprogramming file for the FPGA device. Your design description, which you have now synthesized, has anumber of ports at the top level. The implementation tools need to know how to assign the ports in yourtop level to physical pins on the FPGA, which are connected to various resources on the Spartan-3 StarterKit board. If you do not make explicit assignments, the tools will randomly assign pins for you. However,this is generally a bad idea because random assignments will be wrong. The top-level design has twoinput ports, and a single output port. We will want to have two switches, SW0 and SW1, connected to theinputs. Additionally, we will want the output connected to an LED so that we can observe it – indicator LD0is appropriate for this purpose.If you inspect the top of the Spartan-3 Starter Kit board, you will notice that almost every resource hasbeen thoughtfully annotated with text indicating which FPGA pins are connected to it. This information isalso available in the Spartan-3 Starter Kit User Guide in tabular and schematic form. Try to identify whichFPGA pins are used for SW0, SW1, and LD0, and then check your results with what is shown below. Youwill need to be able to do this on your own in future lab assignments:• SW0 FPGA Pin F12• SW1 FPGA Pin G12• LD0 FPGA Pin K12You now have enough information to create what is called a user constraint file, or UCF. This file containsdesign constraints that you did not specify in the Verilog-HDL description, such as pin location and designperformance constraints. It is convenient to provide them in a UCF rather than in the Verilog-HDLdescription. For instance, if you make a mistake in the pin assignments, you do not need to go back andresynthesize your design.You can add a UCF to the project using the same process you used for adding the design and its testbench. Create a new source file; select Project New Source from the main menu or use the equivalentprocess in the Processes for Current Source window. The first of the New Source dialog boxes willappear, as shown in Figure 53.56

Figure 53: New Source Dialog 1 of 3Select Implementation Constraints File to indicate you are creating a constraints file. Then, provide a filename as shown in Figure 53. You should not need to change the specified location, which should beinside the project directory you created earlier. Click “Next”.The second dialog, shown in Figure 54, asks you to identify a design module with which the constraintsfile should be associated. Select the two-input XOR design as shown and click “Next”.Figure 54: New Source Dialog 2 of 357

The final dialog box of Figure 55 provides a summary of the source that Project Navigator will createbased on your settings. Review the summary to make sure it matches what is shown in Figure 55. If itdoes not, go “Back” and correct any errors. Otherwise, click “Finish” to complete this process. This time,however, you will notice that the new source file is not automatically opened in the text editor.Figure 55: New Source Dialog 3 of 3If you select the constraint file in the Sources in Project Window, and then expand the Processes forCurrent Source window item for User Constraints by clicking on the + next to it, you will see that there area number of ways to edit a user constraint file, including a text editor. The default user constraint editor iscalled PACE. Simply double click the constraint file in the Sources in Project window, and PACE will open,see Figure 56. PACE is a fairly powerful constraint editor but we will only be using a small portion of itscapabilities in this tutorial.The PACE sub-windows shown in Figure 56 have been moved from their default positions in order to yieldan improved screen capture. First click on I/O Pins in the Design Browser window. The Design Object Listwindow will then show the names of the three top level ports and their signal directions. In this window, fillin the LOC fields based on the previously determined FPGA pin assignments. For the three IO STD fieldsselect LVCMOS33, which is a common 3.3 volt signaling standard.After entering each pin assignment, you will notice that the corresponding package pin shown in thePackage Pins window will be grayed out, indicating it is in use. This diagram represents the physical pinson the package that holds the FPGA die. You will also notice the highlighting of regions shown in theDevice Architecture window. This diagram represents resources in use on the FPGA die related to yourconstraints – in this case, the input and output buffers and I/O pads. When you are done, save your workand exit the PACE program.58

Figure 56: Entering Pin Location Constraints using PACENow that you have a constraint file in your project, you can implement the design. Select two_input_xor inthe Sources in Project window. Then, double click on the Implement Design process in the Processes forCurrent Source window. Project Navigator will implement the design and print information to the Consolewindow in the process. As an informational note, it is possible to change the implementation optionsbefore you implement by right clicking on Implement Design and then selecting Properties. For thistutorial, however, leave the options at their default settings. You should not see any errors in the Consolewindow. However, you should always review the three log files, which are available for viewing if youexpand the Implement Design process item by clicking on the + next to it. There are log files locatedunder Translate, Map, and Place and Route. If you don’t understand a particular message, you should notsimply ignore it. Instead, search the Xilinx support web site or ask the instructor. At this point, you shouldhave a green checkmark next to the Implement Design process.Timing SimulationAfter completing the implementation steps, you can simulate your design again – this time, using astructural representation of your synthesized, placed, and routed design with worst-case delayinformation. The idea is to simulate your design, as physically implemented in the FPGA device. Thesimulation processes enable you to run simulation on the design using Modelsim. To locate the Modelsimsimulator processes, select the test bench in the Sources in Project window. Then, click the + next to theModelsim Simulator entry in the Processes for Source window to expand the item. You will perform atiming simulation using Simulate Post-Place & Route Verilog Model but you must specify the simulationprocess properties first, just like you did for functional simulation. Right click on Simulate Post-Place &Route Verilog Model, and select Simulation Properties. The Process Properties dialog box appears, asshown in Figure 57.59

Figure 57: Simulation Process PropertiesMake sure the properties are set as shown in Figure 57. The most interesting of these parameters isprobably the simulation run time – again, 1000 ns is more than sufficient for the test bench in the project.For test benches that require more simulation time, this property should be adjusted as needed. Click“Ok”. To start the simulation, double-click Simulate Post-Place & Route Verilog Model. Modelsim createsa work directory, compiles the source files, loads the design, and performs simulation for the timespecified. The simulator will run, and you’ll see results as before. Unless you are lucky, your simulationwill fail. The testbench should report that your design has failed because it is checking the output of yourdesign five nanoseconds after it has changed the inputs. If you look at the wave window, it appears thatthe FPGA implementation requires more than five nanoseconds for signals to propagate through thedesign – more like ten to fifteen nanoseconds. The exact number depends on the device you are using,the placement, the routing, and your design. Close Modelsim, go back to your testbench, and change thedelays to fifty nanoseconds (to be safe…) Then perform the simulation again. This time, it should pass. Atthis point, you are ready to program the FPGA with your design. The Spartan-3 Starter Kit board may beprogrammed by two different methods. One is to program the FPGA by download cable. The other is toprogram the PROM by download cable, and then have the PROM program the FPGA. Both are coveredin the following sections.Programming the FPGA by Download CableProgramming the FPGA directly by the download cable is a convenient way to try out a design. Thismethod is useful when you want to quickly test something, or are not certain your design is final. Forexample, at this point you are fairly confident your design is correct. However, you should realize by thispoint in your education that complex designs rarely ever work “on the first try”. One of the greatadvantages FPGAs have over ASICs is that the penalty for being wrong on the first try is minimal.The first order of business is to create a programming file for the FPGA. Select two_input_xor in theSources in Project window. In the Processes for Current Source window, right click on GenerateProgramming File and then select Properties. The Process Properties dialog box appears. Select theConfiguration Options tab, as shown in Figure 58.60

Figure 58: Generate Programming File Process PropertiesChange the Unused IOB Pins option to Float. The other settings should already be correct, but make surethey match what is shown in Figure 59.Figure 59: IOB pin settingsNext, select the Startup Options tab, as shown in Figure 60.61

Figure 60: Generate Programming File Process PropertiesChange the FPGA Start-Up Clock option to JTAG Clock. The other settings should already be correct, butmake sure they match what is shown in Figure 59. Click “Ok” to save the settings.Confirm that two_input_xor is selected in the Sources in Project window. Then, double click on thegenerate Programming File process in the Processes for Current Source window. Project Navigator willgenerate a programming file and print information to the Console window in the process.Before you continue, you must have the Spartan-3 Starter Kit board, power supply, and download cableavailable. Connect the download cable to the parallel port of the machine you are using. Plug the powersupply into the wall. Loaok at the Spartan-3 Starter Kit board and identify the following. If you need help,ask the instructor to refer to the Spartan-3 Kit User Guide.• PROM jumper, JP1, at top right• Mode Jumper, J8, near Top Center62

• DC Power Jack, J4, at Left Center• Download Cable Connector, J7, at Top CenterMake sure that the PROM Jumper is set to Default and that the Mode Jumper has all three jumpersinstalled. You should have received the board in this state, but it is better to confirm. Then, insert thepower plug into the DC Power Jack. Be aware that if a programming file was previously stored in thePROM, it will automatically load, and may result in board activity, like flashing LEDs, etc. This can besafely ignored. Finally, connect the download cable to its connector, as shown in Figure 60.Figure 60: Download Cable ConnectionTo download your bitstream to the FPGA device, expand the Generate Programming File process bylicking on the + next to it, and then double click on the Configure Device (iMPACT) process. This willlaunch the iMPACT program in another window. You will be immediately presented with several dialogboxes, the first of which is shown in Figure 61.Figure 61: Configuration Mode SelectionThere are actually a bewildering number of ways to configure an FPGA device. The board has anintegrated JTAG programming function, which is also called Boundary-Scan mode. Select this option andproceed to the next dialog box.63

Allow the program to automatically connect to the cable and identify the devices on the board. After youfinish this sequence, the program will automatically detect the FPGA and PROM devices. and prompt youto specify a programming file for each device. You should see a message like that shown in Figure 62.Click “Ok”.Figure 62: NotificationIn the first file requestor, shown in Figure 63, select the two_input_xor.bit file you created with theimplementation process. This is the FPGA programming file.Figure 63: Selecting the FPGA Programming FileThe next file requestor, shown in Figure 64, asks for a PROM programming file. We are not programmingthe PROM at this time, therefore select Bypass.64

Figure 64: Placing the PROM in Bypass ModeAt this point, you should be ready to program the FPGA. If you have made a mistake, you can correct yourassignments by using the technique illustrated in Figure 65.Figure 65: Alternate File Assignment Method65

To correct a file assignment, or to make initial assignments if iMPACT does not automatically prompt youfor programming files, select the FPGA icon in the iMPACT window. Right click and select Assign NewConfiguration File. You will get a file requestor like that shown in Figure 63. You can repeat this processwith the PROM icon, and you will get a file requestor like that shown in Figure 64. Finally, you will reachthe point shown in Figure 66. iMPACT is ready to program the FPGA. Select the FPGA icon in the windowand then use the right mouse button to activate the menu as shown and select the Program option.Figure 66: Select Program DeviceYou will be presented with a dialog box listing programming options. Most of these options are ghostedout for FPGA programming and are of no concern, see Figure 67. Disable the Verify option, if selected,and then click “Ok” to start the programming sequence.66

Figure 67: Programming OptionsA progress indicator will appear. Once the programming is complete, the program will be sure to let youknow if it was successful or if it failed. If the programming has failed, re-check your cable connections, thepower connections, and the jumpers – and then try again. If it still fails, ask the instructor for assistance.Now, you can test your design in hardware. Locate SW0 and SW1 on the board, and exercise your designby trying the four possible combinations of switch settings while observing LD0. Does the circuit behaveas you expect? If it does not, seek assistance. If it does work properly, you are ready to try the otherprogramming method. Exit iMPACT (you do not need to save). Keep the board connected to power andthe download cable.Programming the PROM by Download CableThe other method is to program the PROM by download cable, and then have the PROM program theFPGA. Typically you would program the PROM when you believe your design is completely done. Afterthe PROM is programmed, each time the power is cycled, the FPGA will automatically load theprogramming file from the PROM. After the PROM is programmed, the need for the download cable iseliminated. Expand the Generate Programming File process by clicking on the + next to it, and thendouble click on the Generate PROM, ACE, or JTAG File process. This will launch the iMPACT programagain.You will be immediately presented with several dialog boxes, the first of which is shown in Figure 68.Select the PROM File option and proceed to the next dialog box, shown in Figure 68.67

Figure 68: PROM Property SelectionIn the dialog box of Figure 69, change the settings to match those shown. Do not forget to change thePROM File Name. Then proceed to the next dialog box.Figure 70: PROM Selection68

In the dialog box of Figure 70, select the XCF—XCF02S PROM type, and then click “Add”. You shouldsee the PROM listed in the sub-window, at position zero. Then click “Next”.Figure 71: Summary WindowFigure 71 shows a summary of what you have selected. If your results do not match that shown in Figure71, go “Back” and correct your error. Otherwise, click “Next” to proceed.Figure 72: Add FPGA Programming Files69