SSD1926 Application Note - Solomon Systech Limited

SSD1926 Application Note - Solomon Systech Limited

SSD1926 Application Note - Solomon Systech Limited

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

SOLOMON SYSTECHSEMICONDUCTOR TECHNICAL DATA<strong>SSD1926</strong> <strong>Application</strong> <strong>Note</strong>This document contains information on a product under development. <strong>Solomon</strong> <strong>Systech</strong> reserves the right to changeor discontinue this product without notice.http://www.solomon-systech.com<strong>SSD1926</strong>Rev 1.0 P 1/1 Jul 2009 Copyright © 2009 <strong>Solomon</strong> <strong>Systech</strong> <strong>Limited</strong><strong>Application</strong> <strong>Note</strong>

CONTENTS1 DISPLAY DATA FORMATS..................................................................................................... 52 REGISTERS TABLE .................................................................................................................. 62.1 REGISTER MAPPING...................................................................................................................................................62.2 READ-ONLY CONFIGURATION REGISTERS.................................................................................................................62.3 CLOCK CONFIGURATION REGISTERS .........................................................................................................................82.4 LOOK-UP TABLE REGISTERS ...................................................................................................................................102.4.1 Monochrome Modes....................................................................................................................................102.4.2 Color Modes ...............................................................................................................................................122.5 PANEL CONFIGURATION REGISTERS........................................................................................................................172.5.1 Monochrome 8-Bit Panel Timing................................................................................................................192.5.2 Color 8-Bit Panel Timing (Format stripe) ..................................................................................................202.5.3 Color 16-Bit Panel Timing..........................................................................................................................212.5.4 Generic TFT Panel Timing .........................................................................................................................232.5.5 Serial TFT Panel Timing ............................................................................................................................242.6 SMART PANEL CONFIGURATION REGISTERS............................................................................................................402.6.1 Write Through Mode...................................................................................................................................402.7 INTERRUPT REGISTERS ............................................................................................................................................522.8 POWER UP REGISTERS.............................................................................................................................................532.9 DISPLAY MODE REGISTERS .....................................................................................................................................552.10 MAIN WINDOW REGISTERS .....................................................................................................................................572.11 SCRATCH BIT REGISTERS.........................................................................................................................................592.12 GENERAL IO PINS REGISTERS .................................................................................................................................592.13 2D ENGINE REGISTERS............................................................................................................................................832.14 DISPLAY ROTATE MODE..........................................................................................................................................842.14.1 90° Display Rotate Mode............................................................................................................................842.14.2 180° Display Rotate Mode..........................................................................................................................852.14.3 270° Display Rotate Mode..........................................................................................................................862.15 FLOATING WINDOW MODE......................................................................................................................................872.15.1 Floating window under 90°Display Rotate Mode.......................................................................................872.15.2 Floating window under 180°Display Rotate Mode.....................................................................................882.15.3 Floating window under 270°Display Rotate Mode.....................................................................................882.16 CURSOR MODE ........................................................................................................................................................952.16.2 Cursor with 270° Display Rotate Mode...................................................................................................1012.17 DRAW2D MODE ....................................................................................................................................................1182.18 JPEG DECODE REGISTERS ....................................................................................................................................1302.18.1 Decode Procedure ....................................................................................................................................1302.19 MMC/SD/SDIO REGISTERS .................................................................................................................................145<strong>Solomon</strong> <strong>Systech</strong> Jul 2009 P 2/3 Rev 1.0<strong>SSD1926</strong><strong>Application</strong> <strong>Note</strong>

TABLESTABLE 2-1: SUGGESTED M & N VALUE ................................................................................................................................9TABLE 2-2: PANEL TIMING PARAMETER DEFINITION AND REGISTER SUMMARY ................................................................18TABLE 2-3: PANEL DATA WIDTH SELECTION......................................................................................................................27TABLE 2-4: LCD PANEL TYPE SELECTION..........................................................................................................................27TABLE 2-5: THE SETTING FOR DISPLAY POST-PROCESSING SATURATION.............................................................................34TABLE 2-6: THE SETTING FOR DISPLAY POST-PROCESSING BRIGHTNESS.............................................................................35TABLE 2-7: THE SETTING FOR DISPLAY POST-PROCESSING CONTRAST................................................................................35TABLE 2-8: THE RGB SEQUENCE FOR SERIAL-TFT INTERFACE..........................................................................................37TABLE 2-9: DATA TYPE FOR PARALLEL INTERFACE OF ALL PANEL TYPES............................................................................40TABLE 2-10: INPUT DATA FORMAT FOR WRITE THROUGH MODE........................................................................................40TABLE 2-11: DATA OUTPUT FORMAT FOR DISPLAY PIXEL IN PARALLEL INTERFACE............................................................41TABLE 2-12: DATA OUTPUT FORMAT FOR 4-WIRE SERIAL INTERFACE (REG[260H] BIT 6= 1) ............................................41TABLE 2-13: DATA OUTPUT FORMAT FOR 3-WIRE SERIAL INTERFACE (REG[260H] BIT 6= 0) ............................................42TABLE 2-14: DATA INPUT FORMAT FOR AUTO REFRESH MODE ..........................................................................................42TABLE 2-15: OUTPUT TIMING FOR 6800 PARALLEL INTERFACE..........................................................................................42TABLE 2-16: OUTPUT TIMING FOR 8080 PARALLEL INTERFACE..........................................................................................43TABLE 2-17: OUTPUT TIMING FOR SERIAL INTERFACE........................................................................................................44TABLE 2-18: REGISTER FOR SMART PANEL INTERFACE........................................................................................................46TABLE 2-19: LCD BIT-PER-PIXEL SELECTION.....................................................................................................................56TABLE 2-20: DISPLAY ROTATE MODE SELECT OPTIONS.....................................................................................................84TABLE 2-21: 32-BIT ADDRESS X INCREMENTS FOR VARIOUS COLOR DEPTHS....................................................................91TABLE 2-22: 32-BIT ADDRESS Y INCREMENTS FOR VARIOUS COLOR DEPTHS....................................................................92TABLE 2-23: 32-BIT ADDRESS X INCREMENTS FOR VARIOUS COLOR DEPTHS....................................................................93TABLE 2-24: 32-BIT ADDRESS Y INCREMENTS FOR VARIOUS COLOR DEPTHS....................................................................94TABLE 2-25: INDEXING SCHEME FOR HARDWARE CURSOR .................................................................................................95TABLE 2-26: X INCREMENT MODE FOR VARIOUS COLOR DEPTHS....................................................................................106TABLE 2-27: Y INCREMENT MODE FOR VARIOUS COLOR DEPTHS....................................................................................107TABLE 2-28: YUV OUTPUT RANGE SELECTION................................................................................................................131TABLE 2-29: JPEG FIFO THRESHOLD STATUS .................................................................................................................131TABLE 2-30: JPEG FIFO THRESHOLD STATUS .................................................................................................................133TABLE 2-31: JPEG FIFO TRIGGER THRESHOLD SELECTION.............................................................................................137TABLE 2-32: JPEG FIFO THRESHOLD STATUS .................................................................................................................137TABLE 2-33: YUV FORMAT SELECTION ...........................................................................................................................140TABLE 2-34: RST MARKER SELECTION ............................................................................................................................144TABLE 2-35: JPEG ERROR STATUS...................................................................................................................................145TABLE 2-36: DETERMINATION OF TRANSFER TYPE...........................................................................................................150TABLE 2-37: COMMAND REGISTER ...................................................................................................................................152TABLE 2-38: RELATION BETWEEN PARAMETERS AND THE NAME OF RESPONSE TYPE .....................................................152TABLE 2-39: RESPONSE BIT DEFINITION FOR EACH RESPONSE TYPE................................................................................153TABLE 2-40: THE RELATION BETWEEN COMMAND CRC ERROR AND COMMAND TIMEOUT ERROR..................................168TABLE 2-41: THE RELATION BETWEEN COMMAND CRC ERROR AND COMMAND TIMEOUT ERROR FOR AUTO CMDI2 ...173<strong>SSD1926</strong><strong>Application</strong> <strong>Note</strong>Rev 1.0 P 3/4 Jul 2009 <strong>Solomon</strong> <strong>Systech</strong>

FIGURESFIGURE 1-1: DISPLAY DATA MEMORY ORGANIZATION........................................................................................................5FIGURE 2-1: CLOCK CONFIGURATION....................................................................................................................................8FIGURE 2-2: 1 BIT-PER-PIXEL MONOCHROME MODE DATA OUTPUT PATH.........................................................................10FIGURE 2-3: 2 BIT-PER-PIXEL MONOCHROME MODE DATA OUTPUT PATH.........................................................................11FIGURE 2-4: 4 BIT-PER-PIXEL MONOCHROME MODE DATA OUTPUT PATH.........................................................................11FIGURE 2-5: 8 BIT-PER-PIXEL MONOCHROME MODE DATA OUTPUT PATH.........................................................................11FIGURE 2-6: 1 BIT-PER-PIXEL COLOR MODE DATA OUTPUT PATH.....................................................................................12FIGURE 2-7: 2 BIT-PER-PIXEL COLOR MODE DATA OUTPUT PATH.....................................................................................12FIGURE 2-8: 4 BIT-PER-PIXEL COLOR MODE DATA OUTPUT PATH.....................................................................................13FIGURE 2-9: 8 BIT-PER-PIXEL COLOR MODE DATA OUTPUT PATH .....................................................................................14FIGURE 2-10: PANEL TIMING PARAMETERS ........................................................................................................................18FIGURE 2-11: MONOCHROME 8-BIT PANEL TIMING ............................................................................................................19FIGURE 2-12: COLOR 8-BIT PANEL TIMING (FORMAT STRIPE) ............................................................................................20FIGURE 2-13: COLOR 16-BIT PANEL TIMING.......................................................................................................................21FIGURE 2-14: GENERIC TFT PANEL TIMING .......................................................................................................................23FIGURE 2-15: SERIAL TFT PANEL TIMING ..........................................................................................................................25FIGURE 2-16: 6800 TIMING DIAGRAM.................................................................................................................................43FIGURE 2-17: 8080 TIMING DIAGRAM.................................................................................................................................44FIGURE 2-18: 4 WIRES TIMING DIAGRAM ...........................................................................................................................45FIGURE 2-19: 3 WIRES TIMING DIAGRAM ...........................................................................................................................45FIGURE 2-20: GPIO[4:0] OUTPUT SETUP .............................................................................................................................61FIGURE 2-21: EXAMPLES FOR LCD SIGNALX BY NDPOFF AND ODD / EVEN BITS ............................................................79FIGURE 2-22: DISPLAY DATA BYTE/WORD SWAP...............................................................................................................83FIGURE 2-23: RELATIONSHIP BETWEEN SCREEN IMAGE AND IMAGE REFRESHED IN 90° DISPLAY ROTATE MODE.............84FIGURE 2-24: RELATIONSHIP BETWEEN SCREEN IMAGE AND IMAGE REFRESHED IN 180° DISPLAY ROTATE MODE...........85FIGURE 2-25: RELATIONSHIP BETWEEN SCREEN IMAGE AND IMAGE REFRESHED IN 270° DISPLAY ROTATE MODE...........86FIGURE 2-26: FLOATING WINDOW WITH DISPLAY ROTATE MODE DISABLED .....................................................................87FIGURE 2-27: FLOATING WINDOW WITH DISPLAY ROTATE MODE 90° ENABLED................................................................87FIGURE 2-28: FLOATING WINDOW WITH DISPLAY ROTATE MODE 180° ENABLED..............................................................88FIGURE 2-29: FLOATING WINDOW WITH DISPLAY ROTATE MODE 270° ENABLED..............................................................88FIGURE 2-30: DISPLAY PRECEDENCE IN HARDWARE CURSOR ............................................................................................96FIGURE 2-31: CURSORS ON THE MAIN WINDOW...................................................................................................................96FIGURE 2-32: CURSORS WITH DISPLAY ROTATE MODE 90° ENABLED.................................................................................97FIGURE 2-33: CURSORS WITH DISPLAY ROTATE MODE 180° ENABLED...............................................................................99FIGURE 2-34: CURSORS WITH DISPLAY ROTATE MODE 270° ENABLED.............................................................................101FIGURE 2-35: TIMING OF COMMAND INHIBIT (DAT) AND COMMAND INHIBIT (CMD) WITH DATA TRANSFER .................158FIGURE 2-36: TIMING OF COMMAND INHIBIT (DAT) FOR THE CASE OF RESPONSE WITH BUSY..........................................159FIGURE 2-37: TIMING OF COMMAND INHIBIT (CMD) FOR THE CASE OF NO RESPONSE COMMAND....................................159<strong>Solomon</strong> <strong>Systech</strong> Jul 2009 P 4/5 Rev 1.0<strong>SSD1926</strong><strong>Application</strong> <strong>Note</strong>

1 Display Data FormatsThe following diagrams show the display mode data formats.1 bpp:Byte 0bit 7 bit 0A0 A1 A2 A3 A4 A5 A6 A7P0 P1 P2 P3 P4 P5 P6 P7Byte 1Byte 2A8 A9 A10 A11 A12 A13 A14 A15A16 A17 A18 A19 A20 A21 A22 A23LUTPn = RGB value from LUTIndex (An)Host AddressDisplay BufferPanel Display2 bpp:Byte 0bit 7 bit 0A0 B0 A1 B1 A2 B2 A3 B3P0 P1 P2 P3 P4 P5 P6 P7Byte 1Byte 2A4 B4 A5 B5 A6 B6 A7 B7A8 B8 A9 B9 A10 B10 A11 B11LUTPn = RGB value from LUTIndex (An, Bn)Host AddressDisplay BufferA is MSB, B is LSBPanel Display4 bpp:Byte 0bit 7 bit 0A0 B0 C0 D0 A1 B1 C1 D1P0 P1 P2 P3 P4 P5 P6 P7Byte 1Byte 2A2 B2 C2 D2 A3 B3 C3 D3A4 B4 C4 D4 A5 B5 C5 D5LUTPn = RGB value from LUTIndex (An, Bn, Cn, Dn)Host AddressDisplay BufferA is MSB, D is LSBPanel Display8 bpp:Byte 0bit 7 bit 0A0 B0 C0 D0 E0 F0 G0 H0P0 P1 P2 P3 P4 P5 P6 P7Byte 1Byte 2A1 B1 C1 D1 E1 F1 G1 H1A2 B2 C2 D2 E2 F2 G2 H2LUTPn = RGB value from LUT Index(An, Bn, Cn, Dn, En, Fn, Gn, Hn)Host AddressDisplay BufferA is MSB, H is LSBPanel Display16 bpp: bit 7 bit 0P0 P1 P2 P3 P4 P5 P6 P7Byte 0Byte 1Byte 2Byte 3Host Address2G04R02G14R11G03R01G13R1G00 4B02R01R0G10 4B12R11R13B03B12B0R00 5G02B1R10 5G1Display Buffer1B04G01B14G10B03G00B13G1Bypasses LUTPn = (Rn4-0 , Gn5-0 , Bn4-0 )Panel DisplayR032 bpp:bit 7 bit 0Byte 07R06R05R04R01R00R0R03 2Byte 1G0 7 G0 6 G0 5 G0 4 G0 3 G0 2 G0 1 G0 0Byte 27B06B05B04B03B02B01B00B07 6 5 4 3 2 1 3Byte 3A0 A0 A0 A0 A0 A0 A0 A0Byte 4 75 41R16R1 R1 20R1R1 R1 R1Host AddressDisplay BufferBypasses LUTP0 P1 P2 P3 P4 P5 P6 P7Pn = (Rn7-0 , Gn7-0 , Bn7-0 , An7-0 )Panel DisplayFigure 1-1: Display Data Memory Organization<strong>Note</strong>1. For 16 bpp format, Rn, Gn, Bn represent the red, green, and blue color components.2. For 32 bpp format, Rn, Gn, Bn, An represent the red, green, blue color and alpha blending components.<strong>SSD1926</strong><strong>Application</strong> <strong>Note</strong>Rev 1.0 P 5/6 Jul 2009 <strong>Solomon</strong> <strong>Systech</strong>

2 REGISTERS TABLEThis document discusses how and where to access the <strong>SSD1926</strong> registers. It also provides detailedinformation about the layout and usage of each register.2.1 Register MappingThe <strong>SSD1926</strong> registers are memory-mapped. When the system decodes the input pins as CS# = 0 andM/R# = 0, the registers may be accessed. The register space is decoded by A[18:0].Unless specified otherwise, all register bits are set to 0 during power-on or software reset (REG[A2h]bit 0 = 1). All bits marked “0” should be programmed as zero. All bits marked “1” should beprogrammed as one.Key :RO : Read Only. Writes to these bits are ignored.ROC : Read Only and initialized to zero at reset. Writes to these bits are ignored.WO : Write OnlyRW : Read / WriteRW1C : Read Only. Write 1 to clear status. Writing a 0 to these bits has no effect.RWAC : Read-Write, automatic clear. Writing a 0 to these bits has no effect.NA : Not ApplicableX : Don’t care2.2 Read-Only Configuration RegistersDebug Code RegisterREG[00h]Bit 7 6 5 4 3 2 1 0DebugCodeBit 7DebugCodeBit 6DebugCodeBit 5DebugCodeBit 4DebugCodeBit 3DebugCodeBit 2DebugCodeBit 1DebugCodeBit 0Type RO RO RO RO RO RO RO ROResetstate0 0 1 0 1 0 0 0Bits 7-0Debug CodeThese bits show the dummy value for debug purpose. The readback code is 00101000.Read Dummy RegisterREG[01h]Bit 7 6 5 4 3 2 1 0DebugCodeBit 7DebugCodeBit 6DebugCodeBit 5DebugCodeBit 4DebugCodeBit 3DebugCodeBit 2DebugCodeBit 1DebugCodeBit 0Type RO RO RO RO RO RO RO ROResetstate1 0 0 0 0 0 0 0Bits 7-0Debug CodeThese bits show the dummy value for debug purpose. The readback code is 10000000.<strong>Solomon</strong> <strong>Systech</strong> Jul 2009 P 6/7 Rev 1.0<strong>SSD1926</strong><strong>Application</strong> <strong>Note</strong>

Configuration Readback RegisterREG[02h]Bit 7 6 5 4 3 2 1 0Reserved CNF6StatusReserved CNF4StatusCNF3StatusCNF2StatusCNF1StatusCNF0StatusType RO RO RO RO RO RO RO ROResetstateX X X X X X X XBits 7-0CNF[6:0] StatusThese status bits return the status of the configuration pins CNF[6:0]. CNF[4:0] are latched atthe rising edge of RESET# or software reset (REG[A2h] bit 0 = 1).Bit 7 = Bit 6Bit 5 = Bit 4Product Code RegisterREG[03h]Bit 7 6 5 4 3 2 1 0ProductCodeProductCodeProductCodeProductCodeProductCodeProductCodeRevisionCode Bit 1RevisionCode Bit 0Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0Type RO RO RO RO RO RO RO ROResetstate1 0 0 0 0 0 0 0Bits 7-2 Product Code Bits [5:0]These are read-only bits that indicate the product code.The product code of <strong>SSD1926</strong> is 100000.Bits 1-0 Revision Code Bits [1:0]These are read-only bits that indicate the revision code which readback value is 00.Memory status RegisterREG[05h]Bit 7 6 5 4 3 2 1 0Reserved Reserved AD_MODE Reserved Reserved Reserved Reserved ReservedStatusType RO RO RO RO RO RO RO ROResetstate1 X X 0 0 0 0 0Bits 7, 4-0Bits 6-5Reserved bitsAD_MODE StatusThese status bits return the status of the configuration pin AD_MODE which is latched at therising edge of RESET# or software reset (REG[A2h] bit 0 = 1).Bit 6 = Bit 5<strong>SSD1926</strong><strong>Application</strong> <strong>Note</strong>Rev 1.0 P 7/8 Jul 2009 <strong>Solomon</strong> <strong>Systech</strong>

2.3 Clock Configuration RegistersPLL_CLKREG[126-127h]MCLK DividerREG[04h] orCNF7:6MCLKSDHC DividerREG[1001h]andREG[112Dh]SD_CLKPCLK DividerREG[15A-158h]PCLKFigure 2-1: Clock configurationPLL Clock Setting Register 0REG[126h]Bit 7 6 5 4 3 2 1 0PLL enablebitReserved Reserved N value bit4N value bit3N value bit2N value bit1N value bit0Type RW RW RW RW RW RW RW RWResetstate0 0 0 1 0 0 0 0Bit 7PLL enable bit1 Enable PLL. PLL_DIS should tie to IOVSS and clock source should be providedthrough CLKI and CLKO(optional).0 Disable PLL. PLL_DIS should tie to IOVDD and clock source should be providedthrough CLKI2.Bits 6-5Reserved bitsBits 4-0 N value bits [4:0]This register is used to program the N value for clock frequency<strong>Note</strong> : The value of N should be greater than 1.PLL Clock Setting Register 1REG[127h]Bit 7 6 5 4 3 2 1 0M value bit7M value bit6M value bit5M value bit4M value bit3M value bit2M value bit1M value bit0Type RW RW RW RW RW RW RW RWResetstate1 0 0 0 0 0 0 0Bits 7-0 M value bits [7:0]This register is used to program the M value for clock frequency<strong>Note</strong> : The value of M should be greater than 1.<strong>Solomon</strong> <strong>Systech</strong> Jul 2009 P 8/9 Rev 1.0<strong>SSD1926</strong><strong>Application</strong> <strong>Note</strong>

PLL Clock Setting Register 2REG[12Bh]Bit 7 6 5 4 3 2 1 0PLL configvalue bit 7PLL configbit 6PLL configbit 5PLL configbit 4PLL configbit 3PLL configbit 2PLL configbit 1PLL configbit 0Type RW RW RW RW RW RW RW RWResetstate1 0 0 0 1 1 1 0Bits 7-0 PLL configuration value bits [7:0]This register is used to config the PLL setting. This register should be programmed to 0xAE.Bits 7:5 : control the internal reference clock value when PLL is not lockedBits 4:0 : control the bias current of PLL (b’0x00000 is not allowed)Program sequence (example input clock frequency = 2MHz) :1. Write the N value (REG[126h] = 0x05)2. Write the M value (REG[127h] = 0xC8)3. Write the PLL Conf value (REG[12Bh] = 0xAE)4. Enable the PLL (REG[126h] = 0x85)Then, the PLL output clock frequency = Input clock frequency * (M / N) = 80MHzMaximum output clock frequency = 85MHzTable 2-1: Suggested M & N valueInput clock frequency N value M value2MHz 0x05 0xC82.5MHz 0x06 0xC03MHz 0x08 0xD53.5MHz 0x09 0xCE4Mz 0x0A 0xC8Memory Clock Configuration RegisterREG[04h]Bit 7 6 5 4 3 2 1 00 0 0 MCLKDivideSelect Bit 4MCLKDivideSelect Bit 3MCLKDivideSelect Bit 2MCLKDivideSelect Bit 1MCLKDivideSelect Bit 0Type RO RW RW RW RW RW RW RWResetstate0 0 0 0 0 0 0 0Bits 7-5Reserved bitsBits 4-0 MCLK Divide Select Bits [4:0]These bits determine the divide used to generate the Memory Clock (MCLK) from the PLLoutput frequency. Refer to REG[126h], REG[127h] for the PLL output frequency.MCLK Frequency = PLL output frequency / (MCLK divide value + 1)<strong>SSD1926</strong><strong>Application</strong> <strong>Note</strong>Rev 1.0 P 9/10 Jul 2009 <strong>Solomon</strong> <strong>Systech</strong>

PCLK Frequency Ratio Register 0REG[158h]Bit 7 6 5 4 3 2 1 0PCLKRatio bit 7PCLKRatio bit 6PCLKRatio bit 5PCLKRatio bit 4PCLKRatio bit 3PCLKRatio bit 2PCLKRatio bit 1PCLKRatio bit 0Type RW RW RW RW RW RW RW RWResetstate0 0 0 0 0 0 0 0PCLK Frequency Ratio Register 1REG[159h]Bit 7 6 5 4 3 2 1 0PCLKRatio bit 15PCLKRatio bit 14PCLKRatio bit 13PCLKRatio bit 12PCLKRatio bit 11PCLKRatio bit 10PCLKRatio bit 9PCLKRatio bit 8Type RW RW RW RW RW RW RW RWResetstate0 0 0 0 0 0 0 0PCLK Frequency Ratio Register 2REG[15Ah]Bit 7 6 5 4 3 2 1 0Reserved Reserved Reserved Reserved PCLKRatio bit 19PCLKRatio bit 18PCLKRatio bit 17PCLKRatio bit 16Type RO RO RO RO RW RW RW RWResetstate0 0 0 0 0 0 0 0REG[15Ah] Bits 3-0,REG[159h] Bits 7-0,REG[158h] Bits 7-0PCLK Frequency Ratio [19:0]These bits determine the Frequency for PCLK.PCLK frequency = MCLK frequency * (PCLK Frequency Ratio + 1) / (2 20 )<strong>Note</strong>(1)Bit[19:0] are used for non Serial-TFT panel type (REG[10h] bit 2:0 not equal to 010)(2)Bit[17:0] are used for Serial-TFT panel type (REG[10h] bit 2:0 equal to 010)(3)PCLK = MCLK (Bit[19:0] = 0xFFFFF) for smart panel interface.2.4 Look-Up Table RegistersThe following sections are the Look-up Table architecture which shows the display data output path only.2.4.1 Monochrome ModesThe green Look-Up Table (LUT) is used for all monochrome modes.Green Look-Up Table 256x61 bit-per-pixel datafrom Display Buffer00016-bit Gray DataFigure 2-2: 1 Bit-per-pixel Monochrome Mode Data Output Path<strong>Solomon</strong> <strong>Systech</strong> Jul 2009 P 10/11 Rev 1.0<strong>SSD1926</strong><strong>Application</strong> <strong>Note</strong>

Green Look-Up Table 256x62 bit-per-pixel datafrom Display Buffer000102036-bit Gray DataFigure 2-3: 2 Bit-per-pixel Monochrome Mode Data Output PathGreen Look-Up Table 256x64 bit-per-pixel datafrom Display Buffer000102030405060708090A0B0C0D0E0F6-bit Gray DataFigure 2-4: 4 Bit-per-pixel Monochrome Mode Data Output PathGreen Look-Up Table 256x68 bit-per-pixel datafrom Display Buffer0001020304050607F8F9FAFBFCFDFEFF6-bit Gray DataFigure 2-5: 8 Bit-per-pixel Monochrome Mode Data Output PathFor 16/32 bit-per-pixel monochrome Mode, the LUT is bypassed and the green data is directly mapped for this colordepth – See Figure 1-1.<strong>SSD1926</strong><strong>Application</strong> <strong>Note</strong>Rev 1.0 P 11/12 Jul 2009 <strong>Solomon</strong> <strong>Systech</strong>

2.4.2 Color ModesRed Look-Up Table 256x600016-bit Red Data1 bit-per-pixel datafrom Display BufferGreen Look-Up Table 256x600016-bit Green DataBlue Look-Up Table 256x600016-bit Blue DataFigure 2-6: 1 Bit-Per-Pixel Color Mode Data Output PathRed Look-Up Table 256x6000102036-bit Red DataGreen Look-Up Table 256x62 bit-per-pixel datafrom Display Buffer000102036-bit Green DataBlue Look-Up Table 256x6000102036-bit Blue DataFigure 2-7: 2 Bit-Per-Pixel Color Mode Data Output Path<strong>Solomon</strong> <strong>Systech</strong> Jul 2009 P 12/13 Rev 1.0<strong>SSD1926</strong><strong>Application</strong> <strong>Note</strong>

Red Look-Up Table 256x6000102030405060708090A0B0C0D0E0F6-bit Red Data4 bit-per-pixel datafrom Display BufferGreen Look-Up Table 256x6000102030405060708090A0B0C0D0E0F6-bit Green DataBlue Look-Up Table 256x6000102030405060708090A0B0C0D0E0F6-bit Blue DataFigure 2-8: 4 Bit-Per-Pixel Color Mode Data Output Path<strong>SSD1926</strong><strong>Application</strong> <strong>Note</strong>Rev 1.0 P 13/14 Jul 2009 <strong>Solomon</strong> <strong>Systech</strong>

Red Look-Up Table 256x600010203040506076-bit Red DataF8F9FAFBFCFDFEFF8 bit-per-pixel datafrom Display BufferGreen Look-Up Table 256x60001020304050607F8F9FAFBFCFDFEFF6-bit Green DataBlue Look-Up Table 256x600010203040506076-bit Blue DataF8F9FAFBFCFDFEFFFigure 2-9: 8 Bit-per-pixel Color Mode Data Output PathFor 16/32 bit-per-pixel color mode, the LUT is bypassed and the color data is directly mapped for this color depth – SeeFigure 1-1.<strong>Solomon</strong> <strong>Systech</strong> Jul 2009 P 14/15 Rev 1.0<strong>SSD1926</strong><strong>Application</strong> <strong>Note</strong>

Look-Up Table Blue Write Data RegisterREG[08h]Bit 7 6 5 4 3 2 1 0LUT BlueWrite DataBit 7LUT BlueWrite DataBit 6LUT BlueWrite DataBit 5LUT BlueWrite DataBit 4LUT BlueWrite DataBit 3LUT BlueWrite DataBit 2LUT BlueWrite DataBit 1LUT BlueWrite DataBit 0Type WO WO WO WO WO WO WO WOResetstate0 0 0 0 0 0 0 0Bits 7-0 LUT Blue Write Data Bits [7:0]This register contains the data to be written to the blue component of the Look-Up Table.The data is stored in this register until a write to the LUT Write Address register (REG[0Bh])moves the data into the Look-Up Table.<strong>Note</strong>The LUT entry is updated only when the LUT Write Address Register (REG[0Bh]) is written.Look-Up Table Green Write Data RegisterREG[09h]Bit 7 6 5 4 3 2 1 0LUT GreenWrite DataBit 7LUT GreenWrite DataBit 6LUT GreenWrite DataBit 5LUT GreenWrite DataBit 4LUT GreenWrite DataBit 3LUT GreenWrite DataBit 2LUT GreenWrite DataBit 1LUT GreenWrite DataBit 0Type WO WO WO WO WO WO WO WOResetstate0 0 0 0 0 0 0 0Bits 7-0 LUT Green Write Data Bits [7:0]This register contains the data to be written to the green component of the Look-Up Table.The data is stored in this register until a write to the LUT Write Address register (REG[0Bh])moves the data into the Look-Up Table.<strong>Note</strong>The LUT entry is updated only when the LUT Write Address Register (REG[0Bh]) is written.Look-Up Table Red Write Data RegisterREG[0Ah]Bit 7 6 5 4 3 2 1 0LUT RedWrite DataBit 7LUT RedWrite DataBit 6LUT RedWrite DataBit 5LUT RedWrite DataBit 4LUT RedWrite DataBit 3LUT RedWrite DataBit 3LUT RedWrite DataBit 1LUT RedWrite DataBit 0Type WO WO WO WO WO WO WO WOResetstate0 0 0 0 0 0 0 0Bits 7-0 LUT Red Write Data Bits [7:0]This register contains the data to be written to the red component of the Look-Up Table.The data is stored in this register until a write to the LUT Write Address register (REG[0Bh])moves the data into the Look-Up Table.<strong>Note</strong>The LUT entry is updated only when the LUT Write Address Register (REG[0Bh]) is written.<strong>SSD1926</strong><strong>Application</strong> <strong>Note</strong>Rev 1.0 P 15/16 Jul 2009 <strong>Solomon</strong> <strong>Systech</strong>

Look-Up Table Write Address RegisterREG[0Bh]Bit 7 6 5 4 3 2 1 0LUT WriteAddress Bit7LUT WriteAddress Bit6LUT WriteAddress Bit5LUT WriteAddress Bit4LUT WriteAddress Bit3LUT WriteAddress Bit2LUT WriteAddress Bit1LUT WriteAddress Bit0Type WO WO WO WO WO WO WO WOResetstate0 0 0 0 0 0 0 0Bits 7-0 LUT Write Address Bits [7:0]This register is a pointer to the Look-Up Table (LUT) which is used to write LUT data stored inREG[08h], REG[09h], and REG[0Ah]. The data is updated to the LUT only with thecompletion of a write to this register. This is a write-only register and returns 00h if read.<strong>Note</strong>The <strong>SSD1926</strong> has three 256-entry, 8-bit-wide LUTs, one for each of red, green and blue (seeSection “Look-Up Table Architecture” in datasheet).Look-Up Table Blue Read Data RegisterREG[0Ch]Bit 7 6 5 4 3 2 1 0LUT BlueRead DataBit 7LUT BlueRead DataBit 6LUT BlueRead DataBit 5LUT BlueRead DataBit 4LUT BlueRead DataBit 3LUT BlueRead DataBit 2LUT BlueRead DataBit 1LUT BlueRead DataBit 0Type RO RO RO RO RO RO RO ROResetstate0 0 0 0 0 0 0 0Bits 7-0 LUT Blue Read Data Bits [7:0]This register contains the data from the blue component of the Look-Up Table. The LUT entryread is controlled by the LUT Read Address Register (REG[0Fh]).<strong>Note</strong>This register is updated only when the LUT Read Address Register (REG[0Fh]) is written.Look-Up Table Green Read Data RegisterREG[0Dh]Bit 7 6 5 4 3 2 1 0LUT GreenRead DataBit 7LUT GreenRead DataBit 6LUT GreenRead DataBit 5LUT GreenRead DataBit 4LUT GreenRead DataBit 3LUT GreenRead DataBit 2LUT GreenRead DataBit 1LUT GreenRead DataBit 0Type RO RO RO RO RO RO RO ROResetstate0 0 0 0 0 0 0 0Bits 7-0 LUT Green Read Data Bits [7:0]This register contains the data from the green component of the Look-Up Table. The LUT entryread is controlled by the LUT Read Address Register (REG[0Fh]).<strong>Note</strong>This register is updated only when the LUT Read Address Register (REG[0Fh]) is written.<strong>Solomon</strong> <strong>Systech</strong> Jul 2009 P 16/17 Rev 1.0<strong>SSD1926</strong><strong>Application</strong> <strong>Note</strong>

Look-Up Table Red Read Data RegisterREG[0Eh]Bit 7 6 5 4 3 2 1 0LUT RedRead DataBit 7LUT RedRead DataBit 6LUT RedRead DataBit 5LUT RedRead DataBit 4LUT RedRead DataBit 3LUT RedRead DataBit 2LUT RedRead DataBit 1LUT RedRead DataBit 0Type RO RO RO RO RO RO RO ROResetstate0 0 0 0 0 0 0 0Bits 7-0 LUT Red Read Data Bits [7:0]This register contains the data from the red component of the Look-Up Table. The LUT entryread is controlled by the LUT Read Address Register (REG[0Fh]).<strong>Note</strong>This register is updated only when the LUT Read Address Register (REG[0Fh]) is written.Look-Up Table Read Address RegisterREG[0Fh]Bit 7 6 5 4 3 2 1 0LUT ReadAddress Bit7LUT ReadAddress Bit6LUT ReadAddress Bit5LUT ReadAddress Bit4LUT ReadAddress Bit3LUT ReadAddress Bit2LUT ReadAddress Bit1LUT ReadAddress Bit0Type WO WO WO WO WO WO WO WOResetstate0 0 0 0 0 0 0 0Bits 7-0 LUT Read Address Bits [7:0]This register is a pointer to the Look-Up Table (LUT) which is used to read LUT data and storeit in REG[0Ch], REG[0Dh], REG[0Eh]. The data is read from the LUT only when a write tothis register is completed. This is a write-only register and returns 00h if read.<strong>Note</strong>The <strong>SSD1926</strong> has three 256-entry, 8-bit-wide LUTs, one for each of red, green and blue (seeSection “Look-Up Table Architecture” in datasheet).2.5 Panel Configuration RegistersFigure 2-10 shows the timing parameters required to drive a flat panel display. Timing details for eachsupported panel types are provided in the remainder of this section.<strong>SSD1926</strong><strong>Application</strong> <strong>Note</strong>Rev 1.0 P 17/18 Jul 2009 <strong>Solomon</strong> <strong>Systech</strong>

HTHDPSHPSHPWVDPSHDPVTVPSVDPVPWFigure 2-10: Panel Timing ParametersTable 2-2: Panel Timing Parameter Definition and Register SummarySymbol Description Derived From UnitsHT Horizontal Total ((REG[12h] bits 7-0) + 1) x 8 + (REG[13h] bits 2-0)HDP 2 Horizontal Display Period 2 ((REG[14h] bits 6-0) + 1) x 8HDPS Horizontal Display Period Start Position ((REG[17h]bits 2-0,REG[16h]bits7-0))Ts 1HPS LLINE Pulse Start Position (REG[23h] bits 2-0, REG[22h] bits 7-0) + 1HPW LLINE Pulse Width (REG[20h] bits 6-0) + 1VT Vertical Total ((REG[19h] bits 2-0, REG[18h] bits 7-0) + 1) xHTVDP 3 Vertical Display Period 3 ((REG[1Dh] bits 1-0, REG[1Ch] bits 7-0) + 1) xHTVDPS Vertical Display Period Start Position (REG[1Fh] bits 2-0, REG[1Eh] bits 7-0) x HTVPS LFRAME Pulse Start Position (REG[27h] bits 2-0, REG[26h] bits 7-0) x HT +Ts 1(REG[31h] bits 2-0, REG[30h] bits 7-0)VPW LFRAME Pulse Width ((REG[24h] bits 2-0) + 1) x HT + (REG[35h] bits2-0, REG[34h] bits 7-0) – (REG[31h] bits 2-0,REG[30h] bits 7-0)The following conditions must be fulfilled for all panel timings:HDPS + HDP < HTVDPS + VDP < VT1Ts = pixel clock period2The HDP must be a minimum of 32 pixels and can be increased by multiples of 8.3The VDP must be a minimum of 2 lines.<strong>Solomon</strong> <strong>Systech</strong> Jul 2009 P 18/19 Rev 1.0<strong>SSD1926</strong><strong>Application</strong> <strong>Note</strong>

2.5.1 Monochrome 8-Bit Panel TimingVDPVNDPLFRAMELLINELDEN (MOD)LDATA[7:0]LINE1LINE2LINE3LINE479LINE480LINE1LINE2LLINELDEN (MOD)LSHIFTHDPHNDPLDATA71-11-91-633LDATA61-21-101-634LDATA51-31-111-635LDATA41-41-121-636LDATA31-51-131-637LDATA21-61-141-638LDATA11-71-151-639LDATA01-81-161-640*Diagram drawn with 2 LLINE vertical blank periodExample timing for a 640x480 panelFigure 2-11: Monochrome 8-Bit Panel TimingVDP = Vertical Display Period= (REG[1Dh] bits 1:0, REG[1Ch] bits 7:0) + 1 LinesVNDP = Vertical Non-Display Period= VT-VDPHDP= (REG[19h] bits 2:0, REG[18h] bits 7:0) - (REG[1Dh] bits 1:0, REG[1Ch] bits 7:0) Lines= Horizontal Display Period= ((REG[14h] bits 6:0) + 1) x 8TsHNDP = Horizontal Non-Display Period= HT - HDP= (((REG[12h] bits 7:0) + 1) x 8Ts + (REG[13h] bits 2-0)) - (((REG[14h] bits 6:0) + 1) x 8Ts)<strong>SSD1926</strong><strong>Application</strong> <strong>Note</strong>Rev 1.0 P 19/20 Jul 2009 <strong>Solomon</strong> <strong>Systech</strong>

2.5.2 Color 8-Bit Panel Timing (Format stripe)VDPVNDPLFRAMELLINELDEN (MOD)LDATA[7:0]LINE1LINE2LINE3LINE479LINE480LINE1LINE2LLINELDEN (MOD)LSHIFTHDPHNDPLDATA71-R11-B31-G61-G638LDATA61-G11-R41-B61-B638LDATA51-B11-G41-R71-R639LDATA41-R21-B41-G71-G639LDATA31-G21-R51-B71-B639LDATA21-B21-G51-R81-R640LDATA11-R31-B51-G81-G640LDATA01-G31-R61-B81-B640*Diagram drawn with 2 LLINE vertical blank periodExample timing for a 640X480 panelFigure 2-12: Color 8-Bit Panel Timing (Format stripe)VDP = Vertical Display Period= (REG[1Dh] bits 1:0, REG[1Ch] bits 7:0) + 1 LinesVNDP = Vertical Non-Display Period= VT-VDPHDP= (REG[19h] bits 2:0, REG[18h] bits 7:0) - (REG[1Dh] bits 1:0, REG[1Ch] bits 7:0) Lines= Horizontal Display Period= ((REG[14h] bits 6:0) + 1) x 8TsHNDP = Horizontal Non-Display Period= HT - HDP= (((REG[12h] bits 7:0) + 1) x 8Ts + (REG[13h] bits 2-0) ) - (((REG[14h] bits 6:0) + 1) x 8Ts)<strong>Solomon</strong> <strong>Systech</strong> Jul 2009 P 20/21 Rev 1.0<strong>SSD1926</strong><strong>Application</strong> <strong>Note</strong>

2.5.3 Color 16-Bit Panel TimingVDPVNDPLFRAMELLINELDEN (MOD)LDATA[7:0]LINE1LINE2LINE3LINE479LINE480LINE1LINE2LLINELDEN (MOD)LSHIFTHDPHNDPLDATA151-R11-G61-B111-G635LDATA141-B11-R71-G121-G636LDATA131-G21-B71-R131-R637LDATA121-R31-G81-B131-B637LDATA71-B31-R91-G141-G638LDATA61-G41-B91-R151-R639LDATA51-R51-G10 1-B151-B639LDATA41-B51-R11 1-G161-G640LDATA111-G11-B61-R121-R636LDATA101-R21-G71-B121-B636LDATA91-B21-R81-G131-G637LDATA81-G31-B81-R141-R638LDATA31-R41-G91-B141-B638LDATA21-B41-R10 1-G151-G639LDATA11-G51-B101-R161-R640LDATA01-R61-G11 1-B161-B640*Diagram drawn with 2 LLINE vertical blank periodExample timing for a 640X480 panelFigure 2-13: Color 16-Bit Panel Timing<strong>SSD1926</strong><strong>Application</strong> <strong>Note</strong>Rev 1.0 P 21/22 Jul 2009 <strong>Solomon</strong> <strong>Systech</strong>

VDP = Vertical Display Period= (REG[1Dh] bits 1:0, REG[1Ch] bits 7:0) + 1 LinesVNDP = Vertical Non-Display Period= VT-VDPHDP= (REG[19h] bits 2:0, REG[18h] bits 7:0) - (REG[1Dh] bits 1:0, REG[1Ch] bits 7:0) Lines= Horizontal Display Period= ((REG[14h] bits 6:0) + 1) x 8TsHNDP = Horizontal Non-Display Period= HT - HDP= (((REG[12h] bits 7:0) + 1) x 8Ts + (REG[13h] bits 2-0) ) - (((REG[14h] bits 6:0) + 1) x 8Ts)<strong>Solomon</strong> <strong>Systech</strong> Jul 2009 P 22/23 Rev 1.0<strong>SSD1926</strong><strong>Application</strong> <strong>Note</strong>

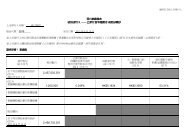

Analyse de la professionPeintre en production industrielleTÂCHE 6 :EXÉCUTER DES TESTSOPÉRATIONSSOUS-OPÉRATIONS6.1 Prendre connaissance des spécifications.6.2 Préparer les appareils et les instruments.6.3 Appliquer la procédure de test.6.4 Consigner les résultats.6.5 Transmettre les résultats.6.1.1 Prendre connaissance des spécificationsdu client, du fournisseur ou desspécifications à l’interne.6.1.2 Prendre connaissance des normesapplicables (environnementales etpropres au domaine de référence).6.2.1 Calibrer les appareils et les instruments.Commentaire : il faut effectuer une lecturevisuelle en conformité avec les standardsreconnus (ASTM, SSPC, etc.) et avec lesstandards du client et les procédures reconnues àl’interne.6.4.1 Rédiger un rapport (sur papier ou àl’aide d’un logiciel).6.4.2 Compiler des statistiques.6.4.3 Archiver les résultats selon la procédureinterne ou la demande du client.6.4.4 Prendre les mesures nécessaires à latraçabilité.6.5.1 Transmettre un rapport.6.5.2 Transmettre une procédure.6.5.3 Afficher de l’information.6.5.4 Organiser une rencontre ou une activitéde formation.CSMOFMI 23

= [(REG[1Dh]bits1-0,REG[1Ch]bits7-0) + 1] lines* The VDP must be a minimum of 2 linesHT = Horizontal Total= [((REG[12h] bits 7-0) + 1) x 8 + (REG[13h] bits 2-0)] pixelsHPS = LLINE Pulse Start Position= [(REG[23h] bits 2-0, REG[22h] bits 7-0) + 1] pixelsHPW = LLINE Pulse Width= [(REG[20h] bits 6-0)+ 1] pixelsHDPS = Horizontal Display Period Start Position= [(REG[17h] bits 2-0, REG[16h] bits 7-0) + 5] pixelsHDP = Horizontal Display Period= [((REG[14h] bits 6-0) + 1) x 8] pixelsThe HDP must be a minimum of 32 pixels and can be increased by multiples of 8.*Panel Type Bits (REG[10h] bits 2-0) = 001 (TFT)*LLINE Pulse Polarity Bit (REG[24h] bit 7) = 0 (active low)*LFRAME Polarity Bit (REG[20h] bit 7) = 0 (active low)2.5.5 Serial TFT Panel Timing<strong>Solomon</strong> <strong>Systech</strong> Jul 2009 P 24/25 Rev 1.0<strong>SSD1926</strong><strong>Application</strong> <strong>Note</strong>

VT (= 1 Frame)VPSVPWLFRAMEVDPSVDPLLINELDENLDATA[7:0]HT (= 1 Line)HPSHPWLLINELSHIFTLDENHDPSHDPLDATA[7:0]Figure 2-15: Serial TFT Panel TimingVT = Vertical Total= [(REG[19h] bits 2-0, REG[18h] bits 7-0) + 1] linesVPS = LFRAME Pulse Start Position= [(REG[27h] bits 2-0, REG[26h] bits 7-0)] x HT + (REG[31h] bits 2-0, REG[30h] bits 7-0) pixelsVPW = LFRAME Pulse Width= [(REG[24h]bits2-0)+ 1] x HT + (REG[35h] bits 2-0, REG[34h] bits 7-0) – (REG[31h] bits 2-0,REG[30h] bits 7-0) pixelsVDPS = Vertical Display Period Start Position= [(REG[1Fh]bits2-0,REG[1Eh]bits7-0)] linesVDP = Vertical Display Period= [(REG[1Dh]bits1-0,REG[1Ch]bits7-0)+ 1] lines* The VDP must be a minimum of 2 lines<strong>SSD1926</strong><strong>Application</strong> <strong>Note</strong>Rev 1.0 P 25/26 Jul 2009 <strong>Solomon</strong> <strong>Systech</strong>

HT = Horizontal Total= [(REG[12h] bits 7-0) x 8 + (REG[13h] bits 2-0) + 1] pixelsHPS = LLINE Pulse Start Position= [(REG[23h] bits 2-0, REG[22h] bits 7-0) + 1] pixelsHPW = LLINE Pulse Width= [(REG[20h] bits 6-0)+ 1] pixelsHDPS = Horizontal Display Period Start Position= [(REG[17h] bits 2-0, REG[16h] bits 7-0) ] pixelsHDP = Horizontal Display Period= [((REG[14h] bits 6-0) + 1) x 8] pixelsThe HDP must be a minimum of 32 pixels and can be increased by multiples of 8.*Panel Type Bits (REG[10h] bits 2-0) = 010 (Serial 8-bit TFT)*LLINE Pulse Polarity Bit (REG[24h] bit 7) = 0 (active low)*LFRAME Polarity Bit (REG[20h] bit 7) = 0 (active low)In horizontal display period, one cycle out of every four LSHIFT clock is off. In horizontal non-displayperiod, all LSHIFT clock cycles are on.So, Horizontal Total (REG[13h] bits 2-0, REG[12h] bits 7-0) = [(no of subpixel clock of horizontal total – noof subpixel clock of horizontal display period)/4 + (no of subpixel clock of horizontal display period)/3] - 1LLINE Pulse Start Position (REG[23h] bits 2-0, REG[22h] bits 7-0) = (no of subpixel clock of LLINE PulseStart Position)/4 - 1LLINE Pulse Width (REG[20h] bits 6-0) = (no of subpixel clock of LLINE Pulse Width)/4 – 1Horizontal Display Period Start Position (REG[17h] bits 2-0, REG[16h] bits 7-0) = (no of subpixel clock ofHorizontal Display Period Start Position)/4 - 1Horizontal Display Period (REG[14h] bits 6-0) = [(no of subpixel clock of horizontal display period)/3]/8 – 1The frequency of LSHIFT was different during display and non-display period.During horizontal display period:LSHIFT frequency = (¾) * MCLK frequency * (PCLK Frequency Ratio + 1) / (2 18 )During horizontal non-display period:LSHIFT frequency = MCLK frequency * (PCLK Frequency Ratio + 1) / (2 18 )<strong>Solomon</strong> <strong>Systech</strong> Jul 2009 P 26/27 Rev 1.0<strong>SSD1926</strong><strong>Application</strong> <strong>Note</strong>

Panel Type RegisterREG[10h]Bit 7 6 5 4 3 2 1 0Color STNPanelColor/MonoPanel DataWidth Bit 1Panel DataWidth Bit 0Reserved Panel TypeBit 2Panel TypeBit 1Panel TypeBit 0Select PanelSelectType RW RW RW RW RW RW RW RWResetstate0 0 0 0 0 0 0 0Bit 7Color STN Panel SelectWhen this bit = 0, non CSTN LCD panel is selected.When this bit = 1, CSTN LCD panel is selected.Bit 6Color/Mono Panel SelectWhen this bit = 0, monochrome LCD panel is selected.When this bit = 1, color LCD panel is selected.Bits 5-4 Panel Data Width Bits [1:0]These bits are determined by the data width of the LCD panel. Refer to Table 2-3: Panel DataWidth Selection for the selection.<strong>Note</strong> : These 2 bits are not effective for Serial TFT panel.Table 2-3: Panel Data Width SelectionPanel Data Width Bits [1:0] Passive Panel Data Width Active Panel Data Width(for TFT only)00 4-bit 9-bit01 8-bit 12-bit10 Reserved 18-bit11 Reserved 24-bitBit 3Reserved bitThis bit should be programmed by 0.Bits 2-0 Panel Type Bit [2:0]This bit selects the panel type.Table 2-4: LCD Panel Type SelectionPanel Type Bit[2:0] Panel Type000 STN001 TFT010 Serial-TFT011 Reserved100 Smart TFT101 Smart CSTN110 Smart OLED111 Reserved<strong>SSD1926</strong><strong>Application</strong> <strong>Note</strong>Rev 1.0 P 27/28 Jul 2009 <strong>Solomon</strong> <strong>Systech</strong>

MOD Rate RegisterREG[11h]Bit 7 6 5 4 3 2 1 00 0 MOD RateBit 5MOD RateBit 4MOD RateBit 3MOD RateBit 2MOD RateBit 1MOD RateBit 0Type RO RO RW RW RW RW RW RWResetstate0 0 0 0 0 0 0 0Bits 5-0 MOD Rate Bits [5:0]When these bits are all 0, the MOD output signal (LDEN) toggles every LFRAME.For any non-zero value n, the MOD output signal (LDEN) toggles every n LLINE.<strong>Note</strong>: These bits are for passive LCD panels and REG[340h] = 0 only.Horizontal Total Register 1REG[12h]Bit 7 6 5 4 3 2 1 0HorizontalTotal Bit 10HorizontalTotal Bit 9HorizontalTotal Bit 8HorizontalTotal Bit 7HorizontalTotal Bit 6HorizontalTotal Bit 5HorizontalTotal Bit 4HorizontalTotal Bit 3Type RW RW RW RW RW RW RW RWResetstate0 0 0 0 0 0 0 0Horizontal Total Register 0REG[13h]Bit 7 6 5 4 3 2 1 00 0 0 0 0 HorizontalTotal Bit 2HorizontalTotal Bit 1HorizontalTotal Bit 0Type RO RW RW RW RW RW RW RWResetstate0 0 0 0 0 1 1 1REG[12h], Bits 6-0REG[13h], Bits 2-0Horizontal Total Bits [10:0]This register is used for both dumb and smart panel interface.For dumb panel interface, these bits specify the LCD panel Horizontal Total period. TheHorizontal Total is the sum of the Horizontal Display period and the Horizontal Non-Displayperiod.The maximum Horizontal Total is 2048 pixels.Horizontal Total in number of pixels = REG[12h] Bits [7:0] x 8 + REG[13h] Bits [2:0] + 1<strong>Note</strong>(1)This register must be programmed such that the following condition is fulfilled.HDPS + HDP < HT(2)For panel AC timing and timing parameter definitions, see Section “Display Interface” indatasheet.(3)For smart panel interface (i.e. REG[10h] bit 2 = 1 and REG[250h] bit 5 = 1), REG[12h] willbe used as horizontal number of pixels and REG[13h] = 0x07.Horizontal width of smart panel = REG[12h] Bits[7:0] x 8 + 8<strong>Solomon</strong> <strong>Systech</strong> Jul 2009 P 28/29 Rev 1.0<strong>SSD1926</strong><strong>Application</strong> <strong>Note</strong>

Horizontal Display Period RegisterREG[14h]Bit 7 6 5 4 3 2 1 00 HorizontalDisplayPeriod Bit 6HorizontalDisplayPeriod Bit 5HorizontalDisplayPeriod Bit 4HorizontalDisplayPeriod Bit 3HorizontalDisplayPeriod Bit 2HorizontalDisplayPeriod Bit 1HorizontalDisplayPeriod Bit 0Type RO RW RW RW RW RW RW RWResetstate0 0 0 0 0 0 0 0Bit 7Reserved bitBits 6-0 Horizontal Display Period Bits [6:0]This register is used for both dumb and smart panel interface.For dumb panel interface, these bits specify the LCD panel Horizontal Display period, in 8pixel resolution. The Horizontal Display period should be less than the Horizontal Total toallow for a sufficient Horizontal Non-Display period.Horizontal Display Period in number of pixels = (Bits [6:0] + 1) x 8<strong>Note</strong>(1)Maximum value of REG[14h] ≤ 0x3F when Display Rotate Mode (90° or 270°) is selected.(2)For panel AC timing and timing parameter definitions, see Section “Display Interface” indatasheet.(3)For smart panel interface (i.e. REG[10h] bit 2 = 1 and REG[250h] bit 5 = 1), these bitsshould be set as same as REG[12h].Horizontal Display Period Start Position Register 0REG[16h]Bit 7 6 5 4 3 2 1 0HorizontalDisplayPeriod StartPosition Bit7HorizontalDisplayPeriod StartPosition Bit6HorizontalDisplayPeriod StartPosition Bit5HorizontalDisplayPeriod StartPosition Bit4HorizontalDisplayPeriod StartPosition Bit3HorizontalDisplayPeriod StartPosition Bit2HorizontalDisplayPeriod StartPosition Bit1HorizontalDisplayPeriod StartPosition Bit0Type RW RW RW RW RW RW RW RWResetstate0 0 0 0 0 0 0 0Horizontal Display Period Start Position Register 1REG[17h]Bit 7 6 5 4 3 2 1 00 0 0 0 0 HorizontalDisplayPeriod StartPosition Bit10HorizontalDisplayPeriod StartPosition Bit9HorizontalDisplayPeriod StartPosition Bit8Type RO RO RO RO RO RO RW RWResetstate0 0 0 0 0 0 0 0REG[17h] bits1-0,REG[16h] bits 7-0Horizontal Display Period Start Position Bits [10:0]These bits specify the Horizontal Display Period Start Position in 1 pixel resolution.<strong>Note</strong>(1)For panel AC timing and timing parameter definitions, see Section “Display Interface” indatasheet.(2)These bit can not be updated for smart panel interface (REG[250h] bit 5 = 1)<strong>SSD1926</strong><strong>Application</strong> <strong>Note</strong>Rev 1.0 P 29/30 Jul 2009 <strong>Solomon</strong> <strong>Systech</strong>

Vertical Total Register 0REG[18h]Bit 7 6 5 4 3 2 1 0VerticalTotal Bit 7VerticalTotal Bit 6VerticalTotal Bit 5VerticalTotal Bit 4VerticalTotal Bit 3VerticalTotal Bit 2VerticalTotal Bit 1VerticalTotal Bit 0Type RW RW RW RW RW RW RW RWResetstate0 0 0 0 0 0 0 0Vertical Total Register 1REG[19h]Bit 7 6 5 4 3 2 1 00 0 0 0 0 VerticalTotal Bit 10VerticalTotal Bit 9VerticalTotal Bit 8Type RO RO RO RO RO RW RW RWResetstate0 0 0 0 0 0 0 0REG[19h] bits 1-0,REG[18h] bits 7-0Vertical Total Bits [10:0]This register is used for both dumb and smart panel interface.For dumb panel interface, these bits specify the LCD panel Vertical Total period, in 1 lineresolution. The Vertical Total is the sum of the Vertical Display Period and the Vertical Non-Display Period.The maximum Vertical Total is 2048 lines. See “Display Interface” in datasheet.Vertical Total in number of lines = Bits [10:0]+ 1<strong>Note</strong>(1)This register must be programmed such that the following condition is fulfilled.VDPS + VDP < VT(2)For panel AC timing and timing parameter definitions, see Section “Display Interface”.(3)For smart panel interface (i.e. REG[10h] bit 2 = 1 and REG[250h] bit 5 = 1), these bits willbe used as vertical number of lines in smart panel.Vertical height of smart panel = REG[19h] 2:0, REG[18h] 7:0 + 1Vertical Display Period Register 0REG[1Ch]Bit 7 6 5 4 3 2 1 0VerticalDisplayPeriod Bit 7VerticalDisplayPeriod Bit 6VerticalDisplayPeriod Bit 5VerticalDisplayPeriod Bit 4VerticalDisplayPeriod Bit 3VerticalDisplayPeriod Bit 2VerticalDisplayPeriod Bit 1VerticalDisplayPeriod Bit 0Type RW RW RW RW RW RW RW RWResetstate0 0 0 0 0 0 0 0<strong>Solomon</strong> <strong>Systech</strong> Jul 2009 P 30/31 Rev 1.0<strong>SSD1926</strong><strong>Application</strong> <strong>Note</strong>

Vertical Display Period Register 1REG[1Dh]Bit 7 6 5 4 3 2 1 00 0 0 0 0 0 VerticalDisplayPeriod Bit 9VerticalDisplayPeriod Bit 8Type RO Ro RO RO RO RO RW RWResetstate0 0 0 0 0 0 0 0REG[1Dh] bits 1-0,REG[1Ch] bits 7-0Vertical Display Period Bits [9:0]This register is used for both main and smart panel interface.For dumb panel interface, these bits specify the LCD panel Vertical Display period, in 1 lineresolution. The Vertical Display period should be less than the Vertical Total to allow for asufficient Vertical Non-Display period.Vertical Display Period in number of lines = Bits [9:0] + 1<strong>Note</strong>(1)For panel AC timing and timing parameter definitions, see Section “Display Interface” indatasheet.(2)For smart panel interface (i.e. REG[10h] bit 2 = 1 and REG[250h] bit 5 = 1), these bitsshould be set as same as REG[19h-18h].Vertical Display Period Start Position Register 0REG[1Eh]Bit 7 6 5 4 3 2 1 0VerticalDisplayPeriod StartPosition Bit7VerticalDisplayPeriod StartPosition Bit6VerticalDisplayPeriod StartPosition Bit5VerticalDisplayPeriod StartPosition Bit4VerticalDisplayPeriod StartPosition Bit3VerticalDisplayPeriod StartPosition Bit2VerticalDisplayPeriod StartPosition Bit1VerticalDisplayPeriod StartPosition Bit0Type RW RW RW RW RW RW RW RWResetstate0 0 0 0 0 0 0 0Vertical Display Period Start Position Register 1REG[1Fh]Bit 7 6 5 4 3 2 1 00 0 0 0 0 VerticalDisplayStartPositionPeriod BitVerticalDisplayStartPositionPeriod Bit 9VerticalDisplayStartPositionPeriod Bit 810Type NA NA NA NA NA NA RW RWResetstate0 0 0 0 0 0 0 0REG[1Fh] bits 1-0,REG[1Eh] bits 7-0Vertical Display Period Start Position Bits [10:0]These bits specify the Vertical Display Period Start Position in 1 line resolution.<strong>Note</strong>For panel AC timing and timing parameter definitions, see Section “Display Interface” indatasheet.<strong>SSD1926</strong><strong>Application</strong> <strong>Note</strong>Rev 1.0 P 31/32 Jul 2009 <strong>Solomon</strong> <strong>Systech</strong>

LLINE Pulse Width RegisterREG[20h]Bit 7 6 5 4 3 2 1 0LLINEPulsePolarityLLINEPulseWidth Bit 6LLINEPulseWidth Bit 5LLINEPulseWidth Bit 4LLINEPulseWidth Bit 3LLINEPulseWidth Bit 2LLINEPulseWidth Bit 1LLINEPulseWidth Bit 0Type RW RW RW RW RW RW RW RWResetstate0 0 0 0 0 0 0 0Bit 7LLINE Pulse PolarityThis bit determines the polarity of the horizontal sync signal. The horizontal sync signal istypically named as LLINE or LP, depending on the panel type.When this bit = 0, the horizontal sync signal is active low.When this bit = 1, the horizontal sync signal is active high.<strong>Note</strong>(1)These bit can not be updated for smart panel interface (REG[250h] bit 5 = 1)Bits 6-0 LLINE Pulse Width Bits [6:0]These bits specify the width of the panel horizontal sync signal, in number of PCLK. Thehorizontal sync signal is typically named as LLINE or LP, depending on the panel type.LLINE Pulse Width in PCLK = Bits [6:0] + 1<strong>Note</strong>(1)These bit can not be updated for smart panel interface (REG[250h] bit 5 = 1)<strong>Note</strong>(1)For panel AC timing and timing parameter definitions, see Section “Display Interface” in datasheet.LLINE Pulse Start Sub-pixel Position RegisterREG[21h]Bit 7 6 5 4 3 2 1 00 0 0 0 0 0 Sub-pixelPosition Bit1Sub-pixelPosition Bit0Type RW RW RW RW RW RW RW RWResetstate0 0 0 0 0 0 0 0Bits 7-2Reserved bitsBits 1-0 Sub-pixel Position Bits [1:0]00 : No sub-pixel delay01 : 1 sub-pixel clock delay10 : 2 sub-pixel clock delay11 : 3 sub-pixel clock delay<strong>Note</strong>(1)This register is effective for Serial-TFT panel only.<strong>Solomon</strong> <strong>Systech</strong> Jul 2009 P 32/33 Rev 1.0<strong>SSD1926</strong><strong>Application</strong> <strong>Note</strong>

LLINE Pulse Start Position Register 0REG[22h]Bit 7 6 5 4 3 2 1 0LLINEPulse StartPosition Bit7LLINEPulse StartPosition Bit6LLINEPulse StartPosition Bit5LLINEPulse StartPosition Bit4LLINEPulse StartPosition Bit3LLINEPulse StartPosition Bit2LLINEPulse StartPosition Bit1LLINEPulse StartPosition Bit0Type RW RW RW RW RW RW RW RWResetstate0 0 0 0 0 0 0 0LLINE Pulse Start Position Register 1REG[23h]Bit 7 6 5 4 3 2 1 00 0 0 0 0 LLINEPulse StartPosition Bit10LLINEPulse StartPosition Bit9LLINEPulse StartPosition Bit8Type NA NA NA NA NA NA RW RWResetstate0 0 0 0 0 0 0 0REG[23h] bits 1-0,REG[22h] bits 7-0LLINE Pulse Start Position Bits [10:0]These bits specify the start position of the horizontal sync signal, in number of PCLK.LLINE Pulses Start Position in PCLK = Bits [10:0] + 1<strong>Note</strong>(1)These bit can not be updated for smart panel interface (REG[250h] bit 5 = 1)<strong>Note</strong>(1)For panel AC timing and timing parameter definitions, see Section “Display Interface” in datasheet”.LFRAME Pulse Width RegisterREG[24h]Bit 7 6 5 4 3 2 1 0LFRAMEPulsePolarity0 0 0 0 LFRAMEPulseWidth Bit 2LFRAMEPulseWidth Bit 1LFRAMEPulseWidth Bit 0Type RW NA NA NA NA RW RW RWResetstate0 0 0 0 0 0 0 0Bit 7LFRAME Pulse PolarityThis bit selects the polarity of the vertical sync signal. The vertical sync signal is typicallynamed as LFRAME or SPS, depending on the panel type.When this bit = 0, the vertical sync signal is active low.When this bit = 1, the vertical sync signal is active high.<strong>Note</strong>(1)These bit can not be updated for smart panel interface (REG[250h] bit 5 = 1)Bits 2-0 LFRAME Pulse Width Bits [2:0]These bits specify the width of the panel vertical sync signal, in 1 line resolution. The verticalsync signal is typically named as LFRAME or SPS, depending on the panel type.LFRAME Pulse Width in number of pixels = (Bits [2:0] + 1) x Horizontal Total + offset<strong>Note</strong>(1)These bit can not be updated for smart panel interface (REG[250h] bit 5 = 1)<strong>Note</strong>(1)For panel AC timing and timing parameter definitions, see Section “Display Interface” in datasheet.<strong>SSD1926</strong><strong>Application</strong> <strong>Note</strong>Rev 1.0 P 33/34 Jul 2009 <strong>Solomon</strong> <strong>Systech</strong>

LFRAME Pulse Start Position Register 0REG[26h]Bit 7 6 5 4 3 2 1 0LFRAMEPulse StartPosition Bit7LFRAMEPulse StartPosition Bit6LFRAMEPulse StartPosition Bit5LFRAMEPulse StartPosition Bit4LFRAMEPulse StartPosition Bit3LFRAMEPulse StartPosition Bit2LFRAMEPulse StartPosition Bit1LFRAMEPulse StartPosition Bit0Type RW RW RW RW RW RW RW RWResetstate0 0 0 0 0 0 0 0LFRAME Pulse Start Position register 1REG[27h]Bit 7 6 5 4 3 2 1 00 0 0 0 0 LFRAMEPulse StartPosition Bit10LFRAMEPulse StartPosition Bit9LFRAMEPulse StartPosition Bit8Type NA NA NA NA NA NA RW RWResetstate0 0 0 0 0 0 0 0REG[27h] bits 1-0REG[26h] bits 7-0LFRAME Pulse Start Position Bits [10:0]These bits specify the start position of the vertical sync signal, in 1 line resolution.LFRAME Pulse Start Position in number of pixels = (Bits [10:0]) x Horizontal Total + offset<strong>Note</strong>(1)These bit can not be updated for smart panel interface (REG[250h] bit 5 = 1)<strong>Note</strong>(1)For panel AC timing and timing parameter definitions, see Section “Display Interface” in datasheet.Display Post-processing Saturation Control RegisterREG[2Ch]Bit 7 6 5 4 3 2 1 0DisplayPost-procSaturationBit 7DisplayPost-procSaturationBit 6DisplayPost-procSaturationBit 5DisplayPost-procSaturationBit 4DisplayPost-procSaturationBit 3DisplayPost-procSaturationBit 2DisplayPost-procSaturationBit 1DisplayPost-procSaturationBit 0Type NA NA NA NA NA NA RW RWResetstate0 1 0 0 0 0 0 0Bits 7-0 Display Post-processing Saturation Control [7:0]These bits control the saturation of the display.Table 2-5: The setting for display post-processing saturationControl Bits [7:0] Saturation Control0x00 Gain = 00x01 Gain = 1/64…0x40 (Default) Gain = 1…0x7F Gain = 127/64<strong>Solomon</strong> <strong>Systech</strong> Jul 2009 P 34/35 Rev 1.0<strong>SSD1926</strong><strong>Application</strong> <strong>Note</strong>

Display Post-processing Brightness Control RegisterREG[2Dh]Bit 7 6 5 4 3 2 1 0DisplayPost-procBrightnessBit 7DisplayPost-procBrightnessBit 6DisplayPost-procBrightnessBit 5DisplayPost-procBrightnessBit 4DisplayPost-procBrightnessBit 3DisplayPost-procBrightnessBit 2DisplayPost-procBrightnessBit 1DisplayPost-procBrightnessBit 0Type NA NA NA NA NA NA RW RWResetstate1 0 0 0 0 0 0 0Bits 7-0 Display Post-processing Brightness Control [7:0]These bits control the brightness of the display.Table 2-6: The setting for Display Post-processing brightnessControl Bits [7:0] Brightness Control0x00 Value = 0…0x80 (Default) Value = 128…0xFF Value = 255Display Post-processing Contrast Control RegisterREG[2Eh]Bit 7 6 5 4 3 2 1 0DisplayPost-procContrast Bit7DisplayPost-procContrast Bit6DisplayPost-procContrast Bit5DisplayPost-procContrast Bit4DisplayPost-procContrast Bit3DisplayPost-procContrast Bit2DisplayPost-procContrast Bit1DisplayPost-procContrast Bit0Type NA NA NA NA NA NA RW RWResetstate0 1 0 0 0 0 0 0Bits 7-0 Display Post-processing Contrast Control [7:0]These bits control the contrast of the display.Table 2-7: The setting for Display Post-processing contrastControl Bits [7:0] Contrast Control0x00 Gain = 00x01 Gain = 1/64…0x40 (Default) Gain = 1…0x7F Gain = 127/64<strong>SSD1926</strong><strong>Application</strong> <strong>Note</strong>Rev 1.0 P 35/36 Jul 2009 <strong>Solomon</strong> <strong>Systech</strong>

Display Post-processing Control RegisterREG[2Fh]Bit 7 6 5 4 3 2 1 00 0 0 0 0 0 0 DisplayPost-procEnableType RW RW RW RW RW RW RW RWResetstate0 0 0 0 0 0 0 0Bits 7-1Bit 0Reserved bitsThese bits should be programmed by 0.Display Post-processing EnableWhen this bit = 1, display post-processing is enabled.When this bit = 0, display post-processing is disabled.LFRAME Pulse Start Offset Register 0REG[30h]Bit 7 6 5 4 3 2 1 0LFRAMEStart OffsetBit 7LFRAMEStart OffsetBit 6LFRAMEStart OffsetBit 5LFRAMEStart OffsetBit 4LFRAMEStart OffsetBit 3LFRAMEStart OffsetBit 2LFRAMEStart OffsetBit 1LFRAMEStart OffsetBit 0Type RW RW RW RW RW RW RW RWResetstate0 0 0 0 0 0 0 0LFRAME Pulse Start Offset Register 1REG[31h]Bit 7 6 5 4 3 2 1 00 0 0 0 0 LFRAMEStart OffsetBit 10LFRAMEStart OffsetBit 9LFRAMEStart OffsetBit 8Type NA NA NA NA NA NA RW RWResetstate0 0 0 0 0 0 0 0REG[31h] bits 2-0REG[30h] bits 7-0LFRAME Pulse Start Offset [10:0]These bits specify the start offset of the vertical sync signal within a line, in 1 pixel resolution.<strong>Note</strong>(1)For panel AC timing and timing parameter definitions, see Section “Display Interface” in datasheet.LFRAME Pulse Stop Offset Register 0REG[34h]Bit 7 6 5 4 3 2 1 0LFRAMEStop OffsetBit 7LFRAMEStop OffsetBit 6LFRAMEStop OffsetBit 5LFRAMEStop OffsetBit 4LFRAMEStop OffsetBit 3LFRAMEStop OffsetBit 2LFRAMEStop OffsetBit 1LFRAMEStop OffsetBit 0Type RW RW RW RW RW RW RW RWResetstate0 0 0 0 0 0 0 0<strong>Solomon</strong> <strong>Systech</strong> Jul 2009 P 36/37 Rev 1.0<strong>SSD1926</strong><strong>Application</strong> <strong>Note</strong>

LFRAME Pulse Stop Offset Register 1REG[35h]Bit 7 6 5 4 3 2 1 00 0 0 0 0 LFRAMEStop OffsetBit 10LFRAMEStop OffsetBit 9LFRAMEStop OffsetBit 8Type NA NA NA NA NA NA RW RWResetstate0 0 0 0 0 0 0 0REG[35h] bits 2-0REG[34h] bits 7-0LFRAME Pulse Stop Offset [10:0]These bits specify the stop offset of the vertical sync signal within a line, in 1 pixel resolution.<strong>Note</strong>(1)For panel AC timing and timing parameter definitions, see Section “Display Interface” in datasheet.LSHIFT Polarity RegisterREG[38h]Bit 7 6 5 4 3 2 1 00 0 0 0 0 0 0 LSHIFTPolarityswapType RW RW RW RW RW RW RW RWResetstate0 0 0 0 0 0 0 0Bits 7-1Reserved bitsThese bits should be programmed by 0.Bit 0LSHIFT Polarity SwapWhen this bit = 1, LSHIFT signal is falling trigger.When this bit = 0, LSHIFT signal is rising trigger.<strong>Note</strong>(1)Bit 0 is effective for TFT panels only (REG[10h] bit 0 = 1).RGB sequence RegisterREG[42h]Bit 7 6 5 4 3 2 1 00 0 Even lineRGBsequence Bit2Even lineRGBsequence Bit1Even lineRGBsequence Bit0Odd lineRGBsequence Bit2Odd lineRGBsequence Bit1Odd lineRGBsequence Bit0Type RW RW RW RW RW RW RW RWResetstate0 0 0 0 0 0 0 0Bits 7-6Reserved bitsBits 5-3 Even line RGB sequence Bits [2:0]Bits 2-0 Odd line RGB sequence Bits [2:0]The first display line is the odd line.<strong>Note</strong>This register is effective for Serial-TFT panel only. The first line is the even line.Table 2-8: The RGB sequence for Serial-TFT interfaceRGB sequence bits [2:0] RGB output sequence000 RGB001 RBG010 GRB011 GBR100 BRG101 BGR11xReserved<strong>SSD1926</strong><strong>Application</strong> <strong>Note</strong>Rev 1.0 P 37/38 Jul 2009 <strong>Solomon</strong> <strong>Systech</strong>

MOD Time Period Register 0REG[340h]Bit 7 6 5 4 3 2 1 00 0 0 0 MOD TimePeriodBit 3MOD TimePeriodBit 2MOD TimePeriodBit 1MOD TimePeriodBit 0Type RO RO RO RO RW RW RW RWReset 0 0 0 0 0 0 0 0stateREG[340h] bits 3-0 MOD Period position Register [3:0]This register define the period of MOD output signal, in terms of display line.0 : Disable and MOD output will follow the setting of REG[11h]n : MOD polarity will repeat every n frames with the patterns defined in REG[342-343h]. Thesetting of REG[11h] will be ignored.<strong>Note</strong>: These bits are for passive LCD panels only.MOD Time Pattern Register 0REG[342h]Bit 7 6 5 4 3 2 1 0MOD TimePatternBit 7MOD TimePatternBit 6MOD TimePatternBit 5MOD TimePatternBit 4MOD TimePatternBit 3MOD TimePatternBit 2MOD TimePatternBit 1MOD TimePatternBit 0Type RW RW RW RW RW RW RW RWReset 0 0 0 0 0 0 0 0stateMOD Time Pattern Register 1REG[343h]Bit 7 6 5 4 3 2 1 0MOD TimePatternBit 15MOD TimePatternBit 14MOD TimePatternBit 13MOD TimePatternBit 12MOD TimePatternBit 11MOD TimePatternBit 10MOD TimePatternBit 9MOD TimePatternBit 8Type RW RW RW RW RW RW RW RWReset 0 0 0 0 0 0 0 0stateREG[343h] bits 7-0,REG[342h] bits 7-0MOD Time pattern register [15:0]This register defines MOD pattern.1 : Positive polarity0 : Negative polarityFor example,REG[340h] = 0x4REG[343-342h] = 0x0001 (i.e. b0001)Then the frame #1 is positive polarity, frame #2-4 are negative polarity. And such pattern willbe repeated for every 4 frames.<strong>Note</strong>(1)These bits are for passive LCD panels only.<strong>Solomon</strong> <strong>Systech</strong> Jul 2009 P 38/39 Rev 1.0<strong>SSD1926</strong><strong>Application</strong> <strong>Note</strong>

LSHIFT signal start position Register 0REG[350h]Bit 7 6 5 4 3 2 1 0LSHIFTstartBit 7LSHIFTstartBit 6LSHIFTstartBit 5LSHIFTstartBit 4LSHIFTstartBit 3LSHIFTstartBit 2LSHIFTstartBit 1LSHIFTstartBit 0Type RW RW RW RW RW RW RW RWReset 0 0 0 0 0 0 0 0stateLSHIFT signal start position Register1REG[351h]Bit 7 6 5 4 3 2 1 0Reserved Reserved Reserved Reserved Reserved LSHIFTstartBit 10LSHIFTstartBit 9LSHIFTstartBit 8Type RO RO RO RO RO RO RW RWReset 0 0 0 0 0 0 0 0stateLSHIFT signal end position Register 0REG[354h]Bit 7 6 5 4 3 2 1 0LCD shiftendBit 7LCD shiftendBit 6LCD shiftendBit 5LCD shiftendBit 4LCD shiftendBit 3LCD shiftendBit 2LCD shiftendBit 1LCD shiftendBit 0Type RW RW RW RW RW RW RW RWReset 0 0 0 0 0 0 0 0stateLSHIFT signal end position Register1REG[355h]Bit 7 6 5 4 3 2 1 0Reserved Reserved Reserved Reserved Reserved LCD shiftendBit 10LCD shiftendBit 9LCD shiftendBit 8Type RO RO RO RO RO RO RW RWReset 0 0 0 0 0 0 0 0stateREG[351h] bits 1-0,REG[350h] bits 7-0REG[355h] bits 1-0,REG[354h] bits 7-0LSHIFT signal start position Register [10:0]These bits define the start position of LSHIFT within a line for active lcd signal.LSHIFT signal end position Register [10:0]These bit defines the end position of LSHIFT within a line for active lcd signal.If REG[351-350h] and REG[355-354h] are 0, LSHIFT will be enabled on the time (i.e. bothdisplay and non-display period).If REG[351-350h] and REG[355-354h] are not equal to 0, LSHIFT will be enabled within therange defined by start and end position within each line.The end position > The start positionFor example,Horizontal display period = 16Horizontal total = 24Horizontal period start = 4LSHIFT start = 3 and LSHIFT end = 20Then the LSHIFT will enabled between horizontal position pixel 3 and 20 within a line.<strong>SSD1926</strong><strong>Application</strong> <strong>Note</strong>Rev 1.0 P 39/40 Jul 2009 <strong>Solomon</strong> <strong>Systech</strong>

2.6 Smart Panel Configuration RegistersTo operate with smart panel module, first is to enable the smart display (REG[250h] bit 5 = 1), then select theoperation mode (Write Through or Auto Reflesh Mode), panel type and panel interface (REG[260h] ®[10h]). The maximum resolution for main smart panel is 2048 x 2048.Then next step is to configure the type of data to be transferred for Write Through Mode. Detail will becovered in section 2.6.1.Data transfer is initiated by writing data to REG[26Ch] and REG[26Dh] for Write Through Mode while bysetting REG[A0h] to enable the Auto Reflesh Mode of smart panel interface.2.6.1 Write Through ModeThere are three types of data for Write Through Mode:- Display pixel data- Command- Command argumentWrite Through Mode will send either pixel display data or command or command argument to the paneldriver at each time by issuing an enable pulse together with the 16-bit data or command.Table 2-9: Data type for parallel interface of all panel typesData TypeData / Command SelectionREG[26Eh] Bit 0Data / ArgumentSelectionREG[26Eh] Bit 7Command 0 xCommand Argument 1 0Pixel Data 1 12.6.1.1 Input FormatMCU data for Write Through mode are stored in REG[26Ch-26Dh]. Input data format from MCU in WriteThrough Mode as Table 2-10: Input data format for Write Through Mode.Table 2-10: Input data format for Write Through ModeInput Data Type Smart Display Input Data [15:0](REG[26Dh-26Ch])Command/Argument (8 bit)XXXXXXXXDDDDDDDDPixel Data (16bpp)RRRRRGGGGGGBBBBB2.6.1.2 Output FormatConsidering parallel output interface, only TFT will support 8-bit and 9-bit interface while CSTN and OLEDwill only have 8-bit interface (LCD_DATA8 will be 0). Refer to Table 2-11 for output data format of differentpanel interface.<strong>Solomon</strong> <strong>Systech</strong> Jul 2009 P 40/41 Rev 1.0<strong>SSD1926</strong><strong>Application</strong> <strong>Note</strong>

Panel TypeTFTCSTNOLEDTable 2-11: Data output format for display pixel in Parallel interfaceParallel InterfaceWidthREG[260h] Bit 5Byte per pixelREG[261h] Bits 1-0Pixel DataDescription0 xx 2 transfersper pixel(18bpp)1 10 2 transfersperpixel(16bpp)1 11 3 transfersper pixel(18bpp)x 00 1 transfer perpixel (8bpp)x 01 3 transfersper 2 pixels(12bpp)x 10 2 transfersper pixel(16bpp)x 11 3 transfersper pixel(18bpp)x 00 1 transfer perpixel (8bpp)x 01 3 transfersper 2 pixels(12bpp)x 10 2 transfersper pixel(16bpp)x 11 3 transfersper pixel(18bpp)Parallel Pixel DataFormat(LCD_DATA[8:0])RRRRRRGGGGGGBBBBBBRRRRRGGG0GGGBBBBB0RRRRRR000GGGGGG000BBBBBB0000RRRGGGBB0RRRRGGGG0BBBBRRRR0GGGGBBBB0RRRRRGGG0GGGBBBBB0RRRRRR000GGGGGG000BBBBBB000RRRGGGBB0RRRRGGGG0BBBBRRRR0GGGGBBBB0RRRRRGGG0GGGBBBBB000RRRRRR000GGGGGG000BBBBBBPanelTypeTFT/CSTNOLEDTable 2-12: Data output format for 4-wire serial interface (REG[260h] Bit 6= 1)Output Data Type Byte per pixel Data Length Serial Output Format (SDA)REG[261h] Bits 1-0 per burstCommand/Argument xx 8 bit DDDDDDDDPixel (8bpp) 00 8 bit RRRGGGBBPixel (12bpp) 01 8 bit, 16 bit RRRRGGGG, BBBBRRRRGGGGBBBBPixel (16bpp) 10 16 bit RRRRRGGGGGGBBBBBPixel (18bpp) 11 24 bit RRRRRR00GGGGGG00BBBBBB00Command/Argument xx 8 bit DDDDDDDDPixel (8bpp) 00 8 bit RRRGGGBBPixel (12bpp) 01 8 bit, 16 bit RRRRGGGG BBBBRRRRGGGGBBBBPixel (16bpp) 10 16 bit RRRRRGGGGGGBBBBBPixel (18bpp) 11 24 bit 00RRRRRR00GGGGGG00BBBBBB<strong>SSD1926</strong><strong>Application</strong> <strong>Note</strong>Rev 1.0 P 41/42 Jul 2009 <strong>Solomon</strong> <strong>Systech</strong>

Panel TypeTFT/CSTNOLEDTable 2-13: Data output format for 3-wire serial interface (REG[260h] Bit 6= 0)Output Data Byte per pixel Data Length Serial Output Format (SDA)TypeREG[261h] Bits 1-0 per burstCommand xx 9 bit 0DDDDDDDDArgument xx 9 bit 1DDDDDDDDPixel (8bpp) 00 9 bit 1RRRGGGBBPixel (12bpp) 01 9 bit, 18 bit 1RRRRGGGG, 1BBBBRRRR1GGGGBBBBPixel (16bpp) 10 18 bit 1RRRRRGGG1GGGBBBBBPixel (18bpp) 11 27 bit 1RRRRRR001GGGGGG001BBBBBB00Command xx 9 bit 0DDDDDDDDArgument xx 9 bit 1DDDDDDDDPixel (8bpp) 00 9 bit 1RRRGGGBBPixel (12bpp) 01 9 bit, 18 bit 1RRRRGGGG 1BBBBRRRR1GGGGBBBBPixel (16bpp) 10 18 bit 1RRRRRGGG1GGGBBBBBPixel (18bpp) 11 27 bit 100RRRRRR100GGGGGG100BBBBBB2.6.1.3 Auto Refresh ModeAuto Refresh Mode will accept 32-bit (32 bits per pixel or 16 bits per pixel) display data from displaymemory and transfer them to panel driver continuously.There is only display pixel data transfer (no command or argument transfer) for Auto Refresh Mode. So thereis no need to configure the data type.Before transfer the pixel data to smart panel, it should configure the panel parameter with REG[12h] -REG[13h], REG[18h]- REG[19h], REG[74h]- REG[76h], REG[78h]- REG[79h].The data input is set according to the format below in memory:Table 2-14: Data input format for Auto Refresh ModeBit per pixelData [31:0]REG[70h] Bits 2:0100 (16 bit per pixel) RRRRRGGGGGGBBBBBRRRRRGGGGGGBBBBB (2 pixels)101 (32 bit per pixel) RRRRRRRRGGGGGGGGBBBBBBBBXXXXXXXX (1 pixel)The output data format is as same as the output pixel data format in Write Through Mode.2.6.1.4 Output Interface TimingTable 2-15: Output Timing for 6800 Parallel interfaceSymbol Parameter Min Typ Max Unitt cycle Clock Cycle Time (write cycle) (note2) 2 - 36 Ts (note1)t CSL Chip Select Low Width (note3) 1 - 16 Tst CSH Chip Select High Width (note4) 3 - 20 Tst AS Address Setup Time - 1 - Tst AH Address Hold Time - 1 - Tst DS Data Setup Time (note5) 1 - 16 Tst DH Data Hold Time (note6) 3 - 20 Ts<strong>Solomon</strong> <strong>Systech</strong> Jul 2009 P 42/43 Rev 1.0<strong>SSD1926</strong><strong>Application</strong> <strong>Note</strong>

D / Ct ASt AHR / WCSt cycleEt CSLt CSHD 0 ~D 8t DSWValid Datat DHWFigure 2-16: 6800 Timing Diagram<strong>Note</strong>(1)Ts = 1/(MCLK frequency / 2 (REG[252h] bit 2-0) )(2)t cycle = t CSL + t CSH(3)t CSL = REG [270h] bit 3-0 + 1(4)t CSH = REG [271h] bit 3-0 + 1 + t during a burst ort CSH = REG [271h] bit 3-0 + 1 + t*2 at the end of the burst, t = 2(5)t DSW = t CSL(6)t DHW = t CSHTable 2-16: Output Timing for 8080 Parallel interfaceSymbol Parameter Min Typ Max Unitt cycle Clock Cycle Time (write cycle) (note2) 2 - 36 Ts (note1)t CSL Control Pulse Low Width (note3) 1 - 16 Tst CSH Control Pulse High Width (note4) 3 - 20 Tst AS Address Setup Time - 1 - Tst AH Address Hold Time - 1 - Tst DSW Data Setup Time (note5) 1 - 16 Tst DHW Data Hold Time (note6) 3 - 20 Ts<strong>SSD1926</strong><strong>Application</strong> <strong>Note</strong>Rev 1.0 P 43/44 Jul 2009 <strong>Solomon</strong> <strong>Systech</strong>

D / Ct ASt AHCSWRt CSLt cyclt CSHRDt DSWt DHWD 0 ~D 8Valid DataFigure 2-17: 8080 Timing Diagram<strong>Note</strong>(1)Ts = 1/(MCLK frequency / 2 (REG[252h] bit 2-0) )(2)t cycle = t CSL + t CSH(3)t CSL = REG [270h] bit 3-0 + 1(4)t CSH = REG [271h] bit 3-0 + 1 + t during a burst ort CSH = REG [271h] bit 3-0 + 1 + t*2 at the end of the burst, t = 2(5)t DSW = t CSL(6)t DHW = t CSHTable 2-17: Output Timing for Serial interfaceSymbol Parameter Min Typ Max Unitt cycle Clock Cycle Time (write cycle) (note2) 2 - 32 Ts (note1)t CLKL SCK Low Width (note3) 1 - 16 Tst CLKH SCK High Width (note4) 1 - 16 Tst CSS Chip Select Setup Time (note5) 2 - 17 Tst CSH Chip Select Hold Time (note6) 2 - 17 Tst DSW Data Setup Time (note7) 1 - 16 Tst DHW Data Hold Time (note8) 1 - 16 Ts<strong>Solomon</strong> <strong>Systech</strong> Jul 2009 P 44/45 Rev 1.0<strong>SSD1926</strong><strong>Application</strong> <strong>Note</strong>

D / CCSt CSSt CSHt cycleSCK (D 6)t CLKLt CLKHSDA(D 7)t DSWValid Datat DHWFigure 2-18: 4 Wires Timing DiagramCSt CSSt cycleSCK (D 6)t CLKLt CLKHt DHWSDA(D 7)t DSWD/CValid DataFigure 2-19: 3 Wires Timing Diagram<strong>Note</strong>(1)Ts = 1/(MCLK frequency / 2 (REG[252h] bit 2-0) )(2)t cycle = t CLKL + t CLKH(3)t CLKL = REG [263h] bit 3-0 + 1(4)t CLKH = REG [263h] bit 3-0 + 1(5)t CSS = REG [270h] bit 3-0 + 2(6)t CSH = REG [271h] bit 3-0 + 2(7)t DSW = t CLKL(8)t DHW = t CLKH<strong>SSD1926</strong><strong>Application</strong> <strong>Note</strong>Rev 1.0 P 45/46 Jul 2009 <strong>Solomon</strong> <strong>Systech</strong>

Table 2-18: Register for smart panel interfaceRegister DescriptionSmart DisplayDisplay reset250h[7]Display EnableA0h[0]Smart Select Enable250h[5]Display mode [1] (YUV/RGB)1A4h[7:6]Display mode [0] (32/16 bpp) 70h[2:0] (1)Divide input clock source Ration [2:0]252h[2:0]Display horizontal panel size [7:0]13h[2:0] -12h[7:0]Display vertical panel size [7:0]19h[2:0] -18h[7:0]Display Operation Mode Selection260h[7]Serial Input Interface Width260h[6]Parallel Input Interface Width260h[5]Parallel/Serial Output Interface Selection [1:0]260h[3:2]Panel Type Selection [1:0] 10h[2:0] (2)Byte per pixel Bit [1:0]261h[1:0]Serial Clock divide ratio [3:0]263h[3:0]Hold count1 Bit [3:0]270h[3:0]Hold count2 Bit [3:0]271h[3:0]Display CSC Mode1A8h[7]Display Y Offset Registers [7:0]1A9h[7:0]Display CB Offset Registers [7:0]1AAh[7:0]Display CR Offset Registers [7:0]1ABh[7:0]Display Write Through Mode input data bit [15:8]26Ch[7:0]Display Write Through Mode input data bit [7:0]26Dh[7:0]Pixel data/Argument Selection26Eh[7]Data/Command Selection26Eh[0]Window Display Start Address Bit [7:0]74h[7:0]Window Display Start Address Bit [15:8]75h[7:0]Window Display Start Address Bit [16]76h[0]Window Line Address Offset Bit [7:0]78h[7:0]Window Line Address Offset Bit [9:8]79h[1:0]Display ready27Dh[0]<strong>Note</strong>(1)For Smart panel interface, 1/2/4/8/16/32 bit per pixel will be supported, 1/2/4/8 bpp will use lookup table.(2)REG[10h] bit 2 should be set to 1 to enable Smart panel interface.Smart Display Mode RegisterREG[250h]Bit 7 6 5 4 3 2 1 0Smart Reserved Smart Reserved Reserved Reserved Reserved ReservedDisplayresetSelectEnableType RW RW RW RO RO RO RW RWResetstate0 0 0 0 0 0 0 0REG [250h] Bit 7Smart Display Reset1 : Reset0 : Normal0 -> 1 : transmission stop immediately1 -> 0 : start transmission from beginning of display frameThis bit should be set to 0 before smart panel command send.<strong>Solomon</strong> <strong>Systech</strong> Jul 2009 P 46/47 Rev 1.0<strong>SSD1926</strong><strong>Application</strong> <strong>Note</strong>