Volume 3: General-Purpose and System Instructions - Stanford ...

Volume 3: General-Purpose and System Instructions - Stanford ... Volume 3: General-Purpose and System Instructions - Stanford ...

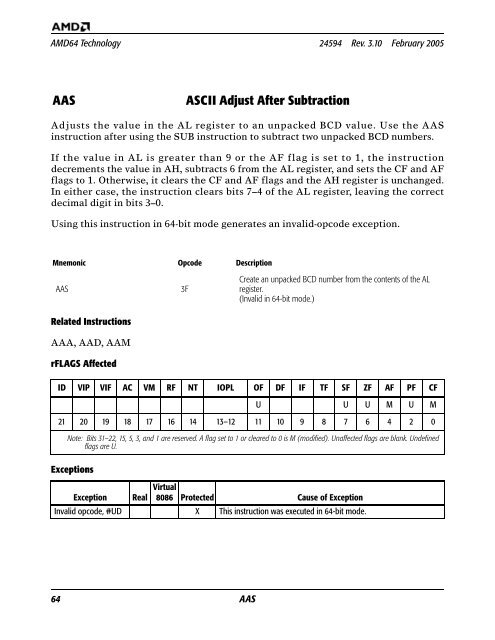

AMD64 Technology 24594 Rev. 3.10 February 2005AASASCII Adjust After SubtractionAdjusts the value in the AL register to an unpacked BCD value. Use the AASinstruction after using the SUB instruction to subtract two unpacked BCD numbers.If the value in AL is greater than 9 or the AF flag is set to 1, the instructiondecrements the value in AH, subtracts 6 from the AL register, and sets the CF and AFflags to 1. Otherwise, it clears the CF and AF flags and the AH register is unchanged.In either case, the instruction clears bits 7–4 of the AL register, leaving the correctdecimal digit in bits 3–0.Using this instruction in 64-bit mode generates an invalid-opcode exception.Mnemonic Opcode DescriptionAASRelated InstructionsAAA, AAD, AAMrFLAGS Affected3FCreate an unpacked BCD number from the contents of the ALregister.(Invalid in 64-bit mode.)ID VIP VIF AC VM RF NT IOPL OF DF IF TF SF ZF AF PF CFExceptionsU U U M U M21 20 19 18 17 16 14 13–12 11 10 9 8 7 6 4 2 0Note: Bits 31–22, 15, 5, 3, and 1 are reserved. A flag set to 1 or cleared to 0 is M (modified). Unaffected flags are blank. Undefinedflags are U.VirtualException Real 8086 Protected Cause of ExceptionInvalid opcode, #UD X This instruction was executed in 64-bit mode.64 AAS

24594 Rev. 3.10 February 2005 AMD64 TechnologyADCAdd with CarryAdds the carry flag (CF), the value in a register or memory location (first operand),and an immediate value or the value in a register a memory location (secondoperand), and stores the result in the first operand location. The instruction cannotadd two memory operands. The CF flag indicates a pending carry from a previousaddition operation. The instruction sign-extends an immediate value to the length ofthe destination register or memory location.This instruction evaluates the result for both signed and unsigned data types and setsthe OF and CF flags to indicate a carry in a signed or unsigned result, respectively. Itsets the SF flag to indicate the sign of a signed result.Use the ADC instruction after an ADD instruction as part of a multibyte or multiwordaddition.The forms of the ADC instruction that write to memory support the LOCK prefix. Fordetails about the LOCK prefix, see “Lock Prefix” on page 10.Mnemonic Opcode DescriptionADC AL, imm8 14 ib Add imm8 to AL + CF.ADC AX, imm16 15 iw Add imm16 to AX + CF.ADC EAX, imm32 15 id Add imm32 to EAX + CF.ADC RAX, imm32 15 id Add sign-extended imm32 to RAX + CF.ADC reg/mem8, imm8 80 /2 ib Add imm8 to reg/mem8 + CF.ADC reg/mem16, imm16 81 /2 iw Add imm16 to reg/mem16 + CF.ADC reg/mem32, imm32 81 /2 id Add imm32 to reg/mem32 + CF.ADC reg/mem64, imm32 81 /2 id Add sign-extended imm32 to reg/mem64 + CF.ADC reg/mem16, imm8 83 /2 ib Add sign-extended imm8 to reg/mem16 + CF.ADC reg/mem32, imm8 83 /2 ib Add sign-extended imm8 to reg/mem32 + CF.ADC reg/mem64, imm8 83 /2 ib Add sign-extended imm8 to reg/mem64 + CF.ADC reg/mem8, reg8 10 /r Add reg8 to reg/mem8 + CFADC reg/mem16, reg16 11 /r Add reg16 to reg/mem16 + CF.ADC reg/mem32, reg32 11 /r Add reg32 to reg/mem32 + CF.ADC 65

- Page 44 and 45: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 46 and 47: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 48 and 49: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 50 and 51: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 52 and 53: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 54 and 55: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 56 and 57: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 58 and 59: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 60 and 61: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 62 and 63: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 64 and 65: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 66 and 67: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 68 and 69: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 70 and 71: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 72 and 73: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 74 and 75: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 76 and 77: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 78 and 79: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 80 and 81: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 82 and 83: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 84 and 85: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 86 and 87: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 88 and 89: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 90 and 91: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 92 and 93: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 96 and 97: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 98 and 99: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 100 and 101: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 102 and 103: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 104 and 105: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 106 and 107: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 108 and 109: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 110 and 111: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 112 and 113: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 114 and 115: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 116 and 117: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 118 and 119: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 120 and 121: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 122 and 123: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 124 and 125: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 126 and 127: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 128 and 129: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 130 and 131: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 132 and 133: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 134 and 135: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 136 and 137: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 138 and 139: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 140 and 141: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 142 and 143: AMD64 Technology 24594 Rev. 3.10 Fe

AMD64 Technology 24594 Rev. 3.10 February 2005AASASCII Adjust After SubtractionAdjusts the value in the AL register to an unpacked BCD value. Use the AASinstruction after using the SUB instruction to subtract two unpacked BCD numbers.If the value in AL is greater than 9 or the AF flag is set to 1, the instructiondecrements the value in AH, subtracts 6 from the AL register, <strong>and</strong> sets the CF <strong>and</strong> AFflags to 1. Otherwise, it clears the CF <strong>and</strong> AF flags <strong>and</strong> the AH register is unchanged.In either case, the instruction clears bits 7–4 of the AL register, leaving the correctdecimal digit in bits 3–0.Using this instruction in 64-bit mode generates an invalid-opcode exception.Mnemonic Opcode DescriptionAASRelated <strong>Instructions</strong>AAA, AAD, AAMrFLAGS Affected3FCreate an unpacked BCD number from the contents of the ALregister.(Invalid in 64-bit mode.)ID VIP VIF AC VM RF NT IOPL OF DF IF TF SF ZF AF PF CFExceptionsU U U M U M21 20 19 18 17 16 14 13–12 11 10 9 8 7 6 4 2 0Note: Bits 31–22, 15, 5, 3, <strong>and</strong> 1 are reserved. A flag set to 1 or cleared to 0 is M (modified). Unaffected flags are blank. Undefinedflags are U.VirtualException Real 8086 Protected Cause of ExceptionInvalid opcode, #UD X This instruction was executed in 64-bit mode.64 AAS