Volume 3: General-Purpose and System Instructions - Stanford ...

Volume 3: General-Purpose and System Instructions - Stanford ... Volume 3: General-Purpose and System Instructions - Stanford ...

AMD64 Technology 24594 Rev. 3.10 February 2005492 Appendix D: Instruction Subsets and CPUID Feature Sets

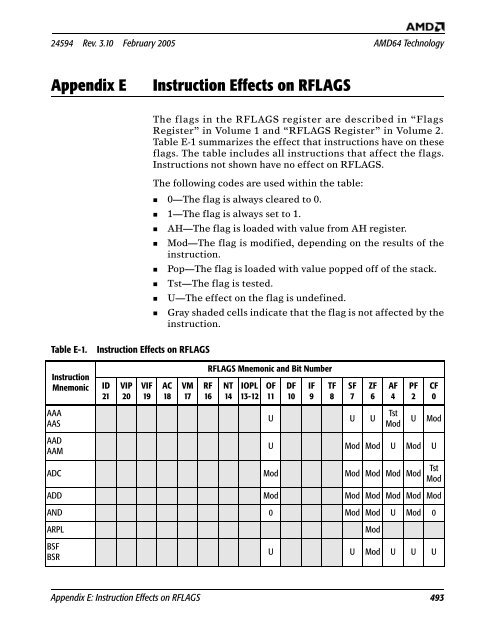

24594 Rev. 3.10 February 2005 AMD64 TechnologyAppendix EInstruction Effects on RFLAGSThe flags in the RFLAGS register are described in “FlagsRegister” in Volume 1 and “RFLAGS Register” in Volume 2.Table E-1 summarizes the effect that instructions have on theseflags. The table includes all instructions that affect the flags.Instructions not shown have no effect on RFLAGS.The following codes are used within the table:• 0—The flag is always cleared to 0.• 1—The flag is always set to 1.• AH—The flag is loaded with value from AH register.• Mod—The flag is modified, depending on the results of theinstruction.• Pop—The flag is loaded with value popped off of the stack.• Tst—The flag is tested.• U—The effect on the flag is undefined.• Gray shaded cells indicate that the flag is not affected by theinstruction.Table E-1.Instruction Effects on RFLAGSInstructionMnemonicID21VIP20VIF19AC18VM17RFLAGS Mnemonic and Bit NumberRF16NT14IOPL13-12OF11DF10IF9TF8SF7ZF6AF4PF2CF0AAAAASU U UTstModUModAADAAMUMod Mod U Mod UADC Mod Mod Mod Mod ModTstModADD Mod Mod Mod Mod Mod ModAND 0 Mod Mod U Mod 0ARPLBSFBSRModU U Mod U U UAppendix E: Instruction Effects on RFLAGS 493

- Page 472 and 473: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 474 and 475: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 476 and 477: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 478 and 479: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 480 and 481: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 482 and 483: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 484 and 485: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 486 and 487: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 488 and 489: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 490 and 491: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 492 and 493: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 494 and 495: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 496 and 497: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 498 and 499: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 500 and 501: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 502 and 503: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 504 and 505: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 506 and 507: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 508 and 509: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 510 and 511: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 512 and 513: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 514 and 515: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 516 and 517: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 518 and 519: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 520 and 521: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 524 and 525: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 526 and 527: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 528 and 529: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 530 and 531: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 532 and 533: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 534: AMD64 Technology 24594 Rev. 3.10 Fe

24594 Rev. 3.10 February 2005 AMD64 TechnologyAppendix EInstruction Effects on RFLAGSThe flags in the RFLAGS register are described in “FlagsRegister” in <strong>Volume</strong> 1 <strong>and</strong> “RFLAGS Register” in <strong>Volume</strong> 2.Table E-1 summarizes the effect that instructions have on theseflags. The table includes all instructions that affect the flags.<strong>Instructions</strong> not shown have no effect on RFLAGS.The following codes are used within the table:• 0—The flag is always cleared to 0.• 1—The flag is always set to 1.• AH—The flag is loaded with value from AH register.• Mod—The flag is modified, depending on the results of theinstruction.• Pop—The flag is loaded with value popped off of the stack.• Tst—The flag is tested.• U—The effect on the flag is undefined.• Gray shaded cells indicate that the flag is not affected by theinstruction.Table E-1.Instruction Effects on RFLAGSInstructionMnemonicID21VIP20VIF19AC18VM17RFLAGS Mnemonic <strong>and</strong> Bit NumberRF16NT14IOPL13-12OF11DF10IF9TF8SF7ZF6AF4PF2CF0AAAAASU U UTstModUModAADAAMUMod Mod U Mod UADC Mod Mod Mod Mod ModTstModADD Mod Mod Mod Mod Mod ModAND 0 Mod Mod U Mod 0ARPLBSFBSRModU U Mod U U UAppendix E: Instruction Effects on RFLAGS 493