Volume 3: General-Purpose and System Instructions - Stanford ...

Volume 3: General-Purpose and System Instructions - Stanford ... Volume 3: General-Purpose and System Instructions - Stanford ...

AMD64 Technology 24594 Rev. 3.10 February 2005WBINVDWriteback and Invalidate CachesThe WBINVD instruction writes all modified cache lines in the internal caches back tomain memory and invalidates (flushes) internal caches. It then causes external cachesto write back modified data to main memory; the external caches are subsequentlyinvalidated. After invalidating internal caches, the processor proceeds immediatelywith the execution of the next instruction without waiting for external hardware toinvalidate its caches.The INVD instruction can be used when cache coherence with memory is notimportant.This instruction does not invalidate TLB caches.This is a privileged instruction. The current privilege level of a procedure invalidatingthe processor’s internal caches must be zero.WBINVD is a serializing instruction.Mnemonic Opcode DescriptionWBINVD 0F 09 Write modified cache lines to main memory, invalidate internalcaches, and trigger external cache flushes.Related InstructionsCLFLUSH, INVDrFLAGS AffectedNoneExceptionsExceptionGeneral protection,#GPRealVirtual8086 Protected Cause of ExceptionX X CPL was not 0.372 WBINVD

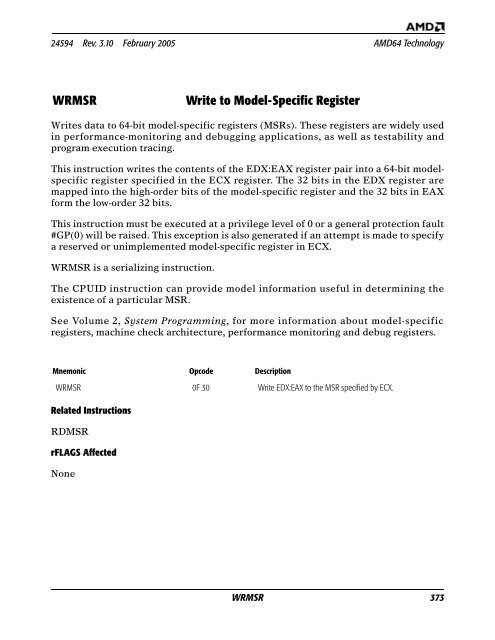

24594 Rev. 3.10 February 2005 AMD64 TechnologyWRMSRWrite to Model-Specific RegisterWrites data to 64-bit model-specific registers (MSRs). These registers are widely usedin performance-monitoring and debugging applications, as well as testability andprogram execution tracing.This instruction writes the contents of the EDX:EAX register pair into a 64-bit modelspecificregister specified in the ECX register. The 32 bits in the EDX register aremapped into the high-order bits of the model-specific register and the 32 bits in EAXform the low-order 32 bits.This instruction must be executed at a privilege level of 0 or a general protection fault#GP(0) will be raised. This exception is also generated if an attempt is made to specifya reserved or unimplemented model-specific register in ECX.WRMSR is a serializing instruction.The CPUID instruction can provide model information useful in determining theexistence of a particular MSR.See Volume 2, System Programming, for more information about model-specificregisters, machine check architecture, performance monitoring and debug registers.Mnemonic Opcode DescriptionWRMSR 0F 30 Write EDX:EAX to the MSR specified by ECX.Related InstructionsRDMSRrFLAGS AffectedNoneWRMSR 373

- Page 352 and 353: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 354 and 355: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 356 and 357: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 358 and 359: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 360 and 361: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 362 and 363: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 364 and 365: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 366 and 367: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 368 and 369: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 370 and 371: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 372 and 373: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 374 and 375: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 376 and 377: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 378 and 379: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 380 and 381: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 382 and 383: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 384 and 385: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 386 and 387: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 388 and 389: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 390 and 391: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 392 and 393: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 394 and 395: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 396 and 397: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 398 and 399: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 400 and 401: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 404 and 405: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 406 and 407: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 408 and 409: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 410 and 411: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 412 and 413: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 414 and 415: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 416 and 417: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 418 and 419: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 420 and 421: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 422 and 423: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 424 and 425: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 426 and 427: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 428 and 429: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 430 and 431: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 432 and 433: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 434 and 435: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 436 and 437: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 438 and 439: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 440 and 441: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 442 and 443: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 444 and 445: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 446 and 447: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 448 and 449: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 450 and 451: AMD64 Technology 24594 Rev. 3.10 Fe

24594 Rev. 3.10 February 2005 AMD64 TechnologyWRMSRWrite to Model-Specific RegisterWrites data to 64-bit model-specific registers (MSRs). These registers are widely usedin performance-monitoring <strong>and</strong> debugging applications, as well as testability <strong>and</strong>program execution tracing.This instruction writes the contents of the EDX:EAX register pair into a 64-bit modelspecificregister specified in the ECX register. The 32 bits in the EDX register aremapped into the high-order bits of the model-specific register <strong>and</strong> the 32 bits in EAXform the low-order 32 bits.This instruction must be executed at a privilege level of 0 or a general protection fault#GP(0) will be raised. This exception is also generated if an attempt is made to specifya reserved or unimplemented model-specific register in ECX.WRMSR is a serializing instruction.The CPUID instruction can provide model information useful in determining theexistence of a particular MSR.See <strong>Volume</strong> 2, <strong>System</strong> Programming, for more information about model-specificregisters, machine check architecture, performance monitoring <strong>and</strong> debug registers.Mnemonic Opcode DescriptionWRMSR 0F 30 Write EDX:EAX to the MSR specified by ECX.Related <strong>Instructions</strong>RDMSRrFLAGS AffectedNoneWRMSR 373