Volume 3: General-Purpose and System Instructions - Stanford ...

Volume 3: General-Purpose and System Instructions - Stanford ... Volume 3: General-Purpose and System Instructions - Stanford ...

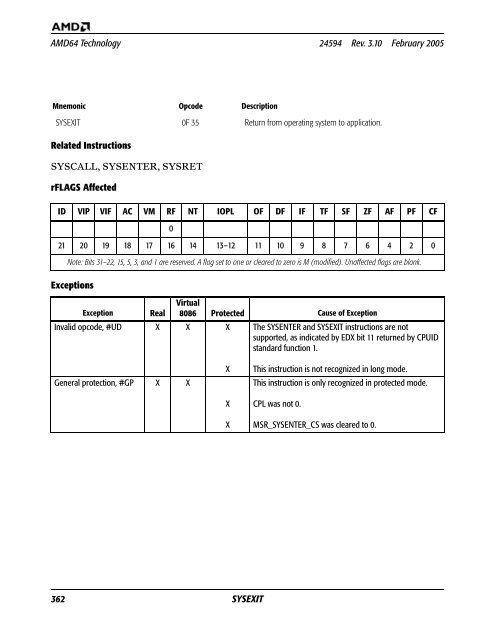

AMD64 Technology 24594 Rev. 3.10 February 2005Mnemonic Opcode DescriptionSYSEXIT 0F 35 Return from operating system to application.Related InstructionsSYSCALL, SYSENTER, SYSRETrFLAGS AffectedID VIP VIF AC VM RF NT IOPL OF DF IF TF SF ZF AF PF CFExceptions021 20 19 18 17 16 14 13–12 11 10 9 8 7 6 4 2 0Note: Bits 31–22, 15, 5, 3, and 1 are reserved. A flag set to one or cleared to zero is M (modified). Unaffected flags are blank.Exception RealInvalid opcode, #UD X X XVirtual8086 Protected Cause of ExceptionThe SYSENTER and SYSEXIT instructions are notsupported, as indicated by EDX bit 11 returned by CPUIDstandard function 1.General protection, #GP X XXXXThis instruction is not recognized in long mode.This instruction is only recognized in protected mode.CPL was not 0.MSR_SYSENTER_CS was cleared to 0.362 SYSEXIT

24594 Rev. 3.10 February 2005 AMD64 TechnologySYSRETFast System ReturnReturns from the operating system to an application. It is a low-latency system returninstruction designed for use by system and application software implementing a flatsegmentation memory model.The SYSCALL and SYSRET instructions are low-latency system call and returncontrol-transfer instructions that assume that the operating system implements a flatsegmentmemory model. By eliminating unneeded checks, and by loading predeterminedvalues into the CS and SS segment registers (both visible and hiddenportions), calls to and returns from the operating system are greatly simplified. Theseinstructions can be used in protected mode and are particularly well-suited for use in64-bit mode, which requires implementation of a paged, flat-segment memory model.This instruction has been optimized by reducing the number of checks and memoryreferences that are normally made so that a call or return takes substantially fewerinternal clock cycles when compared to the CALL/RET instruction method.It is assumed that the base, limit, and attributes of the Code Segment will remain flatfor all processes and for the operating system, and that only the current privilege levelfor the selector of the calling process should be changed from a current privilege levelof 0 to a new privilege level of 3. It is also assumed (but not checked) that the RPL ofthe SYSCALL and SYSRET target selectors are set to 0 and 3, respectively.SYSRET sets the CPL to 3, regardless of the values of bits 49–48 of the star register.SYSRET can only be executed in protected mode at CPL 0. SYSCALL and SYSRETmust be enabled by setting EFER.SCE to 1.It is the responsibility of the operating system to keep the descriptors in memory thatcorrespond to the CS and SS selectors loaded by the SYSCALL and SYSRETinstructions consistent with the segment base, limit, and attribute values forced bythese instructions.When a system procedure performs a SYSRET back to application software, the CSselector is updated from bits 63–50 of the STAR register (STAR.SYSRET_CS) asfollows:• If the return is to 32-bit mode (legacy or compatibility), CS is updated with thevalue of STAR.SYSRET_CS.• If the return is to 64-bit mode, CS is updated with the value of STAR.SYSRET_CS+ 16.SYSRET 363

- Page 342 and 343: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 344 and 345: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 346 and 347: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 348 and 349: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 350 and 351: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 352 and 353: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 354 and 355: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 356 and 357: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 358 and 359: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 360 and 361: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 362 and 363: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 364 and 365: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 366 and 367: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 368 and 369: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 370 and 371: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 372 and 373: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 374 and 375: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 376 and 377: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 378 and 379: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 380 and 381: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 382 and 383: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 384 and 385: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 386 and 387: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 388 and 389: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 390 and 391: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 394 and 395: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 396 and 397: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 398 and 399: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 400 and 401: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 402 and 403: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 404 and 405: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 406 and 407: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 408 and 409: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 410 and 411: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 412 and 413: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 414 and 415: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 416 and 417: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 418 and 419: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 420 and 421: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 422 and 423: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 424 and 425: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 426 and 427: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 428 and 429: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 430 and 431: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 432 and 433: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 434 and 435: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 436 and 437: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 438 and 439: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 440 and 441: AMD64 Technology 24594 Rev. 3.10 Fe

AMD64 Technology 24594 Rev. 3.10 February 2005Mnemonic Opcode DescriptionSYSEXIT 0F 35 Return from operating system to application.Related <strong>Instructions</strong>SYSCALL, SYSENTER, SYSRETrFLAGS AffectedID VIP VIF AC VM RF NT IOPL OF DF IF TF SF ZF AF PF CFExceptions021 20 19 18 17 16 14 13–12 11 10 9 8 7 6 4 2 0Note: Bits 31–22, 15, 5, 3, <strong>and</strong> 1 are reserved. A flag set to one or cleared to zero is M (modified). Unaffected flags are blank.Exception RealInvalid opcode, #UD X X XVirtual8086 Protected Cause of ExceptionThe SYSENTER <strong>and</strong> SYSEXIT instructions are notsupported, as indicated by EDX bit 11 returned by CPUIDst<strong>and</strong>ard function 1.<strong>General</strong> protection, #GP X XXXXThis instruction is not recognized in long mode.This instruction is only recognized in protected mode.CPL was not 0.MSR_SYSENTER_CS was cleared to 0.362 SYSEXIT