Volume 3: General-Purpose and System Instructions - Stanford ...

Volume 3: General-Purpose and System Instructions - Stanford ... Volume 3: General-Purpose and System Instructions - Stanford ...

AMD64 Technology 24594 Rev. 3.10 February 2005LMSWLoad Machine Status WordLoads the lower four bits of the 16-bit register or memory operand into bits 3–0 of themachine status word in register CR0. Only the protection enabled (PE), monitorcoprocessor (MP), emulation (EM), and task switched (TS) bits of CR0 are modified.Additionally, LMSW can set CR0.PE, but cannot clear it.The LMSW instruction can be used only when the current privilege level is 0. It is onlyprovided for compatibility with early processors.Use the MOV CR0 instruction to load all 32 or 64 bits of CR0.Mnemonic Opcode DescriptionLMSW reg/mem16 0F 01 /6 Load the lower 4 bits of the source into the lower 4 bits of CR0.Related InstructionsMOV (CRn), SMSWrFLAGS AffectedNoneExceptionsException RealVirtual8086 Protected Cause of ExceptionStack, #SS X X A memory address exceeded the stack segment limit or was noncanonical.General protection,#GPXXA memory address exceeded a data segment limit or was noncanonical.XXCPL was not 0.X A null data segment was used to reference memory.Page fault, #PF X A page fault resulted from the execution of the instruction.324 LMSW

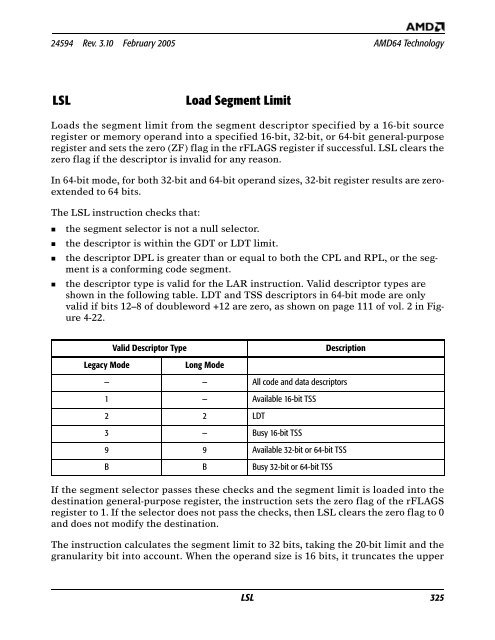

24594 Rev. 3.10 February 2005 AMD64 TechnologyLSLLoad Segment LimitLoads the segment limit from the segment descriptor specified by a 16-bit sourceregister or memory operand into a specified 16-bit, 32-bit, or 64-bit general-purposeregister and sets the zero (ZF) flag in the rFLAGS register if successful. LSL clears thezero flag if the descriptor is invalid for any reason.In 64-bit mode, for both 32-bit and 64-bit operand sizes, 32-bit register results are zeroextendedto 64 bits.The LSL instruction checks that:• the segment selector is not a null selector.• the descriptor is within the GDT or LDT limit.• the descriptor DPL is greater than or equal to both the CPL and RPL, or the segmentis a conforming code segment.• the descriptor type is valid for the LAR instruction. Valid descriptor types areshown in the following table. LDT and TSS descriptors in 64-bit mode are onlyvalid if bits 12–8 of doubleword +12 are zero, as shown on page 111 of vol. 2 in Figure4-22.Valid Descriptor TypeDescriptionLegacy ModeLong Mode— — All code and data descriptors1 — Available 16-bit TSS2 2 LDT3 — Busy 16-bit TSS9 9 Available 32-bit or 64-bit TSSB B Busy 32-bit or 64-bit TSSIf the segment selector passes these checks and the segment limit is loaded into thedestination general-purpose register, the instruction sets the zero flag of the rFLAGSregister to 1. If the selector does not pass the checks, then LSL clears the zero flag to 0and does not modify the destination.The instruction calculates the segment limit to 32 bits, taking the 20-bit limit and thegranularity bit into account. When the operand size is 16 bits, it truncates the upperLSL 325

- Page 304 and 305: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 306 and 307: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 308 and 309: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 310 and 311: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 312 and 313: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 314 and 315: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 316 and 317: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 318 and 319: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 320 and 321: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 322 and 323: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 324 and 325: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 326 and 327: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 328 and 329: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 330 and 331: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 332 and 333: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 334 and 335: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 336 and 337: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 338 and 339: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 340 and 341: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 342 and 343: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 344 and 345: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 346 and 347: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 348 and 349: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 350 and 351: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 352 and 353: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 356 and 357: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 358 and 359: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 360 and 361: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 362 and 363: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 364 and 365: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 366 and 367: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 368 and 369: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 370 and 371: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 372 and 373: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 374 and 375: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 376 and 377: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 378 and 379: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 380 and 381: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 382 and 383: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 384 and 385: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 386 and 387: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 388 and 389: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 390 and 391: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 392 and 393: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 394 and 395: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 396 and 397: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 398 and 399: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 400 and 401: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 402 and 403: AMD64 Technology 24594 Rev. 3.10 Fe

24594 Rev. 3.10 February 2005 AMD64 TechnologyLSLLoad Segment LimitLoads the segment limit from the segment descriptor specified by a 16-bit sourceregister or memory oper<strong>and</strong> into a specified 16-bit, 32-bit, or 64-bit general-purposeregister <strong>and</strong> sets the zero (ZF) flag in the rFLAGS register if successful. LSL clears thezero flag if the descriptor is invalid for any reason.In 64-bit mode, for both 32-bit <strong>and</strong> 64-bit oper<strong>and</strong> sizes, 32-bit register results are zeroextendedto 64 bits.The LSL instruction checks that:• the segment selector is not a null selector.• the descriptor is within the GDT or LDT limit.• the descriptor DPL is greater than or equal to both the CPL <strong>and</strong> RPL, or the segmentis a conforming code segment.• the descriptor type is valid for the LAR instruction. Valid descriptor types areshown in the following table. LDT <strong>and</strong> TSS descriptors in 64-bit mode are onlyvalid if bits 12–8 of doubleword +12 are zero, as shown on page 111 of vol. 2 in Figure4-22.Valid Descriptor TypeDescriptionLegacy ModeLong Mode— — All code <strong>and</strong> data descriptors1 — Available 16-bit TSS2 2 LDT3 — Busy 16-bit TSS9 9 Available 32-bit or 64-bit TSSB B Busy 32-bit or 64-bit TSSIf the segment selector passes these checks <strong>and</strong> the segment limit is loaded into thedestination general-purpose register, the instruction sets the zero flag of the rFLAGSregister to 1. If the selector does not pass the checks, then LSL clears the zero flag to 0<strong>and</strong> does not modify the destination.The instruction calculates the segment limit to 32 bits, taking the 20-bit limit <strong>and</strong> thegranularity bit into account. When the oper<strong>and</strong> size is 16 bits, it truncates the upperLSL 325