Volume 3: General-Purpose and System Instructions - Stanford ...

Volume 3: General-Purpose and System Instructions - Stanford ... Volume 3: General-Purpose and System Instructions - Stanford ...

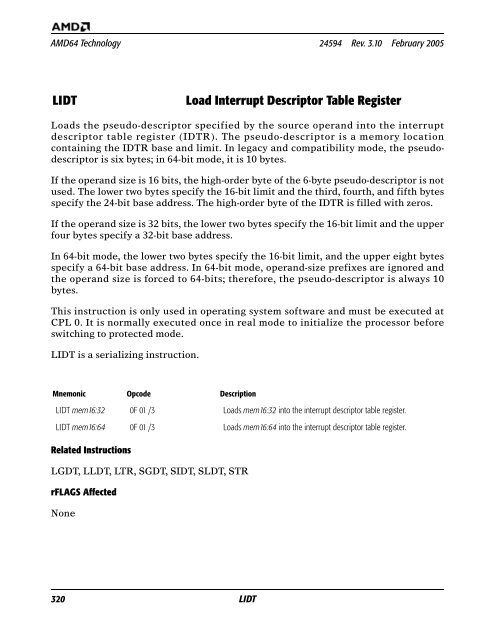

AMD64 Technology 24594 Rev. 3.10 February 2005LIDTLoad Interrupt Descriptor Table RegisterLoads the pseudo-descriptor specified by the source operand into the interruptdescriptor table register (IDTR). The pseudo-descriptor is a memory locationcontaining the IDTR base and limit. In legacy and compatibility mode, the pseudodescriptoris six bytes; in 64-bit mode, it is 10 bytes.If the operand size is 16 bits, the high-order byte of the 6-byte pseudo-descriptor is notused. The lower two bytes specify the 16-bit limit and the third, fourth, and fifth bytesspecify the 24-bit base address. The high-order byte of the IDTR is filled with zeros.If the operand size is 32 bits, the lower two bytes specify the 16-bit limit and the upperfour bytes specify a 32-bit base address.In 64-bit mode, the lower two bytes specify the 16-bit limit, and the upper eight bytesspecify a 64-bit base address. In 64-bit mode, operand-size prefixes are ignored andthe operand size is forced to 64-bits; therefore, the pseudo-descriptor is always 10bytes.This instruction is only used in operating system software and must be executed atCPL 0. It is normally executed once in real mode to initialize the processor beforeswitching to protected mode.LIDT is a serializing instruction.Mnemonic Opcode DescriptionLIDT mem16:32 0F 01 /3 Loads mem16:32 into the interrupt descriptor table register.LIDT mem16:64 0F 01 /3 Loads mem16:64 into the interrupt descriptor table register.Related InstructionsLGDT, LLDT, LTR, SGDT, SIDT, SLDT, STRrFLAGS AffectedNone320 LIDT

24594 Rev. 3.10 February 2005 AMD64 TechnologyExceptionsException RealVirtual8086 Protected Cause of ExceptionInvalid opcode, #UD X X X The operand was a register.Stack, #SS X X A memory address exceeded the stack segment limit or was noncanonical.General protection, #GP XX A memory address exceeded the data segment limit or was noncanonical.XXXCPL was not 0.The new IDT base address was non-canonical.X A null data segment was used to reference memory.Page fault, #PF X A page fault resulted from the execution of the instruction.LIDT 321

- Page 300 and 301: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 302 and 303: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 304 and 305: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 306 and 307: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 308 and 309: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 310 and 311: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 312 and 313: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 314 and 315: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 316 and 317: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 318 and 319: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 320 and 321: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 322 and 323: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 324 and 325: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 326 and 327: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 328 and 329: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 330 and 331: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 332 and 333: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 334 and 335: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 336 and 337: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 338 and 339: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 340 and 341: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 342 and 343: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 344 and 345: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 346 and 347: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 348 and 349: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 352 and 353: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 354 and 355: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 356 and 357: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 358 and 359: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 360 and 361: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 362 and 363: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 364 and 365: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 366 and 367: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 368 and 369: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 370 and 371: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 372 and 373: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 374 and 375: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 376 and 377: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 378 and 379: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 380 and 381: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 382 and 383: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 384 and 385: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 386 and 387: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 388 and 389: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 390 and 391: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 392 and 393: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 394 and 395: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 396 and 397: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 398 and 399: AMD64 Technology 24594 Rev. 3.10 Fe

AMD64 Technology 24594 Rev. 3.10 February 2005LIDTLoad Interrupt Descriptor Table RegisterLoads the pseudo-descriptor specified by the source oper<strong>and</strong> into the interruptdescriptor table register (IDTR). The pseudo-descriptor is a memory locationcontaining the IDTR base <strong>and</strong> limit. In legacy <strong>and</strong> compatibility mode, the pseudodescriptoris six bytes; in 64-bit mode, it is 10 bytes.If the oper<strong>and</strong> size is 16 bits, the high-order byte of the 6-byte pseudo-descriptor is notused. The lower two bytes specify the 16-bit limit <strong>and</strong> the third, fourth, <strong>and</strong> fifth bytesspecify the 24-bit base address. The high-order byte of the IDTR is filled with zeros.If the oper<strong>and</strong> size is 32 bits, the lower two bytes specify the 16-bit limit <strong>and</strong> the upperfour bytes specify a 32-bit base address.In 64-bit mode, the lower two bytes specify the 16-bit limit, <strong>and</strong> the upper eight bytesspecify a 64-bit base address. In 64-bit mode, oper<strong>and</strong>-size prefixes are ignored <strong>and</strong>the oper<strong>and</strong> size is forced to 64-bits; therefore, the pseudo-descriptor is always 10bytes.This instruction is only used in operating system software <strong>and</strong> must be executed atCPL 0. It is normally executed once in real mode to initialize the processor beforeswitching to protected mode.LIDT is a serializing instruction.Mnemonic Opcode DescriptionLIDT mem16:32 0F 01 /3 Loads mem16:32 into the interrupt descriptor table register.LIDT mem16:64 0F 01 /3 Loads mem16:64 into the interrupt descriptor table register.Related <strong>Instructions</strong>LGDT, LLDT, LTR, SGDT, SIDT, SLDT, STRrFLAGS AffectedNone320 LIDT