Volume 3: General-Purpose and System Instructions - Stanford ...

Volume 3: General-Purpose and System Instructions - Stanford ... Volume 3: General-Purpose and System Instructions - Stanford ...

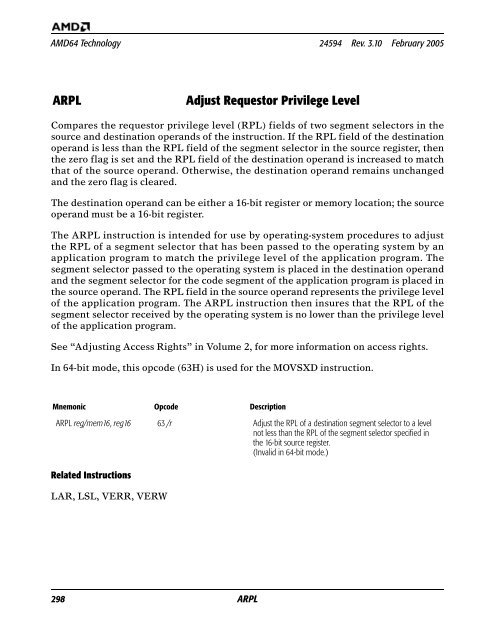

AMD64 Technology 24594 Rev. 3.10 February 2005ARPLAdjust Requestor Privilege LevelCompares the requestor privilege level (RPL) fields of two segment selectors in thesource and destination operands of the instruction. If the RPL field of the destinationoperand is less than the RPL field of the segment selector in the source register, thenthe zero flag is set and the RPL field of the destination operand is increased to matchthat of the source operand. Otherwise, the destination operand remains unchangedand the zero flag is cleared.The destination operand can be either a 16-bit register or memory location; the sourceoperand must be a 16-bit register.The ARPL instruction is intended for use by operating-system procedures to adjustthe RPL of a segment selector that has been passed to the operating system by anapplication program to match the privilege level of the application program. Thesegment selector passed to the operating system is placed in the destination operandand the segment selector for the code segment of the application program is placed inthe source operand. The RPL field in the source operand represents the privilege levelof the application program. The ARPL instruction then insures that the RPL of thesegment selector received by the operating system is no lower than the privilege levelof the application program.See “Adjusting Access Rights” in Volume 2, for more information on access rights.In 64-bit mode, this opcode (63H) is used for the MOVSXD instruction.Mnemonic Opcode DescriptionARPL reg/mem16, reg16 63 /r Adjust the RPL of a destination segment selector to a levelnot less than the RPL of the segment selector specified inthe 16-bit source register.(Invalid in 64-bit mode.)Related InstructionsLAR, LSL, VERR, VERW298 ARPL

24594 Rev. 3.10 February 2005 AMD64 TechnologyrFLAGS AffectedID VIP VIF AC VM RF NT IOPL OF DF IF TF SF ZF AF PF CF21 20 19 18 17 16 14 13–12 11 10 9 8 7 6 4 2 0Note: Bits 31–22, 15, 5, 3, and 1 are reserved. A flag set to one or cleared to zero is M (modified). Unaffected flags are blank. Undefinedflags are U.ExceptionsException RealVirtual8086 Protected Cause of ExceptionInvalid opcode, #UD X X This instruction is only recognized in protected legacy andcompatibility mode.Stack, #SS X A memory address exceeded the stack segment limit.General protection, #GPX A memory address exceeded a data segment limit.MXThe destination operand was in a non-writable segment.X A null segment selector was used to reference memory.Page fault, #PF X A page fault resulted from the execution of the instruction.Alignment check, #AC X An unaligned memory reference was performed while alignmentchecking was enabled.ARPL 299

- Page 278 and 279: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 280 and 281: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 282 and 283: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 284 and 285: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 286 and 287: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 288 and 289: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 290 and 291: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 292 and 293: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 294 and 295: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 296 and 297: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 298 and 299: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 300 and 301: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 302 and 303: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 304 and 305: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 306 and 307: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 308 and 309: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 310 and 311: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 312 and 313: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 314 and 315: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 316 and 317: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 318 and 319: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 320 and 321: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 322 and 323: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 324 and 325: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 326 and 327: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 330 and 331: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 332 and 333: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 334 and 335: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 336 and 337: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 338 and 339: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 340 and 341: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 342 and 343: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 344 and 345: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 346 and 347: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 348 and 349: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 350 and 351: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 352 and 353: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 354 and 355: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 356 and 357: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 358 and 359: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 360 and 361: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 362 and 363: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 364 and 365: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 366 and 367: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 368 and 369: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 370 and 371: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 372 and 373: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 374 and 375: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 376 and 377: AMD64 Technology 24594 Rev. 3.10 Fe

AMD64 Technology 24594 Rev. 3.10 February 2005ARPLAdjust Requestor Privilege LevelCompares the requestor privilege level (RPL) fields of two segment selectors in thesource <strong>and</strong> destination oper<strong>and</strong>s of the instruction. If the RPL field of the destinationoper<strong>and</strong> is less than the RPL field of the segment selector in the source register, thenthe zero flag is set <strong>and</strong> the RPL field of the destination oper<strong>and</strong> is increased to matchthat of the source oper<strong>and</strong>. Otherwise, the destination oper<strong>and</strong> remains unchanged<strong>and</strong> the zero flag is cleared.The destination oper<strong>and</strong> can be either a 16-bit register or memory location; the sourceoper<strong>and</strong> must be a 16-bit register.The ARPL instruction is intended for use by operating-system procedures to adjustthe RPL of a segment selector that has been passed to the operating system by anapplication program to match the privilege level of the application program. Thesegment selector passed to the operating system is placed in the destination oper<strong>and</strong><strong>and</strong> the segment selector for the code segment of the application program is placed inthe source oper<strong>and</strong>. The RPL field in the source oper<strong>and</strong> represents the privilege levelof the application program. The ARPL instruction then insures that the RPL of thesegment selector received by the operating system is no lower than the privilege levelof the application program.See “Adjusting Access Rights” in <strong>Volume</strong> 2, for more information on access rights.In 64-bit mode, this opcode (63H) is used for the MOVSXD instruction.Mnemonic Opcode DescriptionARPL reg/mem16, reg16 63 /r Adjust the RPL of a destination segment selector to a levelnot less than the RPL of the segment selector specified inthe 16-bit source register.(Invalid in 64-bit mode.)Related <strong>Instructions</strong>LAR, LSL, VERR, VERW298 ARPL