Volume 3: General-Purpose and System Instructions - Stanford ...

Volume 3: General-Purpose and System Instructions - Stanford ... Volume 3: General-Purpose and System Instructions - Stanford ...

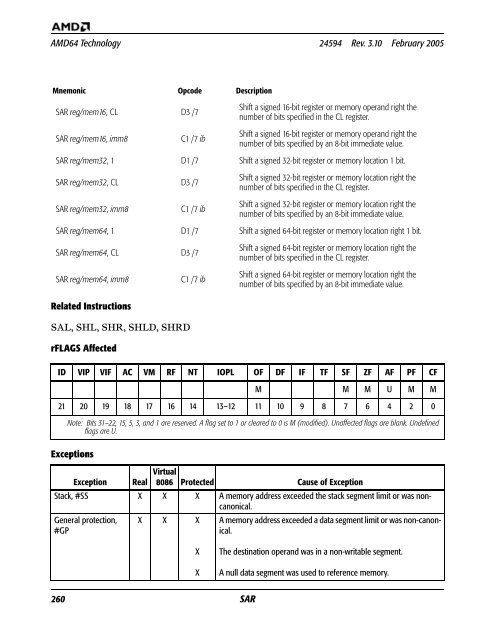

AMD64 Technology 24594 Rev. 3.10 February 2005Mnemonic Opcode DescriptionSAR reg/mem16, CL D3 /7Shift a signed 16-bit register or memory operand right thenumber of bits specified in the CL register.SAR reg/mem16, imm8C1 /7 ibShift a signed 16-bit register or memory operand right thenumber of bits specified by an 8-bit immediate value.SAR reg/mem32, 1 D1 /7 Shift a signed 32-bit register or memory location 1 bit.SAR reg/mem32, CL D3 /7Shift a signed 32-bit register or memory location right thenumber of bits specified in the CL register.SAR reg/mem32, imm8C1 /7 ibShift a signed 32-bit register or memory location right thenumber of bits specified by an 8-bit immediate value.SAR reg/mem64, 1 D1 /7 Shift a signed 64-bit register or memory location right 1 bit.SAR reg/mem64, CL D3 /7Shift a signed 64-bit register or memory location right thenumber of bits specified in the CL register.SAR reg/mem64, imm8Related InstructionsC1 /7 ibShift a signed 64-bit register or memory location right thenumber of bits specified by an 8-bit immediate value.SAL, SHL, SHR, SHLD, SHRDrFLAGS AffectedID VIP VIF AC VM RF NT IOPL OF DF IF TF SF ZF AF PF CFExceptionsM M M U M M21 20 19 18 17 16 14 13–12 11 10 9 8 7 6 4 2 0Note: Bits 31–22, 15, 5, 3, and 1 are reserved. A flag set to 1 or cleared to 0 is M (modified). Unaffected flags are blank. Undefinedflags are U.Exception RealVirtual8086 Protected Cause of ExceptionStack, #SS X X X A memory address exceeded the stack segment limit or was noncanonical.General protection,#GPX X XA memory address exceeded a data segment limit or was non-canonical.XXThe destination operand was in a non-writable segment.A null data segment was used to reference memory.260 SAR

24594 Rev. 3.10 February 2005 AMD64 TechnologyExceptionRealVirtual8086 Protected Cause of ExceptionPage fault, #PF X X A page fault resulted from the execution of the instruction.Alignment check, #AC X X An unaligned memory reference was performed while alignmentchecking was enabled.SAR 261

- Page 240 and 241: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 242 and 243: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 244 and 245: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 246 and 247: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 248 and 249: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 250 and 251: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 252 and 253: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 254 and 255: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 256 and 257: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 258 and 259: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 260 and 261: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 262 and 263: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 264 and 265: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 266 and 267: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 268 and 269: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 270 and 271: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 272 and 273: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 274 and 275: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 276 and 277: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 278 and 279: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 280 and 281: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 282 and 283: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 284 and 285: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 286 and 287: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 288 and 289: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 292 and 293: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 294 and 295: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 296 and 297: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 298 and 299: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 300 and 301: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 302 and 303: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 304 and 305: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 306 and 307: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 308 and 309: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 310 and 311: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 312 and 313: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 314 and 315: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 316 and 317: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 318 and 319: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 320 and 321: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 322 and 323: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 324 and 325: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 326 and 327: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 328 and 329: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 330 and 331: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 332 and 333: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 334 and 335: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 336 and 337: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 338 and 339: AMD64 Technology 24594 Rev. 3.10 Fe

AMD64 Technology 24594 Rev. 3.10 February 2005Mnemonic Opcode DescriptionSAR reg/mem16, CL D3 /7Shift a signed 16-bit register or memory oper<strong>and</strong> right thenumber of bits specified in the CL register.SAR reg/mem16, imm8C1 /7 ibShift a signed 16-bit register or memory oper<strong>and</strong> right thenumber of bits specified by an 8-bit immediate value.SAR reg/mem32, 1 D1 /7 Shift a signed 32-bit register or memory location 1 bit.SAR reg/mem32, CL D3 /7Shift a signed 32-bit register or memory location right thenumber of bits specified in the CL register.SAR reg/mem32, imm8C1 /7 ibShift a signed 32-bit register or memory location right thenumber of bits specified by an 8-bit immediate value.SAR reg/mem64, 1 D1 /7 Shift a signed 64-bit register or memory location right 1 bit.SAR reg/mem64, CL D3 /7Shift a signed 64-bit register or memory location right thenumber of bits specified in the CL register.SAR reg/mem64, imm8Related <strong>Instructions</strong>C1 /7 ibShift a signed 64-bit register or memory location right thenumber of bits specified by an 8-bit immediate value.SAL, SHL, SHR, SHLD, SHRDrFLAGS AffectedID VIP VIF AC VM RF NT IOPL OF DF IF TF SF ZF AF PF CFExceptionsM M M U M M21 20 19 18 17 16 14 13–12 11 10 9 8 7 6 4 2 0Note: Bits 31–22, 15, 5, 3, <strong>and</strong> 1 are reserved. A flag set to 1 or cleared to 0 is M (modified). Unaffected flags are blank. Undefinedflags are U.Exception RealVirtual8086 Protected Cause of ExceptionStack, #SS X X X A memory address exceeded the stack segment limit or was noncanonical.<strong>General</strong> protection,#GPX X XA memory address exceeded a data segment limit or was non-canonical.XXThe destination oper<strong>and</strong> was in a non-writable segment.A null data segment was used to reference memory.260 SAR