Volume 3: General-Purpose and System Instructions - Stanford ...

Volume 3: General-Purpose and System Instructions - Stanford ... Volume 3: General-Purpose and System Instructions - Stanford ...

AMD64 Technology 24594 Rev. 3.10 February 2005MOVMoveCopies an immediate value or the value in a general-purpose register, segmentregister, or memory location (second operand) to a general-purpose register, segmentregister, or memory location. The source and destination must be the same size (byte,word, doubleword, or quadword) and cannot both be memory locations.In opcodes A0 through A3, the memory offsets (called moffsets) are address sized. In64-bit mode, memory offsets default to 64 bits. Opcodes A0–A3, in 64-bit mode, are theonly cases that support a 64-bit offset value. (In all other cases, offsets anddisplacements are a maximum of 32 bits.) The B8 through BF (B8 +rq) opcodes, in 64-bit mode, are the only cases that support a 64-bit immediate value (in all other cases,immediate values are a maximum of 32 bits).When reading segment-registers with a 32-bit operand size, the processor zero-extendsthe 16-bit selector results to 32 bits. When reading segment-registers with a 64-bitoperand size, the processor zero-extends the 16-bit selector to 64 bits. If thedestination operand specifies a segment register (DS, ES, FS, GS, or SS), the sourceoperand must be a valid segment selector.It is possible to move a null segment selector value (0000–0003h) into the DS, ES, FS,or GS register. This action does not cause a general protection fault, but a subsequentreference to such a segment does cause a #GP exception. For more information aboutsegment selectors, see “Segment Selectors and Registers” on page 82.When the MOV instruction is used to load the SS register, the processor blocksexternal interrupts until after the execution of the following instruction. This actionallows the following instruction to be a MOV instruction to load a stack pointer intothe ESP register (MOV ESP,val) before an interrupt occurs. However, the LSSinstruction provides a more efficient method of loading SS and ESP.Attempting to use the MOV instruction to load the CS register generates an invalidopcode exception (#UD). Use the far JMP, CALL, or RET instructions to load the CSregister.To initialize a register to 0, rather than using a MOV instruction, it may be moreefficient to use the XOR instruction with identical destination and source operands.192 MOV

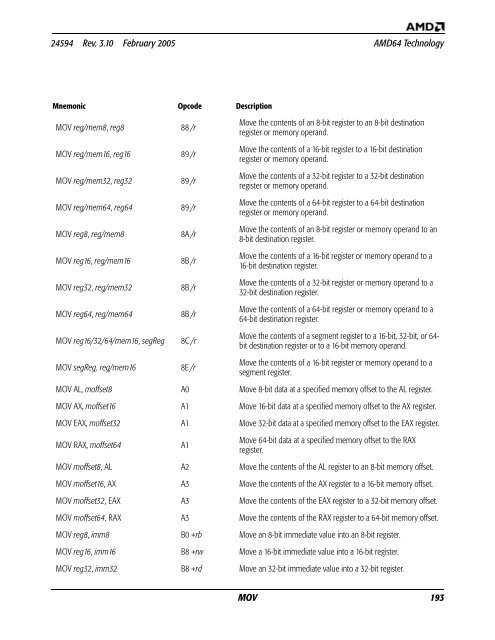

24594 Rev. 3.10 February 2005 AMD64 TechnologyMnemonic Opcode DescriptionMOV reg/mem8, reg8 88 /rMOV reg/mem16, reg16 89 /rMOV reg/mem32, reg32 89 /rMOV reg/mem64, reg64 89 /rMOV reg8, reg/mem8 8A /rMOV reg16, reg/mem16 8B /rMOV reg32, reg/mem32 8B /rMOV reg64, reg/mem64 8B /rMOV reg16/32/64/mem16, segReg 8C /rMOV segReg, reg/mem16 8E /rMove the contents of an 8-bit register to an 8-bit destinationregister or memory operand.Move the contents of a 16-bit register to a 16-bit destinationregister or memory operand.Move the contents of a 32-bit register to a 32-bit destinationregister or memory operand.Move the contents of a 64-bit register to a 64-bit destinationregister or memory operand.Move the contents of an 8-bit register or memory operand to an8-bit destination register.Move the contents of a 16-bit register or memory operand to a16-bit destination register.Move the contents of a 32-bit register or memory operand to a32-bit destination register.Move the contents of a 64-bit register or memory operand to a64-bit destination register.Move the contents of a segment register to a 16-bit, 32-bit, or 64-bit destination register or to a 16-bit memory operand.Move the contents of a 16-bit register or memory operand to asegment register.MOV AL, moffset8 A0 Move 8-bit data at a specified memory offset to the AL register.MOV AX, moffset16 A1 Move 16-bit data at a specified memory offset to the AX register.MOV EAX, moffset32 A1 Move 32-bit data at a specified memory offset to the EAX register.MOV RAX, moffset64A1Move 64-bit data at a specified memory offset to the RAXregister.MOV moffset8, AL A2 Move the contents of the AL register to an 8-bit memory offset.MOV moffset16, AX A3 Move the contents of the AX register to a 16-bit memory offset.MOV moffset32, EAX A3 Move the contents of the EAX register to a 32-bit memory offset.MOV moffset64, RAX A3 Move the contents of the RAX register to a 64-bit memory offset.MOV reg8, imm8 B0 +rb Move an 8-bit immediate value into an 8-bit register.MOV reg16, imm16 B8 +rw Move a 16-bit immediate value into a 16-bit register.MOV reg32, imm32 B8 +rd Move an 32-bit immediate value into a 32-bit register.MOV 193

- Page 172 and 173: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 174 and 175: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 176 and 177: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 178 and 179: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 180 and 181: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 182 and 183: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 184 and 185: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 186 and 187: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 188 and 189: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 190 and 191: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 192 and 193: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 194 and 195: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 196 and 197: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 198 and 199: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 200 and 201: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 202 and 203: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 204 and 205: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 206 and 207: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 208 and 209: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 210 and 211: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 212 and 213: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 214 and 215: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 216 and 217: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 218 and 219: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 220 and 221: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 224 and 225: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 226 and 227: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 228 and 229: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 230 and 231: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 232 and 233: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 234 and 235: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 236 and 237: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 238 and 239: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 240 and 241: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 242 and 243: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 244 and 245: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 246 and 247: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 248 and 249: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 250 and 251: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 252 and 253: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 254 and 255: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 256 and 257: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 258 and 259: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 260 and 261: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 262 and 263: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 264 and 265: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 266 and 267: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 268 and 269: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 270 and 271: AMD64 Technology 24594 Rev. 3.10 Fe

24594 Rev. 3.10 February 2005 AMD64 TechnologyMnemonic Opcode DescriptionMOV reg/mem8, reg8 88 /rMOV reg/mem16, reg16 89 /rMOV reg/mem32, reg32 89 /rMOV reg/mem64, reg64 89 /rMOV reg8, reg/mem8 8A /rMOV reg16, reg/mem16 8B /rMOV reg32, reg/mem32 8B /rMOV reg64, reg/mem64 8B /rMOV reg16/32/64/mem16, segReg 8C /rMOV segReg, reg/mem16 8E /rMove the contents of an 8-bit register to an 8-bit destinationregister or memory oper<strong>and</strong>.Move the contents of a 16-bit register to a 16-bit destinationregister or memory oper<strong>and</strong>.Move the contents of a 32-bit register to a 32-bit destinationregister or memory oper<strong>and</strong>.Move the contents of a 64-bit register to a 64-bit destinationregister or memory oper<strong>and</strong>.Move the contents of an 8-bit register or memory oper<strong>and</strong> to an8-bit destination register.Move the contents of a 16-bit register or memory oper<strong>and</strong> to a16-bit destination register.Move the contents of a 32-bit register or memory oper<strong>and</strong> to a32-bit destination register.Move the contents of a 64-bit register or memory oper<strong>and</strong> to a64-bit destination register.Move the contents of a segment register to a 16-bit, 32-bit, or 64-bit destination register or to a 16-bit memory oper<strong>and</strong>.Move the contents of a 16-bit register or memory oper<strong>and</strong> to asegment register.MOV AL, moffset8 A0 Move 8-bit data at a specified memory offset to the AL register.MOV AX, moffset16 A1 Move 16-bit data at a specified memory offset to the AX register.MOV EAX, moffset32 A1 Move 32-bit data at a specified memory offset to the EAX register.MOV RAX, moffset64A1Move 64-bit data at a specified memory offset to the RAXregister.MOV moffset8, AL A2 Move the contents of the AL register to an 8-bit memory offset.MOV moffset16, AX A3 Move the contents of the AX register to a 16-bit memory offset.MOV moffset32, EAX A3 Move the contents of the EAX register to a 32-bit memory offset.MOV moffset64, RAX A3 Move the contents of the RAX register to a 64-bit memory offset.MOV reg8, imm8 B0 +rb Move an 8-bit immediate value into an 8-bit register.MOV reg16, imm16 B8 +rw Move a 16-bit immediate value into a 16-bit register.MOV reg32, imm32 B8 +rd Move an 32-bit immediate value into a 32-bit register.MOV 193