Volume 3: General-Purpose and System Instructions - Stanford ...

Volume 3: General-Purpose and System Instructions - Stanford ... Volume 3: General-Purpose and System Instructions - Stanford ...

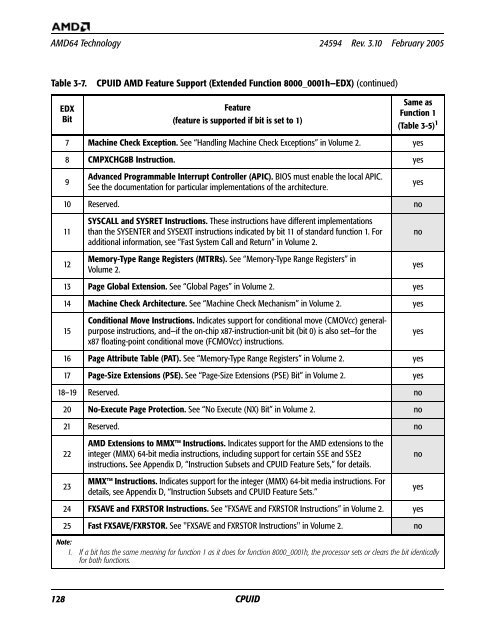

AMD64 Technology 24594 Rev. 3.10 February 2005Table 3-7.CPUID AMD Feature Support (Extended Function 8000_0001h—EDX) (continued)EDXBitFeature(feature is supported if bit is set to 1)Same asFunction 1(Table 3-5) 17 Machine Check Exception. See “Handling Machine Check Exceptions” in Volume 2. yes8 CMPXCHG8B Instruction. yes9Advanced Programmable Interrupt Controller (APIC). BIOS must enable the local APIC.See the documentation for particular implementations of the architecture.yes10 Reserved. no1112SYSCALL and SYSRET Instructions. These instructions have different implementationsthan the SYSENTER and SYSEXIT instructions indicated by bit 11 of standard function 1. Foradditional information, see “Fast System Call and Return” in Volume 2.Memory-Type Range Registers (MTRRs). See “Memory-Type Range Registers” inVolume 2.noyes13 Page Global Extension. See “Global Pages” in Volume 2. yes14 Machine Check Architecture. See “Machine Check Mechanism” in Volume 2. yes15Conditional Move Instructions. Indicates support for conditional move (CMOVcc) generalpurposeinstructions, and—if the on-chip x87-instruction-unit bit (bit 0) is also set—for thex87 floating-point conditional move (FCMOVcc) instructions.yes16 Page Attribute Table (PAT). See “Memory-Type Range Registers” in Volume 2. yes17 Page-Size Extensions (PSE). See “Page-Size Extensions (PSE) Bit” in Volume 2. yes18–19 Reserved. no20 No-Execute Page Protection. See “No Execute (NX) Bit” in Volume 2. no21 Reserved. no2223AMD Extensions to MMX Instructions. Indicates support for the AMD extensions to theinteger (MMX) 64-bit media instructions, including support for certain SSE and SSE2instructions. See Appendix D, “Instruction Subsets and CPUID Feature Sets,” for details.MMX Instructions. Indicates support for the integer (MMX) 64-bit media instructions. Fordetails, see Appendix D, “Instruction Subsets and CPUID Feature Sets.”noyes24 FXSAVE and FXRSTOR Instructions. See “FXSAVE and FXRSTOR Instructions” in Volume 2. yes25 Fast FXSAVE/FXRSTOR. See "FXSAVE and FXRSTOR Instructions" in Volume 2. noNote:1. If a bit has the same meaning for function 1 as it does for function 8000_0001h, the processor sets or clears the bit identicallyfor both functions.128 CPUID

24594 Rev. 3.10 February 2005 AMD64 TechnologyTable 3-7.CPUID AMD Feature Support (Extended Function 8000_0001h—EDX) (continued)EDXBit26 Reserved.Feature(feature is supported if bit is set to 1)Same asFunction 1(Table 3-5) 127 RDTSCP Instruction. no28 Reserved.29 Long Mode. See “Long Mode” in Volume 2. no3031AMD Extensions to 3DNow! Instructions. Indicates support for the AMD extensions tothe floating-point (3DNow!) 64-bit media instructions. For details, see Appendix D,“Instruction Subsets and CPUID Feature Sets.”AMD 3DNow! Instructions. Indicates support for the floating-point (3DNow!) 64-bitmedia instructions. For details, see Appendix D, “Instruction Subsets and CPUID FeatureSets.”nonoNote:1. If a bit has the same meaning for function 1 as it does for function 8000_0001h, the processor sets or clears the bit identicallyfor both functions.Extended Functions8000_0002h–8000_0004h:Processor NameExtended functions 8000_0002h, 8000_0003h, and 8000_0004h together return anASCII string containing the name of the processor implementation. Software cansimply call these three functions in numerical order to obtain a 48-character ASCIIname string. Although the name string can be up to 48 characters in length, shorternames have unused byte locations filled with the ASCII null character (00h).Note: The BIOS must program the name string before these functions are executed;otherwise, these functions return the default processor name string (48 ASCIInull characters).The name string returned by these functions is in little-endian format. Extendedfunction 8000_0002h returns the first 16 characters of the name and extendedfunction 8000_0004h returns the last 16 characters. For each of the three groups of 16characters, the functions return the name (in order of least-significant to mostsignificantbyte) in the EAX, EBX, ECX, and EDX registers. The first character residesin the least-significant byte of EAX, and the last character resides in the mostsignificantbyte of EDX.CPUID 129

- Page 108 and 109: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 110 and 111: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 112 and 113: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 114 and 115: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 116 and 117: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 118 and 119: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 120 and 121: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 122 and 123: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 124 and 125: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 126 and 127: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 128 and 129: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 130 and 131: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 132 and 133: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 134 and 135: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 136 and 137: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 138 and 139: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 140 and 141: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 142 and 143: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 144 and 145: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 146 and 147: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 148 and 149: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 150 and 151: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 152 and 153: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 154 and 155: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 156 and 157: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 160 and 161: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 162 and 163: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 164 and 165: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 166 and 167: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 168 and 169: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 170 and 171: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 172 and 173: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 174 and 175: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 176 and 177: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 178 and 179: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 180 and 181: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 182 and 183: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 184 and 185: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 186 and 187: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 188 and 189: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 190 and 191: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 192 and 193: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 194 and 195: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 196 and 197: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 198 and 199: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 200 and 201: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 202 and 203: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 204 and 205: AMD64 Technology 24594 Rev. 3.10 Fe

- Page 206 and 207: AMD64 Technology 24594 Rev. 3.10 Fe

AMD64 Technology 24594 Rev. 3.10 February 2005Table 3-7.CPUID AMD Feature Support (Extended Function 8000_0001h—EDX) (continued)EDXBitFeature(feature is supported if bit is set to 1)Same asFunction 1(Table 3-5) 17 Machine Check Exception. See “H<strong>and</strong>ling Machine Check Exceptions” in <strong>Volume</strong> 2. yes8 CMPXCHG8B Instruction. yes9Advanced Programmable Interrupt Controller (APIC). BIOS must enable the local APIC.See the documentation for particular implementations of the architecture.yes10 Reserved. no1112SYSCALL <strong>and</strong> SYSRET <strong>Instructions</strong>. These instructions have different implementationsthan the SYSENTER <strong>and</strong> SYSEXIT instructions indicated by bit 11 of st<strong>and</strong>ard function 1. Foradditional information, see “Fast <strong>System</strong> Call <strong>and</strong> Return” in <strong>Volume</strong> 2.Memory-Type Range Registers (MTRRs). See “Memory-Type Range Registers” in<strong>Volume</strong> 2.noyes13 Page Global Extension. See “Global Pages” in <strong>Volume</strong> 2. yes14 Machine Check Architecture. See “Machine Check Mechanism” in <strong>Volume</strong> 2. yes15Conditional Move <strong>Instructions</strong>. Indicates support for conditional move (CMOVcc) generalpurposeinstructions, <strong>and</strong>—if the on-chip x87-instruction-unit bit (bit 0) is also set—for thex87 floating-point conditional move (FCMOVcc) instructions.yes16 Page Attribute Table (PAT). See “Memory-Type Range Registers” in <strong>Volume</strong> 2. yes17 Page-Size Extensions (PSE). See “Page-Size Extensions (PSE) Bit” in <strong>Volume</strong> 2. yes18–19 Reserved. no20 No-Execute Page Protection. See “No Execute (NX) Bit” in <strong>Volume</strong> 2. no21 Reserved. no2223AMD Extensions to MMX <strong>Instructions</strong>. Indicates support for the AMD extensions to theinteger (MMX) 64-bit media instructions, including support for certain SSE <strong>and</strong> SSE2instructions. See Appendix D, “Instruction Subsets <strong>and</strong> CPUID Feature Sets,” for details.MMX <strong>Instructions</strong>. Indicates support for the integer (MMX) 64-bit media instructions. Fordetails, see Appendix D, “Instruction Subsets <strong>and</strong> CPUID Feature Sets.”noyes24 FXSAVE <strong>and</strong> FXRSTOR <strong>Instructions</strong>. See “FXSAVE <strong>and</strong> FXRSTOR <strong>Instructions</strong>” in <strong>Volume</strong> 2. yes25 Fast FXSAVE/FXRSTOR. See "FXSAVE <strong>and</strong> FXRSTOR <strong>Instructions</strong>" in <strong>Volume</strong> 2. noNote:1. If a bit has the same meaning for function 1 as it does for function 8000_0001h, the processor sets or clears the bit identicallyfor both functions.128 CPUID