Cyclone V SoC FPGA Development Board Reference Manual - Altera

Cyclone V SoC FPGA Development Board Reference Manual - Altera

Cyclone V SoC FPGA Development Board Reference Manual - Altera

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

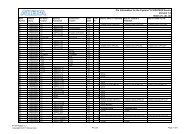

Chapter 2: <strong>Board</strong> Components 2–45MemoryTable 2–33. DDR3 SDRAM Pin Assignments, Schematic Signal Names, and Functions (Part 5 of 5)<strong>Board</strong><strong>Reference</strong>SchematicSignal NameF2 DDR3_HPS_DQ7 J29 1.5-V SSTL Class I Data busC8 DDR3_HPS_DQ8 K26 1.5-V SSTL Class I Data busB8 DDR3_HPS_DQ9 L26 1.5-V SSTL Class I Data busD7 DDR3_HPS_DQ10 K29 1.5-V SSTL Class I Data busA7 DDR3_HPS_DQ11 K27 1.5-V SSTL Class I Data busC2 DDR3_HPS_DQ12 M26 1.5-V SSTL Class I Data busC3 DDR3_HPS_DQ13 M27 1.5-V SSTL Class I Data busA3 DDR3_HPS_DQ14 L28 1.5-V SSTL Class I Data busA2 DDR3_HPS_DQ15 M30 1.5-V SSTL Class I Data busG3 DDR3_HPS_DQS_N0 M19B7 DDR3_HPS_DQS_N1 N24F3 DDR3_HPS_DQS_P0 N18QSPI Flash (HPS)<strong>Cyclone</strong> V <strong>SoC</strong>Pin NumberI/O StandardDifferential 1.5-VSSTL Class IDifferential 1.5-VSSTL Class IDifferential 1.5-VSSTL Class IDescriptionData strobe P byte lane 0Data strobe N byte lane 0Data strobe P byte lane 1C7 DDR3_HPS_DQS_P1 N25Differential 1.5-VSSTL Class IData strobe N byte lane 1K1 DDR3_HPS_ODT H28 1.5-V SSTL Class I On-die termination enableJ3 DDR3_HPS_RASN D30 1.5-V SSTL Class I Row address selectT2 DDR3_HPS_RESETN P30 1.5-V SSTL Class I ResetL3 DDR3_HPS_WEN C28 1.5-V SSTL Class I Write enableL8 DDR3_HPS_ZQ — 1.5-V SSTL Class I ZQ impedance calibrationThe development board supports one 512-Mb quad-SPI (QSPI) flash device for nonvolatilestorage of the HPS boot code, user data, and program. The device connects tothe HPS dedicated interface. The device interface may contain a secondary boot code.This 4-bit data memory interface can sustain burst read operations at up to 108 MHzfor a throughput of 54 MBps. Erase capability is at 4 KB, 64 KB, and 32 MB.Table 2–34 lists the QSPI flash pin assignments, signal names, and functions. Thesignal names and types are relative to the <strong>Cyclone</strong> V <strong>SoC</strong> in terms of I/O setting anddirection.Table 2–34. QSPI Flash Schematic Signal Names and Functions<strong>Board</strong><strong>Reference</strong> (U5)SchematicSignal Name<strong>Cyclone</strong> V <strong>SoC</strong> PinNumberI/O Standard16 QSPI_CLK D19 3.3-V Clock15 QSPI_IO0 C20 3.3-V Data bus8 QSPI_IO1 H18 3.3-V Data bus9 QSPI_IO2 A19 3.3-V Data bus1 QSPI_IO3 E19 3.3-V Data busDescriptionNovember 2013 <strong>Altera</strong> Corporation <strong>Cyclone</strong> V <strong>SoC</strong> <strong>Development</strong> <strong>Board</strong><strong>Reference</strong> <strong>Manual</strong>