Cyclone V SoC FPGA Development Board Reference Manual - Altera

Cyclone V SoC FPGA Development Board Reference Manual - Altera

Cyclone V SoC FPGA Development Board Reference Manual - Altera

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

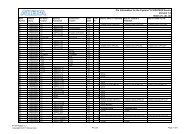

Chapter 2: <strong>Board</strong> Components 2–35Components and InterfacesTable 2–25 lists the PHY device pin assignments, signal names, and functions. Thesignal names and types are relative to the <strong>Cyclone</strong> V <strong>SoC</strong> in terms of I/O setting anddirection.Table 2–25. PHY Device Schematic Signal Names and Functions<strong>Board</strong><strong>Reference</strong> (U50)Real-Time Clock (HPS)SPI MasterI 2 C InterfaceSchematic SignalName<strong>Cyclone</strong> V <strong>SoC</strong>Pin NumberI/O Standard7 CANH_P — 3.3-V CAN bus line high6 CANL_N — 3.3-V CAN bus line lowThe HPS system has a battery backed real-time clock (RTC) connected through the I 2 Cinterface. The RTC is implemented using a DS1339 device from MaximSemiconductor. The device has a built-in power sense circuit that detects powerfailures and automatically switches to backup battery supply, maintaining time. Thedevice uses a 357 coin battery with a nominal voltage of 1.55 V. Using typical currentcapacity, the RTC is expected to have 120,000 backup hours. The battery is mountedinside a holder attached to the board to allow battery replacement or removal.Table 2–25 lists the RTC device pin assignments, signal names, and functions. Thesignal names and types are relative to the <strong>Cyclone</strong> V <strong>SoC</strong> in terms of I/O setting anddirection.Table 2–26. RTC Device Schematic Signal Names and Functions<strong>Board</strong><strong>Reference</strong> (U50)Schematic SignalName<strong>Cyclone</strong> V <strong>SoC</strong>Pin NumberI/O StandardThe HPS system has a SPI master interface available on the board. This interfaceconnects to the Linear Technology expansion header (J31). This header can power andinterface to most Linear Technology daughter boards such as the included DC934Dual D/A and A/D board.The HPS system has one I 2 C interface for communicating with the on-board andexternal components. The data rate is 50kbps.Table 2–25 lists the I 2 C interface address map.DescriptionDescription16 I2C_SDA_HPS C23 3.3-V Management serial data1 I2C_SCL_HPS D22 3.3-V Management serial clockTable 2–27. I 2 C interface address mapAddress0x680x500x5CDeviceReal-time clockLCD<strong>FPGA</strong> power monitorNovember 2013 <strong>Altera</strong> Corporation <strong>Cyclone</strong> V <strong>SoC</strong> <strong>Development</strong> <strong>Board</strong><strong>Reference</strong> <strong>Manual</strong>