Cyclone V SoC FPGA Development Board Reference Manual - Altera

Cyclone V SoC FPGA Development Board Reference Manual - Altera

Cyclone V SoC FPGA Development Board Reference Manual - Altera

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

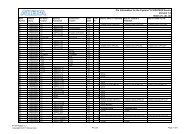

2–24 Chapter 2: <strong>Board</strong> ComponentsComponents and InterfacesTable 2–17. Off-<strong>Board</strong> Clock OutputsSourceTable 2–17 lists the clock outputs for the development board.Components and InterfacesThis section describes the development board's communication ports and interfacecards relative to the <strong>Cyclone</strong> V <strong>SoC</strong> device. The development board supports thefollowing communication ports:■■■■■■■■■■PCI ExpressSchematic SignalNamePCI Express10/100/1000 Ethernet (HPS)10/100 Ethernet (<strong>FPGA</strong>)HSMCRS-232 Serial UART (HPS)CAN bus (HPS)Real-Time clock (HPS)SPI masterI 2 CSDI videoI/O Standard<strong>Cyclone</strong> V <strong>SoC</strong>Pin NumberDescriptionSamtec HSMC HSMA_CLK_OUT0 2.5-V CMOS A10 <strong>FPGA</strong> CMOS output (or GPIO)HSMA_CLK_OUT_P1 2.5-V CMOS AJ2Samtec HSMCCMOS outputHSMA_CLK_OUT_N1 2.5-V CMOS AC12HSMA_CLK_OUT_P2 LVDS/2.5V CMOS E7 LVDS output. Can also support 2x CMOSSamtec HSMCHSMA_CLK_OUT_N2 LVDS/2.5V CMOS E6 outputs.PCI Express PCIE_REFCLK_QL0_P HCSL W8HCSL output to the PCI Express socketSocketPCIE_REFCLK_QL0_N HCSL W7The PCI Express interface on the development board supports auto-negotiatingchannel width from ×1 to ×4 as well as the connection speed of Gen1 at 2.5 Gbps/lanefor a maximum of 10 Gbps bandwidth.The PCIE_REFCLK_P/N signal is a 100-MHz differential input that is driven to thedaughter card through the PCI Express edge connector. This signal connects directlyto a <strong>Cyclone</strong> V <strong>SoC</strong> REFCLK input pin pair using DC coupling. The I/O standard isHigh-Speed Current Steering Logic (HCSL).<strong>Cyclone</strong> V <strong>SoC</strong> <strong>Development</strong> <strong>Board</strong> November 2013 <strong>Altera</strong> Corporation<strong>Reference</strong> <strong>Manual</strong>