Cyclone V SoC FPGA Development Board Reference Manual - Altera

Cyclone V SoC FPGA Development Board Reference Manual - Altera

Cyclone V SoC FPGA Development Board Reference Manual - Altera

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

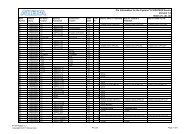

2–20 Chapter 2: <strong>Board</strong> ComponentsGeneral User Input/OutputMAX V Reset Push ButtonThe MAX V reset push button, MAX_RESETn (S2), is an input to the MAX V CPLD5M2210 System Controller. This push button is the default reset for the CPLD logic.Program Configuration Push ButtonThe program configuration push button, PGM_CONFIG (S12), is an input to the MAX VCPLD 5M2210 System Controller. This input forces a <strong>FPGA</strong> reconfiguration from theflash memory. The location in the flash memory is based on the settings ofPGM_LED[2:0], which is controlled by the program select push button, PGM_SEL (S2).Valid settings include PGM_LED0, PGM_LED1, or PGM_LED2 on the three pages in flashmemory reserved for <strong>FPGA</strong> designs.Program Select Push ButtonGeneral User Input/OutputThe program select push button, PGM_SEL (S11), is an input to the MAX V CPLDSystem Controller. This push button toggles the PGM_LED[2:0]sequence that selectswhich location in the flash memory is used to configure the <strong>FPGA</strong>. Refer to Table 2–6on page 2–14 for the PGM_LED[2:0] sequence definitions.This section describes the user I/O interface to the <strong>FPGA</strong>, including the push buttons,DIP switches, LEDs, expansion header, and character LCD.User-Defined Push ButtonsThe development board includes six user-defined push buttons. For informationabout the system and safe reset push buttons, refer to “Setup Elements” on page 2–17.<strong>Board</strong> references S1–S6 are push buttons for controlling the <strong>FPGA</strong> designs that loadsinto the <strong>Cyclone</strong> V <strong>SoC</strong> device. Push buttons S5 and S6 connect to the <strong>FPGA</strong> whilepush buttons S1–S4 connect to the HPS. When you press and hold down the switch,the device pin is set to logic 0; when you release the switch, the device pin is set tologic 1. There are no board-specific functions for these general user push buttons.Table 2–12 lists the user-defined push button schematic signal names and theircorresponding <strong>Cyclone</strong> V <strong>SoC</strong> pin numbers.Table 2–12. User-Defined Push Button Schematic Signal Names and Functions<strong>Board</strong> <strong>Reference</strong> Schematic Signal Name<strong>Cyclone</strong> V <strong>SoC</strong> PinNumberI/O StandardS6 USER_PB_<strong>FPGA</strong>0 AA13 1.5-VS5 USER_PB_<strong>FPGA</strong>1 AB13 1.5-VS4 USER_PB_HPS0 T30 2.5-VS3 USER_PB_HPS1 U28 2.5-VS2 USER_PB_HPS2 T21 2.5-VS1 USER_PB_HPS3 U20 2.5-V<strong>Cyclone</strong> V <strong>SoC</strong> <strong>Development</strong> <strong>Board</strong> November 2013 <strong>Altera</strong> Corporation<strong>Reference</strong> <strong>Manual</strong>