Cyclone V SoC FPGA Development Board Reference Manual - Altera

Cyclone V SoC FPGA Development Board Reference Manual - Altera

Cyclone V SoC FPGA Development Board Reference Manual - Altera

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

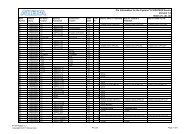

Chapter 2: <strong>Board</strong> Components 2–15<strong>FPGA</strong> ConfigurationFigure 2–4. PFL ConfigurationFigure 2–4 shows the PFL configuration.2.5 V2.5 V2.5 V 2.5 V56.2 Ω 100 ΩDIP SwitchMAX V CPLD5M2210 System ControllerMAX_ERRORMAX_LOADFACTORYUSB_BLASTERCLK125A_ENSi570_ENFACTORY_LOADSECURITY_MODEMAX_RESETnPGM_CONFIG<strong>FPGA</strong>_CVP_DONE<strong>FPGA</strong>_INIT_DONE50 MHz100 MHz56.2 Ω10 kΩCVP_CONFDONEINIT_DONE<strong>FPGA</strong>_nSTATUSnSTATUS<strong>FPGA</strong>_nCONFIGnCONFIG<strong>FPGA</strong>_CONF_DONECONF_DONEnCECVP_CONF_DONECONF_DONEPS PORT<strong>FPGA</strong>_DATA [3:0]<strong>FPGA</strong>_DATA [4]DATA [3:0]DATA [4]<strong>FPGA</strong>_DATA [7:5] DATA [7:5]<strong>FPGA</strong>_DCLKDCLK<strong>Cyclone</strong> V <strong>SoC</strong>MSEL4MSEL3MSEL2MSEL1BOOTSEL0BOOTSEL1BOOTSEL2MSEL[4:0] andBOOTSEL[3:0]also connects to theMAX V CPLDDIP SwitchDIP Switch2.5 V56.2 ΩPGM_SELPGM_LED0PGM_LED1PGM_LED2EPCQ_nCSFLASH_A [25:1]FLASH_D [15:0]FLASH_CEnFLASH_OEnFLASH_WEnFLASH_RYBSYnFLASH_CLKFLASH_RSTnFLASH_ADVnDATA [3:0]DCLKnCEEPCQCFI Flash2.5 VFLASH_A [25:0]FLASH_D [15:0]FLASH_CEnFLASH_OEnFLASH_WEnFLASH_RYBSYnFLASH_CLKFLASH_RESETn10 kΩFLASH_WPnFLASH_ADVn10 kΩfFor more information on the following topics, refer to the respective documents:■■<strong>Board</strong> Update Portal, PFL design, and flash memory map storage, refer to the<strong>Cyclone</strong> V <strong>SoC</strong> <strong>Development</strong> Kit User GuidePFL megafunction, refer to Parallel Flash Loader Megafunction User Guide.<strong>FPGA</strong> Programming over External USB-BlasterThe JTAG chain header provides another method for configuring the <strong>FPGA</strong> using anexternal USB-Blaster device with the Quartus II Programmer running on a PC. Toprevent contention between the JTAG masters, the embedded USB-Blaster isautomatically disabled when you connect an external USB-Blaster to the JTAG chainthrough the JTAG chain header.November 2013 <strong>Altera</strong> Corporation <strong>Cyclone</strong> V <strong>SoC</strong> <strong>Development</strong> <strong>Board</strong><strong>Reference</strong> <strong>Manual</strong>