Cyclone V SoC FPGA Development Board Reference Manual - Altera

Cyclone V SoC FPGA Development Board Reference Manual - Altera

Cyclone V SoC FPGA Development Board Reference Manual - Altera

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

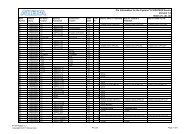

Chapter 2: <strong>Board</strong> Components 2–9MAX V CPLD 5M2210 System ControllerTable 2–4. MAX V CPLD System Controller Device Pin-Out (Part 3 of 4)<strong>Board</strong><strong>Reference</strong> (U19)Schematic Signal Name I/O Standard DescriptionF6 <strong>FPGA</strong>_CONFIG_D13 2.5-V <strong>FPGA</strong> configuration dataG2 <strong>FPGA</strong>_CONFIG_D14 2.5-V <strong>FPGA</strong> configuration dataG3 <strong>FPGA</strong>_CONFIG_D15 2.5-V <strong>FPGA</strong> configuration dataN3 <strong>FPGA</strong>_CVP_CONFDONE 2.5-V <strong>FPGA</strong> Configuration via Protocol (CvP) doneJ3 <strong>FPGA</strong>_DCLK 2.5-V <strong>FPGA</strong> configuration clockN1 <strong>FPGA</strong>_NCONFIG 2.5-V <strong>FPGA</strong> configuration activeJ4 <strong>FPGA</strong>_NSTATUS 2.5-V <strong>FPGA</strong> configuration readyH1 <strong>FPGA</strong>_PR_DONE 2.5-V <strong>FPGA</strong> partial reconfiguration doneP2 <strong>FPGA</strong>_PR_ERROR 2.5-V <strong>FPGA</strong> partial reconfiguration errorE2 <strong>FPGA</strong>_PR_READY 2.5-V <strong>FPGA</strong> partial reconfiguration readyF5 <strong>FPGA</strong>_PR_REQUEST 2.5-V <strong>FPGA</strong> partial reconfiguration requestB11 HPS_RESETN 2.5-V HPS reset push buttonB8 HSMA_PRSNTN 2.5-V HSMC port A presentM1 I2C_SCL_MAX 2.5-V Programmable oscillator I 2 C clockM2 I2C_SDA_MAX 2.5-V Programmable oscillator I 2 C dataL6 JTAG_MAX_TDI 2.5-V JTAG chain data inM5 JTAG_MAX_TDO 2.5-V JTAG chain data outN4 JTAG_MAX_TMS 2.5-V JTAG chain modeP3 JTAG_MUX_TCK 2.5-V JTAG chain clockP11 M570_CLOCK 1.8-V25-MHz clock to embedded USB-Blaster II for sendingFACTORY commandL5 M570_PCIE_JTAG_EN 2.5-V M570 JTAG enable for the embedded USB-Blaster IIH2 MAX_AS_CONF 2.5-VDriven low to enable AS configuration from the EPCQ flashthrough U13 to the <strong>FPGA</strong>E11 MAX_CONF_DONE 2.5-V Embedded USB-Blaster II configuration done LEDA4 MAX_ERROR 2.5-V <strong>FPGA</strong> configuration error LEDG4 MAX_<strong>FPGA</strong>_MISO 2.5-V <strong>FPGA</strong> to MAX V SPI bus data outputG1 MAX_<strong>FPGA</strong>_MOSI 2.5-V <strong>FPGA</strong> to MAX V SPI bus data inputH3 MAX_<strong>FPGA</strong>_SCK 2.5-V <strong>FPGA</strong> to MAX V SPI bus clockG5 MAX_<strong>FPGA</strong>_SSEL 2.5-V <strong>FPGA</strong> to MAX V SPI bus slave selectA6 MAX_LOAD 2.5-V <strong>FPGA</strong> configuration active LEDM9 MAX_RESETN 2.5-V MAX V reset push buttonB10 MSEL0 2.5-V <strong>FPGA</strong> MSEL0 settingB3 MSEL1 2.5-V <strong>FPGA</strong> MSEL1 settingC10 MSEL2 2.5-V <strong>FPGA</strong> MSEL2 settingC12 MSEL3 2.5-V <strong>FPGA</strong> MSEL3 settingC6 MSEL4 2.5-V <strong>FPGA</strong> MSEL4 settingE10 OVERTEMP 2.5-V Temperature monitor fan enableC7 PCIE_JTAG_EN 2.5-V PCIe JTAG master enableNovember 2013 <strong>Altera</strong> Corporation <strong>Cyclone</strong> V <strong>SoC</strong> <strong>Development</strong> <strong>Board</strong><strong>Reference</strong> <strong>Manual</strong>