Formal Methods in Specification and Synthesis of Petri net ... - LSI

Formal Methods in Specification and Synthesis of Petri net ... - LSI

Formal Methods in Specification and Synthesis of Petri net ... - LSI

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

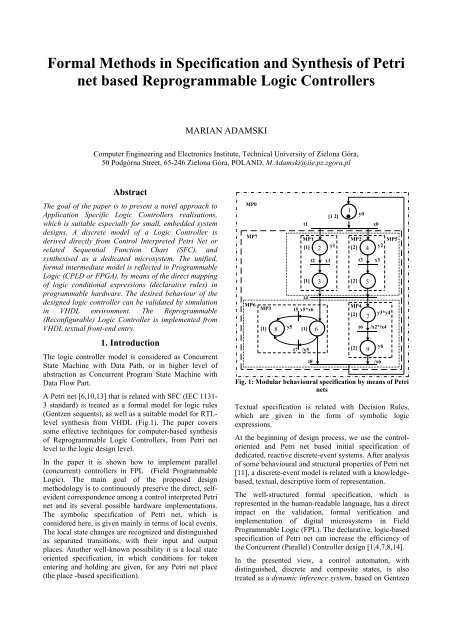

attached explicitly to the places, <strong>and</strong> implicitly to thetransitions <strong>and</strong> arcs as well as to the tokens [15]. The set<strong>of</strong> sub<strong>net</strong>s is partially ordered (Fig. 3, Fig. 4, Fig. 1). Thecoloured hierarchy relation tree (Fig.5) graphicallyrepresents the hierarchy <strong>and</strong> concurrency relationsamong sub<strong>net</strong>s. The Base Net MP0 is on the root <strong>of</strong> theFig. 4: First <strong>and</strong> second order macro<strong>net</strong>tree. It conta<strong>in</strong>s the double-macroplaces MP1-MP7,which st<strong>and</strong> for the hierarchically structured sub<strong>net</strong>s atthe lower level <strong>of</strong> hierarchy.Each double macroplace corresponds to a compoundoperation, which is itself a discrete sub-processdescribed by the doubled block. The colours [1] <strong>and</strong> [2]are used for dist<strong>in</strong>guish<strong>in</strong>g particular <strong>in</strong>tended sequentialprocesses, <strong>and</strong> cont<strong>in</strong>uously controll<strong>in</strong>g the place<strong>in</strong>variants (P-sub<strong>net</strong>s) <strong>and</strong> hierarchy tree dur<strong>in</strong>g thecomposition or reduction <strong>of</strong> the <strong>net</strong>.[1 2][1 2][1 2][1 2][1]t1t4t8P1MP11MP5MP6[1 2]MP5/Q1MP0/Q1 Q1[2][1 2]MP2[2]MP7MP3[1 2]MP6MP4P2 P3 P4 P5 P6 P8 P7 P9[1] [1] [2]Q1/Q2Q1Q2/Q2 Q2/Q2 /Q2 Q2Q2/Q3 Q3 /Q4 Q4 /Q3 Q3 /Q4 c[1][1][1]Fig. 5: Hierarchy treeThe <strong>Petri</strong> <strong>net</strong> (Figure 1) is hierarchically encoded bymeans <strong>of</strong> state variables Qi, i= 1,2,3,4. The symbols Qior /Qi, attached to the particular path, which is directedfrom the root to the leave, form the unique encod<strong>in</strong>gterm for the considered macroplace or place.3. Gentzen Sequent Logic<strong>Petri</strong> <strong>net</strong>s can be viewed as a formal model for logicrule-based specification (<strong>in</strong>terpretation structure).Transition rules are usually treated as production rulest1Q1/Q2[1]t4Q1Q2[1]t8[1 2] 1 /Q1MP1MP3[2][2][2][2]MP2MP4[2]Q1/Q2Q1Q2('if-then' non-procedural statements). The pr<strong>in</strong>cipaldesign language used to specify the Logic Controllerbehaviour <strong>in</strong> extended nested If-Then-Else form <strong>in</strong> ourdesign environment is Gentzen Sequent Logic [9].While formulae F may be regarded as a formalrepresentation <strong>of</strong> compound proposition, sequent |- F <strong>in</strong>our approach represents asserted statement. Sequentsmay also formally describe all general forms <strong>of</strong>conditional assertions, for example production rules: F |-G.The Gentzen formal system naturally simulates <strong>and</strong>records human-like reason<strong>in</strong>g. The synthesis, based onGentzen calculus, is treated as a formal symbolictransformation <strong>of</strong> the <strong>in</strong>itial set <strong>of</strong> sequents(specification) <strong>in</strong>to another equivalent set <strong>of</strong> sequents(implementation) [1,2]. The rules <strong>of</strong> <strong>in</strong>ference aredirectly based on Gentzen Logic or they are previouslyproven, so the implementations are correct byconstruction.4. <strong>Petri</strong> <strong>net</strong> specification <strong>in</strong> sequent logiclanguageThe Logic Controller is considered as an abstractreason<strong>in</strong>g system (rule based system) implemented <strong>in</strong>reconfigurable hardware. The mapp<strong>in</strong>g between <strong>in</strong>puts,outputs <strong>and</strong> local <strong>in</strong>ternal states <strong>of</strong> the system isdescribed <strong>in</strong> a formal manner by means <strong>of</strong> logic rules(represented as sequents) with some temporal operators,especially with operator 'next' @ [1,11,14]. Thecorrectness preserv<strong>in</strong>g synthesis, based on Gentzencalculus, is treated as a formal transformation <strong>of</strong> the<strong>in</strong>itial set <strong>of</strong> compound rules (<strong>Specification</strong>) <strong>in</strong>to anotherset <strong>of</strong> compound rules (Implementation).As a basic form <strong>of</strong> <strong>Petri</strong> <strong>net</strong> specification <strong>in</strong> decision ruleformat, the transition-oriented declarative specificationis presented. It describes all possible active events <strong>in</strong>concurrent state mach<strong>in</strong>e, when local states associated totransition change <strong>and</strong> the guard (Boolean label) is true.The presented form <strong>of</strong> description is very closed to wellknownproduction rules, whose are a pr<strong>in</strong>cipal forms <strong>of</strong><strong>Petri</strong> <strong>net</strong> description <strong>in</strong> LOGICIAN [1], CONPAR[8,10], PARIS [12], <strong>and</strong> PeNCAD [3,15].T1: P1 * X0 |-@P2 *@P4;T2: P2 * X1 |-@P3;T3: P4 * X3 |-@P5;T4: P3 * P5 |-@P6 * @P7;T5: P6 * X5*X6|-@P8;T6: P7 * /X2*/X4|-@P9;T7: P8 * /X5|-@P6;T8: P6 *P9 * /X6|-@P1;The static (level) Moore type outputs depend directly onplace mark<strong>in</strong>gs:P1 |- Y0; P2 |- Y1; P4 |- Y2;

P7 |- Y3 * Y4; P8 |- Y5; P9 |- Y6.The total discrete state space (Fig. 6), which <strong>in</strong>cludes 9global states, should be always consistent with all<strong>in</strong>tended local state changes:|-P1*/P2*/P3*/P4*/P5*/P6*/P7*/P8*/P9,/P1*P2*/P3*P4*/P5*/P6*/P7*/P8*/P9,…,/P1*/P2*/P3*/P4*/P5*/P6*P7*P8*/P9,/P1*/P2*/P3*/P4*/P5*/P6*/P7*P8*P9;y2y3 y4 y5p3*p4M3p7*p8p1p2*p4p3*p4M5t4M6t7 /x5p6*p7t5M7M2t2t3t6M1x1x3x0x5*x6/x2*/x4p6*p9Fig 6: Global states <strong>of</strong> logic controllerThe dynamic (pulse or registered) output signal can be<strong>in</strong>cluded directly to the decision rule, when it changes itsvalue together with the occurrence <strong>of</strong> transition. On theother h<strong>and</strong>, all changes <strong>of</strong> the place mak<strong>in</strong>g could be alsoexplicitly <strong>in</strong>cluded <strong>in</strong>to the sequent, for example:T1:P1*X0|-@P2*@P4*@/P1*/@Y0*@Y1*@Y2;T8: P6 *P9 * /X6|-@P1*@/P6*@/P9*@/Y6*@Y0The transition symbols can be explicitly <strong>in</strong>cluded <strong>in</strong>tothe formal textual <strong>Petri</strong> <strong>net</strong> specification:y0P1 * X0|-T1;T1|- @P2 *@P4;P2 * X1 |-T2;T2|-@P3;P4 * X3 |-T3;T3|- @P5;P3 * P5 |- T4;T4|- @P6 * @P7;P6 * X5*X6|- T5;T5|- @P8;P7 * /X2*/X4 |- T6T6|- @P9;P8 * /X5 |- T7;t1y1 y2t3x3x1p2*p5t2y3 y4t6M4y1y6/x2*/x4 x5*x6 M8t5p8*p9 y5 y6M9/x5 t7t8 /x6T7- @P6;P6 *P9 * /X6 |- T8;T8|- @P1;In some cases, like implementations with D flip-flops <strong>in</strong>FPGA, the declarative, place oriented specification istaken <strong>in</strong>to account. For example, the sequents which<strong>in</strong>clude explicit transition symbols {T1, T2, …, T8}, aftermapp<strong>in</strong>g the <strong>Petri</strong> <strong>net</strong> <strong>in</strong>to VHDL statements <strong>in</strong> M.Bolton’s style, give economical implementations <strong>in</strong>FPGA [8]Preconditions:Next mark<strong>in</strong>gs:P1 * X0 |- T1;P2 * X1 |- T2;…P6*P9*/X6 |- T8;T8+P1*/T1 |- @P1;T1+P2*/T2 |- @P2;…T8+P9 */T8 |- @P9;In this k<strong>in</strong>d <strong>of</strong> specification, if the next value <strong>of</strong> thetemporal variable, for example @P1, cannot be proved<strong>in</strong> the current mark<strong>in</strong>g (global state) as true, it isconsidered that it takes the value false.5. <strong>Petri</strong> Net <strong>and</strong> Logic DesignThe direct mapp<strong>in</strong>g <strong>of</strong> a <strong>Petri</strong> <strong>net</strong> <strong>in</strong>to FieldProgrammable Logic (FPL) is based on a self-evidentcorrespondence between a place <strong>and</strong> a clearly def<strong>in</strong>edbit-subset <strong>of</strong> a state register. The places <strong>of</strong> the <strong>Petri</strong> <strong>net</strong>are assigned to the particular flip-flops <strong>in</strong> the RegisterBlock. VHDL supports conditional-statement constructs,which can be used to describe <strong>Petri</strong> <strong>net</strong>. The proper localstate assignment (encod<strong>in</strong>g) makes it possible to map agiven Interpreted <strong>Petri</strong> <strong>net</strong> directly <strong>in</strong>to FPGA or CPLDwithout its transformation <strong>in</strong>to an equivalent global StateMach<strong>in</strong>e.The simplest technique for <strong>Petri</strong> <strong>net</strong> place encod<strong>in</strong>g is touse one-to-one mapp<strong>in</strong>g <strong>of</strong> places onto flip-flops <strong>in</strong> thestyle <strong>of</strong> a one-hot state assignment. In that case, a name<strong>of</strong> the place becomes also a name <strong>of</strong> the related flip-flop.The flip-flop is set <strong>in</strong>to 1 if <strong>and</strong> only if the particularplace holds the token. Some <strong>of</strong> the recent developments<strong>in</strong>volv<strong>in</strong>g modell<strong>in</strong>g <strong>and</strong> analysis such constructs <strong>in</strong>VHDL were reported, for example <strong>in</strong> [2,3,8,10,15].In general, places after encod<strong>in</strong>g are dist<strong>in</strong>guished byconjunctions, which are formed from state variablesfrom the set {Q1, Q2, ... , Qk}. The local states, whichare active simultaneously, have non-orthogonal codes.They are represented by places hold<strong>in</strong>g the tokensconcurrently <strong>and</strong> belong<strong>in</strong>g to the same vertex from theimplicitly or explicitly given reachability graph <strong>of</strong> Petr<strong>in</strong>et. The local states, which belong to the different, butsometimes overlapp<strong>in</strong>g sequential processes (P<strong>in</strong>variants,SM-components) have orthogonal codes. One

ecommended particular method <strong>of</strong> place encod<strong>in</strong>g isbased on hierarchical decomposition <strong>of</strong> the <strong>net</strong> (Figure 2,Figure 3). The result <strong>of</strong> an efficient heuristic hierarchicallocal state assignment [Q1, Q2, Q3, Q4] is asfollows:P1 = 0 - - -P1 = /Q1P2 = 1 0 0 *P2= Q1*/Q2*/Q3P3 = 1 0 1 *P3= Q1*/Q2*Q3P4 = 1 0 * 0P4= Q1*/Q2*/Q4P5 = 1 0 * 1P5= Q1*/Q2*Q4P6 = 1 1 0 *P6= Q1*Q2*/Q3P7 = 1 1 * 0P7= Q1*Q2*/Q4P8 = 1 1 1 *P8= Q1*Q2*Q3P9 = 1 1 * 1P9= Q1*Q2*Q4The global state encod<strong>in</strong>g is correct if all vertices <strong>of</strong> thereachability graph have different codes. The total code <strong>of</strong>the reachability graph vertex would be obta<strong>in</strong>ed bymerg<strong>in</strong>g the codes <strong>of</strong> the simultaneously marked places.The code <strong>of</strong> the particular place or macroplace isrepresented by means <strong>of</strong> the vector composed from {0, 1,- , *} or it is given as a related Boolean term. Thesymbols 0, 1, - ('don't care') have the usual mean<strong>in</strong>gs,but the symbol * <strong>in</strong> vector denotes 'explicitly don'tknow' (0 or 1, but not 'don't care').For several practical applications it is recommended tomanipulate with Boolean expressions (product terms), <strong>in</strong>which the symbols <strong>of</strong> places are substituted by encod<strong>in</strong>gconjunctions, for example:T1: /Q1 * X0|-@Q1*@/Q2*@/Q3*@/Q4;T2: Q1*/Q2*/Q3* X1 |-@Q1*@/Q2*@Q3;T3: Q1*/Q2*/Q4* X3 |-@Q1*@/Q2*@Q4;T4: Q1*/Q2*Q3*Q4 |-@Q1*@Q2*@/Q3 *@/Q4;T5: Q1*Q2*/Q3*X5*X6|-@Q1*@Q2*@Q3;T6: Q1*Q2*/Q4*/X2*/X4|-@Q1*@Q2*@Q4;T7: Q1*Q2*Q3*/X5|-@Q1*@Q2*@/Q3;T8: Q1*Q2*/Q3*Q4*/X6|-@Q1;The simplified sequent specification, planned forimplementations based on the state register with JK flipflops,on the right sides does not conta<strong>in</strong> signals, whichconserve their values dur<strong>in</strong>g the occurrences <strong>of</strong>transitions:T1: /Q1 * X0|-@Q1*@/Q2*@/Q3*@/Q4;T2: Q1*/Q2*/Q3* X1 |-@Q3;T3: Q1*/Q2*/Q4* X3 |-@Q4;T4: Q1*/Q2*Q3*Q4 |-@Q2*@/Q3 *@/Q4;T5: Q1*Q2*/Q3*X5*X6|-@Q3;T6: Q1*Q2*/Q4*/X2*/X4|-@Q4;T7: Q1*Q2*Q3*/X5|-@/Q3;T8: Q1*Q2*/Q3*Q4*/X6|-@/Q1;For Field Programmable Logic with JK flip flops,symbols @Qi can be replaced by J_Qi <strong>and</strong> symbols@/Qi respectively by K_Qi.6. Rapid modell<strong>in</strong>g <strong>and</strong> synthesis withVHDLA particular form <strong>of</strong> place-based rules describesseparately the conditions for mark<strong>in</strong>g <strong>and</strong> clear<strong>in</strong>g all theconsidered places. The condition for the new mark<strong>in</strong>g <strong>of</strong>place P1 is described as follows:Asserted that if P6 <strong>and</strong> P9 <strong>and</strong> not X6 then next P1;|- P6*P9*/X6-> @P1;Place P1 holds the token if it is marked <strong>and</strong> guard relatedwith its output transition is false:Asserted that if P1 <strong>and</strong> not X0 then next P1;|- P1*/X0 -> @P1;After the simple formal manipulations two separatedrules can be merged <strong>in</strong>to the one statementAsserted that if P6 <strong>and</strong> P9 <strong>and</strong> not X6 or P1 <strong>and</strong>not X0 then next P1;|- P6*P9*/X6+ P1*/X0 -> @P1;Tak<strong>in</strong>g as an example output Y0, which is active if <strong>and</strong>only if the place P1 holds the token, we obta<strong>in</strong>:Asserted that if P1 then Y1 else not Y1;|-(P1-> Y1)*(/P1-. >/Y1)VHDL supports conditional-statement constructs, whichcan be used to describe <strong>Petri</strong> <strong>net</strong>-based Concurrent StateMach<strong>in</strong>e implementations. As an example only a part <strong>of</strong><strong>Petri</strong> Net specification <strong>in</strong> VHDL is presented:Architecture reactor_desc <strong>of</strong> reactor issignal P : std_logic_vector(1 to 9);beg<strong>in</strong>--Mark<strong>in</strong>g Places <strong>and</strong> Fir<strong>in</strong>g TransitionsP1: process (clk, reset)beg<strong>in</strong>if reset='1' then P(1)

eg<strong>in</strong>if reset='1' then P(2)