Chip Scale Review - October 2008

Chip Scale Review - October 2008

Chip Scale Review - October 2008

- No tags were found...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

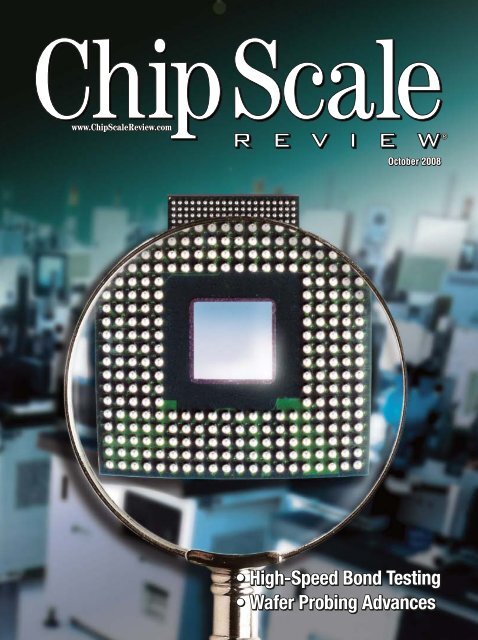

<strong>October</strong> <strong>2008</strong>• High-Speed Bond Testing• Wafer Probing Advances

CONTENTS<strong>October</strong> <strong>2008</strong>Volume 12, Number 7The international magazine for device and wafer-level test, assemblyand packaging that addresses high-density interconnection of microelectronicsICs, MEMS, RF/wireless, optoelectronic and other wafer-fabricated devicesfor the 21st Century.FEATURE ARTICLESInternational Directory of Wafer Probers and Probe Cards<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> Staff26THE COVERThis is <strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong>’s inspection issue.This issue’s cover graphically representsprobing and test.That conveniently ties in with the“Probe Mark Analysis—A Critical Windowon Actual Probe Card Performance” articleby Darren James, Product Manager,Rudolph Technologies Inc. Probe markanalysis provides a critical window on actualprobe performance, allowing engineersto optimize probing processes and realizesubstantial economic returns.The insightful “High-Speed Wire BondTesting: Understanding the Technology”article by Bob Sykes, Dage PrecisionIndustries, Ltd. follows with details on howto be certain that your wire bonding integrityis as intended. A comprehensive knowledgeof bond strength, force displacement andenergy measurement of solder ball bonds iscritical for the detection of brittle fracturefailures within semiconductor packages.PCA OTWafer Scrub EPCA & ScrubCenter PositioWafer Scrub StPCA NOTProbe Mark Analysis—A Critical Window 29on Actual Probe Card PerformanceDarren James, Rudolph Technologies Inc.Probe mark analysis provides a critical window on actual probeperformance, allowing engineers to optimize probing processes andrealize substantial economic returns. Systematic discrepancies betweenprobe card test data and actual on-wafer performance can be correctedto improve visibility of the probing process.International Directory of Failure Analysis/DefectInspection System Suppliers<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> Staff36High-Speed Bondtesting:42Understanding the TechnologyBob Sykes, Dage Precision Industries Ltd.Bond failures indicate loads on the bond and excessive strain rates.However, weak or poor quality bonds can fail even at low forces. Thekey is determining at what force and energy they fail. A comprehensiveknowledge of bond strength, force displacement and energy measurementof solder ball bonds is critical for the detection of brittle fracture failureswithin semiconductor packages.CONTINUED >>(Illustration for <strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> byDesign 2 Market) [design2marketinc.com]<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong>, at 7291 Coronado Dr., Suite 8, San Jose, CA 95129(ISSN 1526-1344), is published eight times a year, with issues inJanuary-February, March, April, May-June, July, August-September,<strong>October</strong> and November-December.Periodical postage paid at San Jose, Calif., and additional offices.POSTMASTER: Send address changes to <strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> magazine,7291 Coronado Dr., Suite 8, San Jose, CA 95129.<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ <strong>October</strong> <strong>2008</strong> ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com] 1

COMMENTARYNew DistinguishedEditorial Advisors Join<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong>By Terrence E. Thompson, Editor in Chief [tethompson@aol.com]and Kim Newman, Publisher and Sales Manager [csradv@aol.com]<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> is honored to announce the addition of two new distinguishedEditorial Advisory Board members: Lee Smith, Vice President of BusinessDevelopment at Amkor Technology Inc. [amkor.com] and Dr. Andy Mackie, ProductManager, Semiconductor Packaging Materials at Indium Corporation [indium.com].Both have extraordinary assembly and packaging insights that will help shape CSR’s editorialfocus as the magazine and the industries we serve move forward to face new challengesand opportunities.Their insights will help CSR better target emerging opportunity areas for those nowprimarily involved in chip (the many devices including ICs) and wafer-level assembly/packaging(WLP) operations. We will, as always, thoroughly address today’s mainstream assemblyand packaging processes and materials to address immediate challenges.Of course, virtually every technology product or service we use today is microelectronicscentric.Ongoing innovations in device and wafer-level test, assembly and packaging areessential to keep up with the ITRS roadmap growth goals anticipated for microelectronicsinterconnects and packaging innovations as well as related emerging technologies includingMEMS/MOEMS and nanotech where IC manufacturing expertise can bring aboutdesired change and progress more quickly.Our own bias is that materials science and engineering are crucial areas that will leadthe way in making future technology advancements both possible and affordable. Theinevitable challenges that high-tech companies will face as IC thin films become ever thinnerand feature sizes continue to shrink are both obvious and subtle.Basic materials behavior changes as bulk sizes decrease and quantum mechanics effectscome into play. In most cases, assembly process temperatures become much more critical.Since many lead-free solders require higher reflow temperatures, more users may be evaluatingsolders more closely than ever.Process equipment is indeed crucial for packaging success. However, most advances inequipment are evolutionary although steady streams of new machines make the processingmore efficient and cost effective.Andy’s insights on advanced materials will help guide our editorial direction. Lee’s insightson assembly and packaging processes as well as the requisite production hardware areinvaluable. Both are well-known and respected industry experts with perspectives thatwill provide guidance for CSR’s ongoing editorial direction. Both will author CSR articlesin 2009 so watch for them! i2<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ <strong>October</strong> <strong>2008</strong> ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com]STAFFVOLUME 12, NUMBER 7The international magazine for device and waferleveltest, assembly and packaging that addresseshigh-density interconnection of microelectronics ICs,MEMS, RF/wireless, optoelectronic and other waferfabricateddevices for the 21st century.Kim Newman Publisher/Sales Manager7291 Coronado Dr., Ste. 8, San Jose, CA 95129b 1.408.996.7016 > 1.408.996.7871csradv@aol.comTerrence Thompson Editor in Chief2303 Randall Rd. #140, Carpentersville, IL 60110b 1.847.515.1255tethompson@aol.comMartin Kraft Technical Editormartykraft@aol.comSteve Berry Contributing Editorb 1.408.369.7000 > 1.408.369.8021saberry@electronictrendpubs.comDr. Tom Di Stefano Contributing Editorb 1.408.399.4501 > 1.408.395.0448tom@centipedesystems.comPaul M. Sakamoto Contributing Editor–Testpaul.sakamoto@comcast.comSandra Winkler Contributing Editorb 1.408.369.7000 > 1.408.369.8021slwinkler@electronictrendpubs.comThe Official Publication of the WLCSP ForumSUBSCRIPTION INQUIRIESJudy Levin <strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong>7291 Coronado Dr., Ste. 8, San Jose, CA 95129b 1.408.996.7016 > 1.408.996.7871csrsubs@chipscalereview.comADVERTISING PRODUCTIONINQUIRIES AND REPRINTSKim Newman7291 Coronado Dr., Ste. 8, San Jose, CA 95129b 1.408.996.7016 > 1.408.996.7871csradv@aol.comADVISORSDr. Tom Di Stefano Centipede SystemsLee Smith Amkor Technology Inc.Dr. Andy C. Mackie Indium CorporationCharles R. Harper Technology Seminars Inc.Dr. Guna Selvaduray San Jose State UniversityDr. Thorsten Teutsch Pac Tech USADr. David Tuckerman Tessera TechnologiesProfessor C.P. Wong Georgia TechCopyright © <strong>2008</strong> by Gene Selven & Associates Inc.<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> (ISSN 1526-1344) is a registered trademarkof Gene Selven & Associates Inc. Publishing headquarters arelocated at 7291 Coronado Drive, Suite 8, San Jose, CA 95129.All rights reserved.<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> is published eight times a year.Subscriptions in the U.S. are available without charge toqualified individuals in the electronics industry. Subscriptionsoutside the U.S. (eight issues) by airmail are $60 per year toCanada or $60 to other countries. In the U.S., subscriptionsby first class mail are $40 per year.

CONTENTSFEATURED DEPARTMENTWLCSP Forum: Trends in Wafer Level 22<strong>Chip</strong> <strong>Scale</strong> PackagingL. Nguyen, National Semiconductor Corp.;T. Tessier, Flip <strong>Chip</strong> International; H. Theuss, Infineon;R. Haas and K. Baker, California Micro Devices“The best package is no package” is a simple butmeaningful description of the basic idea to fabricatea complete electrical component on wafer level prior to dicing.In a Wafer Level <strong>Chip</strong> <strong>Scale</strong> Package (WLCSP), all packaging andinterconnection are done using wafer processes. Thus, cost-intensivesequential processes like die and wirebonding are replaced. WLCSPs areshipped after electrical testing and mounted directly onto a PCB usingstandard pick and place technology, preferably without underfill.DEPARTMENTSCommentary Terrence Thompson and Kim NewmanNew Distinguished Editorial Advisors Join <strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong>Assembly Lines Terrence ThompsonMartin Kraft Joins the <strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> Editorial Staff; 5th Annual IWLPCInside Patents A. Jason Mirabito and Carol PetersWafer Probe Interconnect System-Resolving Wafer Warp IssuesIndustry NewsCalendar2681618If you’re involved in IC or MEMS packaging, thisyear’s IWLPC is the conference you should not miss!SA N JOSE, CALIFO R NIA<strong>October</strong> 13-16, <strong>2008</strong>San Jose, CaliforniaCo-presented byElectronic Trends Steve Berry and Sandra WinklerIC Applications—Solid Volume Increases, More Growth to ComeWhat’s New!Product Showcase (Advertisement)213446O C T O B E R 1 3-1 6, 2 0 0 8Visit IWLPC.COM for detailsAd Index/More News/Sales Offices48<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ <strong>October</strong> <strong>2008</strong> ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com] 3

SSEC Single WaferSingle Wafer ProcessingSSEC Systems are configurable in strip, etch and clean process stations withup to 12 stations in a system. In a Class 1 mini-environment, dual SCARArobotics can operate in any sequence to any station according to recipeselection. SSEC’s applications laboratory will assist you in configuring a toolaround your exact process and manufacturing requirements.Come visit SSEC and learn what is new in single wafer processing.wet processingClean99% Particle Removal Efficiency atthe 88 nm, 65 nm, and 45 nm NodesDual SCARA robotics can addressall stations in any sequence.Solvent StripImmersion and SingleWafer ProcessingSSEC 33011 Processing StationSSEC 3303/43-4 Processing StationsEtchUniform, Selective Etching onMultiple Process LevelsSSEC 33077 Processing StationsSSEC ComplianceSEMI S2-0706E SafetySEMI S8-0705E ErgonomicsFM 4910 MaterialsSECS GEM CCS 200 & 300CE MarkedETL ListedSSEC 331010 Processing StationsCoat/DevelopPhotolithography Clusterswww.ssecusa.comPhone: 215-328-0700

US # 6,539,952High Velocity Scrub Single Wafer Megasonic Scrub Rotary PVA Brush ScrubDouble-sided PVA BrushFor single-or double-sided particle clean, SSEC systems can be configured exactly to your cleaning requirements. Using dilute chemistries,such as SC-1 1:1:300, SSEC cleaning processors have 99% particle removal efficiency at the 88 nm, 65nm, and 45 nm nodes.High Pressure Flow ControlPressureSolvent Immersion High Pressure Spray High Pressure Needle DispenseTimeUsing only milliliters of solvent per wafer, SSEC solvent processors combine batch immersion and single wafer spray technology inone SEMI ® safety compliant, dry-in /dry-out system. High pressure sprays are entirely under closed-loop control for flow, temperature,and dispense arm motions.Ti EtchBackside/Bevel CleaningStream Flow EtchSpray EtchAl EtchCu EtchSingle Wafer Wet Etch with PC Program Control over Flow Rate, Temperature and Chemical Blending by recipe with per wafer selectivity. SSEC’spatent pending Chemical Collection System is over 90% effective for both single side and double sided processing. Each Wafer is processed underthe careful watch of a color CCD camera for adaptive process control with SSEC’s WaferChek System.Spin CoatingHot Plate Bake ProcessingMulti Size Hot PlateSpray DevelopCoat and Develop processors are configured to your exact production requirements, whether for double sided MEMs Coating or Thick ResistProcessing. With SSEC’s Vision Driven Wafer Alignment, Coat/Develop processors can change wafer sizes with only a PC recipe change- nohardware tooling changes. All Systems are fully robotic enabling recipe driven sequencing operation.3300

ASSEMBLY LINESMartin Kraft Joins the <strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> Editorial StaffBy Terrence Thompson, Editor in Chief [tethompson@aol.com]We enthusiastically welcomemy friend and colleaguefrom earlier publishingdays Martin (Marty) Kraft. He hasjoined the <strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> editorialstaff as Technical Editor. Marty has 25years of technical writing and editingexperience. Previously, he was theTechnical Editor for Circuits Assemblymagazine. Currently, he is the managingeditor for an international mechanicalengineering association. He has a MS intechnical communication and a BA injournalism.He’s already hard at work behind thescenes! He will make CSR a better magazinegoing forward.5th Annual IWLPC, Biggerand Better Than Ever!The 5th InternationalConference on Wafer-Level Packaging(IWLPC) with its 3DStacking focus is on track with its largerthan ever technical program, timely paneldiscussions and companion exhibitsthat address the products and servicesneeded by those in microelectronics,nanotech and emerging technologiesincluding photovoltaic production.SA N JOSE, CALIFO R NIAO C T O B E R 1 3-1 6, 2 0 0 8Batch or Discrete ManufacturingThis conference is all about how toselect and implement the “best” IC andwafer-level packaging (WLP) optionsfor a given application. For industryContinued on page 11 >>6<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ <strong>October</strong> <strong>2008</strong> ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com]

INSIDE PATENTSWafer Probe Interconnect System—Resolving Wafer Warp IssuesBy A. Jason Mirabito [jmirabito@mintz.com] andCarol Peters [cpeters@mintz.com], Contributing Legal Editors,Mintz Levin Cohn Ferris Glovsky and Popeo P.C., Boston [mintz.com]Our column discusses theimprovements that U.S.Patent No. 7,382,143, issuedon June 3, <strong>2008</strong> and assigned on its faceto Centipede Systems, offers to resolveproblems related to wafer warp. In thepast, integrated circuit chips (“ICs”)were tested once the chips had beendiced and cut away from the wafer.Today, with WLP, it is becoming morecommon to test individual ICs whilethey remain on the wafer.Testing chips on the wafer allows theoperator to determine which wafersmeet specific electrical and functionaltests and to discard defective ICs beforethey are diced and mounted into semiconductorpackages. The problem thatoccurs with such testing is that, as semiconductorwafers are more and moredense, the geometries of ICs shrink andit becomes consequently more difficultto probe each of the desired pads on anindividual IC.Making Better Contact Is CrucialThe ‘143 patent describes a specificproblem with prior art probes in thatprobe heads under a load do not makeuniform contacts with the wafer due towarping of the wafer probe head.Consequently, incorrect or inaccuratetest results occur due to the incorrect orinadequate contacts, and this can causethe rejection of ICs that are good.According to the ‘143 patent, animprovement is offered by mounting a8<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ <strong>October</strong> <strong>2008</strong> ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com]

number of posts on a rigid supportblock that inhibits warping of a substrateunder load. As illustrated in the figure, awafer probe interconnection apparatusis disclosed that includes pliant probetips a mounted on a number of dielectricsubstrates b. The substrates,according to the patent, could be fabricatedin different sizes in order toaccommodate a particular wafer beingtested. The wafer probe interconnectapparatus includes a plurality of dielectricsubstrates arrayed in a two-dimensionalpattern that may cover the surfaceof an entire wafer.The substrates may be fabricatedfrom alumina sheet material or otherdielectric materials, such as aluminumnitrate. Each substrate b is supportedby spring posts c. Each spring postcompresses, or is allowed to compress,to permiteach of thesubstrates bto align parallelto theplane of thewafer beingprobed. Eachof the springposts c holdeach of thesubstrates b above a support block d.The support block is, according to thepatent, selected for material propertiesincluding rigidity. The spring posts alsoare designed to be sufficiently pliantto allow for thermal expansion of thedielectric substrate b without thedielectric substrate being warped. Inaddition, flex cables e electrically coupleprobes a at contact terminals f.Improvements are obtained by mounting a number of posts on a rigid support blockthat inhibits the warping of a substrate under load.Finally, flat springs g are attached to amounting ring h and maintain tensionbetween support block d and levelingplate i.The ‘143 patent thus discloses a wafertesting apparatus that allows testing of anumber of uncut ICs on a semiconductorwafer in such a way that the probe tipsuniformly contact the contact surfaceson the undiced ICs. iFOR MICROWAVE DEVICE SOLDERING LOOK TOSikama InternationalThe World Leader in High Density Package Reflow OvensSikama International, Inc. • www.sikama.com<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ <strong>October</strong> <strong>2008</strong> ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com] 9

MicrobondDocfish –same behaviora billion timesMaterials for WaferBumping ApplicationsPlease visit us atIMAPS ProvidenceBooth 52201883 www.aim.deUmicore AG & Co. KGMicrobond - EPMHanau · Singaporewww.microbond.euUltrafinepitchSolder PastesWatersoluble andNo Clean Flux SeriesSoft Solder Spheresfrom Duksan Hi-MetalA perfect fit !

ASSEMBLY LINESContinued from page 6 >>veterans, it’s obvious that any singlegiven packaging approach does not workfor everything. There’s a reason why wehave competing processes—they all workwell for some applications but not for all.The conference explores many processalternatives of interest to attendees.WLP itself has many subsets and thevariants are increasing. The WLP appealis obvious—it is batch (parallel) manufacturingprocess with enormous potentialeconomies of scale. WLP can redistributepads (RDL), bump, encapsulate,dice, etc., to produce a packaged deviceready for mounting on a PWB—or in a2D/3D SiP or in a PoP stack.High-Volume CustomizationSystem in Package (SiP) is a collectionof electrically interconnected andmechanically secured “chips” in 2Dand/or 3D arrangements on/in somesort of HDI (high-density interconnect)substrate. SiP can be quickly implementedfor fast-changing OEM products withmarket-driven quarterly, or even morefrequent, updates.System on <strong>Chip</strong> (SoC) is an elegantcollection of interconnected chipsformed on a wafer with an expensivemicroprocessor grade silicon wafer base.Potentially, SoC is an alternative to SiP.However, SoC design and fabricationusually are too slow for fast-changingOEM products with quarterly updates.However, SoC provides core functionalityfor some products including mobilephones and other high-volume productscan use SoCs in SiPs. If quick turnaroundsand the lowest possible costs are essential,SiP is probably a far better choice.Stack WLP-produced and/or standardpackages and you get PoP (Package-on-Package). With WLP, stacked wafers areoften thinned to minimize final packagethickness, essential for many low-profileform factor products. TSV (through siliconvia) vertical interconnects withinthe wafer and for wafer-to-wafer or dieto-diestacks are made with either “viafirst” and “via last” philosophies. Whichis best? We’re waiting to see.As the IWLPC speakers and instructorswill suggest, the “best” option is whatworks for you within your budget andmeets performance and reliability criteria!Affordable and ReliableWe need economies of scale, assembly/packaging schemes with a high probabilityof working right the first time, flexibilityContinued on page 13 >><strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ <strong>October</strong> <strong>2008</strong> ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com] 11

Automatic In-line Wire Bond InspectionHigh accuracy inspectionof wire bond connectionsViscom’s in-line automatic opticalinspection (AOI) system S6053BOguarantees reliable defect detectionon typical bond connections. Withits modular camera technologyand standard resolutions of 8.3μm or5.6μm, the system inspects over1,000 aluminum or gold wireconnections per minute as well asSMD components, solder joints anddie damages. For wire diameters downto 17μm, the new VHR cameramodule with resolutions < 3μm isnow available. Viscom’s field-provenS6053BO AOI system is able toreliably inspect features such asball or wedge position andcompleteness, loop-height, spacing,shape and geometry and ensureshighest quality in zero defectenvironments.See us atIMAPS <strong>2008</strong>,November 4-6,Rhode Island

ASSEMBLY LINESContinued from page 11 >>to handle constant product updates/innovation and the infrastructureto make it happen. Today’s mainstream technologyproducts are “microelectronics centric,” i.e., they don’t workwithout electronics for I/O control and electrical power.What, exactly, are you packaging, and how is what youmust ask yourself? So why not keep packaging one chip at atime? Or batch package chips? Or package multiple chips? Orbetter yet—any and all as needed.Don’t miss the conference since it will help answer the manycrucial questions that those making the most sophisticatedpackages in the world! [iwlpc.com] or [smta.org]DuPont Electronic TechnologiesExpands WLP PortfolioResearch Triangle Park, N.C.—DuPont Electronic Technologieshas expanded its focus on materials for wafer level packagingand emerging 3D and through silicon via (TSV) semiconductorpackaging including copper pillar and solder bump applications.DuPont is developing new products, new partnerships and isexpanding its technical capability to support the growingglobal demand for advanced materials in the semiconductorindustry.“Our goal is to reduce customer cycle time for new processdevelopment and implementation by offering innovative, testedand compatible material sets based on technology from acrossDuPont as well as in cooperation with our strategic industrypartners,” said Mats J. Ehlin, global business manage, DuPontWafer Level Packaging. “The semiconductor packaging marketis recognized as a strategic area of growth within DuPont, andwe’re excited about expanding our portfolio of WLP solutionsto enable new advanced packaging designs.”[www2.dupont.com/packaging_and_circuits/en_us/index.html]Report States Manufacturing Capacity for Thin-Film and Organic PV to Reach 29 GWp by 2015Glen Allen, Va.—Manufacturing capacity for thin-film andorganic photovoltaics is expected to grow from approximately2 GWp (Gigawatts at peak sunlight) this year to 29 GWp by2015 according to a new report from NanoMarkets,anindustry analyst firm based here. At the same time, the valueof manufacturing equipment purchased by thin-film PV (TFPV)and organic PV (OPV) firms will grow from $450 million in<strong>2008</strong> to $4.8 billion in 2015. These and other findings arefrom NanoMarkets’ new report, “The Future of Thin Filmand Organic Photovoltaics Manufacturing.”Continued on page 15 >><strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ <strong>October</strong> <strong>2008</strong> ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com] 13

ASSEMBLY LINESContinued from page 13 >>While First Solar will be hard to pass in the cadmium telluride (CdTe) sector, therace for dominance in the CIGS and OPV sectors has just begun. By 2015 these twosectors combined will account for 19 percent and 10 of aggregate capacity.Annual manufacturing equipment purchases by TFPV/OPV firms will reach over$1 billion in 2009, more than double this year. NanoMarkets projects that the marketfor TFPV/OPV equipment will flatten in 2010 as solar cell makers fully utilize thecapacity they have rapidly put in place since 2007 but resume growth and reach$4.8 billion in 2015. [nanomarkets.net]STATS <strong>Chip</strong>PAC Introduces Pre-Stacked PoP Solution,Includes 3D Package Assembly, Test And Reflow ProcessSingapore—STATS <strong>Chip</strong>PAC Ltd. introduced its Pre-Stacked Package-on-Package(PoP) that includes both a top and bottom PoP package that are assembled andtested separately, then stacked and reflowed together to produce a complete highperformance3D solution.The rapid adoption and growth of PoP, particularly in the mobile phone market,has led to a number of new top and bottom PoP packages being introduced. In astandard PoP process flow, the top and bottom PoP packages are separately assembled,tested and shipped to a surface mount technology (SMT) provider for final integration.When top and bottom PoP packages are stacked and reflowed together duringthe surface mount process, high reflow temperatures can cause warpage in both thetop and bottom PoP packages, resulting in yield loss.“Pre-Stacked PoP provides our customers with a new approach to integratingmultiple die and diverse technologies in a reduced footprint. The Pre-Stacked PoPassembly process is unique in that we added a reflow step to our full turnkey manufacturingflow to provide semiconductor companies with a pre-stacked, pre-testedsolution that can be delivered directly to their end customers. Pre-Stacked PoP canbe easily placed onto a printed circuit board through the same surface mount processas standard components,” said Dr. Han Byung Joon, Executive Vice President andChief Technology Officer, STATS <strong>Chip</strong>PAC. [statschippac.com]Whatareyourcurrentburn-insocketsmissing?Quik-Pak Acquires Aguila Technologies’ FC Assembly,Radiation Sensor and Laser Micromachining Business UnitsSan Diego, Calif.—Quik-Pak, a division of Delphon Industries, has acquiredAguila Technologies’ flip chip assembly, detector array processing, and laser micromachiningbusiness units. The acquisition is part of Quik-Pak’s ongoing effort toexpand its advanced packaging and assembly services.The acquisition, which includes key technical personnel and proprietary equipment,allows Quik-Pak to provide a full turnkey solution to support wafer backgrindingand dicing, the latest packaging technologies and advanced assembly services.“The new acquisition coupled with Quik-Pak’s current services will enable us tomore completely meet the increasing demands of our customers and facilitate fastertime-to-market for their newproducts,” says Steve Swendrowski,General Manager. [icproto.com] iDid You Know?<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> is now offered in a digitalformat with a powerful search engine!<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ <strong>October</strong> <strong>2008</strong> ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com] 15

INDUSTRY NEWSA First in All Integrated Nanowire Sensor CircuitryBerkeley, Calif.—Scientists at theU.S. Department of Energy’s LawrenceBerkeley National Laboratory and theUniversity of California at Berkeleyhave created the world’s first allintegratedsensor circuit based onnanowire arrays, combining lightsensors and electronics made ofdifferent crystalline materials. Theirmethod can be used to reproduceGlobal Low-CostWafer Bumping Services• Europe – USA – Asia • Quick-turn andmass-production Highly competitive,low-cost bumpingtechnology Exceptional qualitythrough high-levelexpertisePac Tech GmbHTel: +49 (0)3321/4495-100sales@pactech.dewww.pactech.dePac Tech USATel: 408-588-1925, ext. 202sales@pactech-usa.comwww.pactech-usa.comPac Tech Asia Sdn. Bhd.Tel: +60 (4) 6430 628sales@pactech-asia.comwww.pactech-asia.comNAGASE & CO., LTD.Tel: +81-3-5640-2282takahiro.okumura@nagase.co.jpwww.nagase.co.jpAvailable Processes Electroless Ni/Au under-bump metallization Ni/Au bump for ACF or NCP assembly Solder paste stencil printing Solder ball drop for wafer-level CSP Solder jet for micro-ball placement BGA and CSP reballing Wafer backside thinning and wafer dicingSpecial Features/Technologies Over 10 years experience U.S. Government Certified 4- to 12-inch wafer capability Wafer pad metallization: Al and Cu Solder alloys: eutectic SnPb37, lead-free,low-alpha, and AuSn Fluxless and contactless bumping for MEMSand optoelectronics Ni/Au interface for wire-bond applicationsThe leader in low-cost electroless wafer bumping.Artist’s impression of an integrated light sensorcircuit based on nanowire arrays. (Javey Group)numerous such devices with high uniformity.“Our integration of arrays of nanowiresthat perform separate functionsand are made of heterogeneous substances—anddoing this in a way thatcan be reproduced on a large scale in acontrolled way—is a first,” says Ali Javey,who led the research team. Javey is astaff scientist in Berkeley Lab’s MaterialsSciences Division (MSD) and an assistantprofessor in the Electrical Engineeringand Computer Sciences Department atUC Berkeley. He and his colleaguesreport their work in the August 1, <strong>2008</strong>edition of Proceedings of the NationalAcademy of Sciences (PNAS).“Our main objective is a route towardintegrated nanowire arrays that we canproduce on any substrate—even paper—and to reproduce them uniformly on alarge scale,” Javey says. “To do that, overthe past two years our group has developedmethods of printing nanowire arrays.After first growing the nanowires on adonor substrate, we transfer them toany desired substrate, including paperor plastic.”The Javey group has devised twoprinting methods, contact and roller.The roller method involves growingnanowires on the surface of a cylinderand rolling it across the applicationsubstrate, like painting with a paintroller. [lbl.gov]16<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ <strong>October</strong> <strong>2008</strong> ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com]

North American Semiconductor Equipment Industry August<strong>2008</strong> Book-to-Bill Ratio of 0.83, No Change from JulySEMI book-to-bill is a ratio of three-month moving averages of worldwide bookings and billings forNorth American-based semiconductor equipment manufacturers. Billings and bookings figures are inmillions of U.S. dollars.Billings Bookings Book-to-Bill(Three-month average)March <strong>2008</strong> 1,344.9 1,165.6 0.87April <strong>2008</strong> 1,337.3 1,090.3 0.82May <strong>2008</strong> 1,313.0 1,029.3 0.78June <strong>2008</strong> 1,159.8 934.2 0.81July <strong>2008</strong> (final) 1,077.2 889.0 0.83August <strong>2008</strong> (prelim.) 1,065.5 884.1 0.83(Source: SEMI, September <strong>2008</strong>)IncreasedSignalSpeedMore PowerLowInductanceSan Jose, Calif.—North America-basedmanufacturers of semiconductor equipmentposted $884 million in orders inAugust <strong>2008</strong> (three-month averagebasis) and a book-to-bill ratio of 0.83according to the August <strong>2008</strong> Book-to-Bill Report published by SEMI. Abook-to-bill of 0.83 means that $83worth of orders were received for every$100 of product billed for the month.The three-month average of worldwidebookings in August <strong>2008</strong> was $884million. The bookings figure is abouteven with the final July <strong>2008</strong> level of$889 million, and about 36 percent lessthan the $1.37 billion in orders postedin August 2007.The three-month average of worldwidebillings in August <strong>2008</strong> was $1.07billion. The billings figure is about onepercent less than the final July <strong>2008</strong>level of $1.08 billion, and almost 37 percentless than the August 2007 billingslevel of $1.68 billion.“As we approach the end of the thirdquarter, orders for semiconductor manufacturingequipment remain very weakcompared to 2006 and 2007 levels.” saidStanley T. Myers, president and CEO ofSEMI. “While there are indications ofresumed spending in 2009, current economicconditions, industry oversupplyand economic uncertainty have resultedin the lowest three month average orderlevel since 2003.”The data contained in this release wascompiled by David Powell Inc., an independentfinancial services firm, withoutaudit, from data submitted directly bythe participants. SEMI and David PowellInc. assume no responsibility for theaccuracy of the underlying data.The data are contained in a monthlyBook-to-Bill Report published by SEMI.The report tracks billings and bookingsworldwide of North American-headquarteredmanufacturers of equipmentused to manufacture semiconductordevices, not billings and bookings of thechips themselves. [semi.org]SUSS MicroTec Launches Next-Generation Manual Mask AlignerGarching, Germany—SUSS MicroTeclaunched the third generation of its MA/BA8, a manual mask and bond aligner thatoffers highest process flexibility includingsubmicron alignment and exposure opticsdedicated for thick resist exposure. It allowseasy and fast upgrades to emerging technologiessuch as UV-nano imprinting,microlens imprinting, UV-bonding andenhanced bond alignment. The MA/BA8Gen3 combines high resolution and lightuniformity with a precision alignmentcapability down to 0.25µm. [suss.com]StableResistanceHigherTemperaturesIncreasedStrokeReplaceablePins<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ <strong>October</strong> <strong>2008</strong> ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com] 17

INDUSTRY NEWSPac Tech’s Wafer Bumping Facility in Penang Up and Running,Their Advanced Packaging Symposium Exceeds ExpectationsPenang, Malaysia—Pac Tech Asia SDNBHD officially opened its wafer bumpingproduction facility in Penang onSeptember 18th followed by hosting aninternational Advanced PackagingSymposium on the 19th.The opening ceremonies includedremarks by the Chief Minister ofPenang, YAB Tuan Lim Guan Eng. Hewelcomed Pac Tech’s commitment tothe development of Penang’s fast growinghigh-tech companies.Dr. Elke Zakel, CEO of Pac Tech Group,opened the symposium and opened withThomas Oppert as session chair. She waspleased with the attendance, exceeding 150.E. Jan Vardaman, President and Founderof TechSearch International, opened withobservations on “Packaging Trends andRoadmaps.” Next, Terrence Thompsonof <strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> magazine covered“Picking The Right IC and Wafer PackagingOptions.”Dr. Thorsten Teutsch of Pac Tech USAwas the session chair for WLCSP and Flip<strong>Chip</strong>. Dr. Elke Zakel, President and CEOof Pac Tech Group addressed “A BriefHistory of (Electroless Ni/Au and) Flip<strong>Chip</strong>.” Then, Dr. Andrew Strandjord,Senior Manager Advanced Packaging atPac Tech-USA, covered “WLCSPProduction Using Electroless Ni/Au andWafer Level Solder Sphere Transfer.”Dr. Ephraim Suhir, Professor ofElectrical Engineering at UC Santa Cruz,described “Accelerated Life Testing andIts Role in Making a Device into aProduct.” The Emerging Technologiessession chair was Ghassem Azdasht.Amol S. Kirtikar, Intel Corp., addressed“Opportunities in MicroelectronicPackaging, Challenges & the Need forInnovation.” This was followed byKatsuyuki Mizuike, EngineeringManager at Nagase ChemteX Corp., whodescribed “Liquid Epoxy Encapsulantfor Wafer Level and 3D Packages.”Closing remarks by Dr. Elke Zakel,wrapped up the symposium.Pac Tech’s new wafer bumping productionfacility will process 300mmwafers with an initial capability of processing600,000 wafers per year. Thefacility will be equipped with the latestgeneration of equipment at supportingsemiconductor market requirements forlow cost wafer bumping and backendprocessing. [pactech.de]Gartner Celebrates 50th Anniversary of Working IC DemonstrationStamford, Conn.—Gartner vice presidentand distinguished analyst Jim Tully noted,“The development of the integrated circuit(IC) made possible great cost reductionsin electronics. This allowed the technologyto spread rapidly through all areas of society.Found in everything from memoriesand microprocessors to mobile phones,TVs, media players, navigation systems,games consoles, watches, cameras andcountless other items, ICs are so woveninto our lives that it would be hard toimagine a world without them.“Sales in ICs have been growing at about10 percent annually for the past severaldecades. Around $270 billion worth ofICs will be sold globally in <strong>2008</strong>.“The integrated circuit is the engine ofthe information age. It has been a catalystfor the democratization of knowledge andchanging global social structures. It facilitatesmass communication through mobilephones and large-scale access to informationand entertainment through theInternet. But how do we compare thesebenefits with the life-saving use of ICsin body scanners, pacemakers and othermedical systems? Or the development ofhearing aids that enhance people’s qualityof life? These benefits can’t be comparedbut we can be sure of one thing—the IChas benefited society in countless ways.”[gartner.com]TheSolutionH-Pin ®US Patent #7025602MaximizedPerformanceMadeAffordablewww.PlastronicsUSA.com800-582-5822<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ <strong>October</strong> <strong>2008</strong> ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com] 19

ELECTRONIC TRENDSIC Applications—Solid VolumeIncreases, More Growth To ComeBy Steve Berry, Contributing Editor [saberry@electronictrendpubs.com] andSandra Winkler, Contributing Editor [slwinkler@electronictrendpubs.com]The number of ICs shipped hit151 billion in 2007—a 10 percentincrease over 2006 and an astonishing120 percent increase since 2001.This represented an unprecedentedsixth consecutive year of double-digitunit growth. ETP forecasts that unitgrowth will continue to be robust. Thenumber of ICs shipped is expected toexceed 260 billion in 2012.Where are all these ICs used, and whatare the implications of this volume increasefor the IC packaging industry? Figure 1 summarizesthe IC market by five applicationsegments—computer, communications,consumer, industrial, and transportation.The computer market segment consistsof PCs (desktop and notebook),servers, workstations, storage systems,monitors, printers, PDAs, and a host ofother commercial office and retailequipment. Accounting for just fewerthan 50 percent of total IC revenue, thecomputer market is more than twice thesize of its closest rival, the communicationsmarket. PCs remain the strongestdriver of the overall computer market.Price Wars Flatten RevenuesWith a continued price war between Inteland AMD and a price collapse in the DRAMmarket, IC revenue from the computermarket dropped about 1 percent in 2007,even though IC unit shipments grew byover 8 percent. IC revenue from thecomputer market is likely to be flat in <strong>2008</strong>,with positive revenue growth expectedto resume in 2009.The communications market consistsof cellular handsets, cellular infrastructure,other phones, enterpriseLAN equipment, wireless LAN equipment,DSL and cable modems, PBXsand other customer premises equipment(CPE), carrier-class equipment,and a host of other equipment—such as emergency-services radios andcommunications satellites. Cellularhandsets have become the main driver ofthe communications industry, with overone billion handsets manufactured in 2007.As a source of semiconductor industryrevenue, the communications segment isthe second largest of the five segmentsof the IC market. However, IC revenuefrom the communications market hashad three consecutive years of veryunimpressive growth. ETP anticipatesthat communications IC revenue will seeimproved growth in the coming years,as IC producers are better able to holdthe line against further price declines.Digital TVs, Flat Displays Drive RevenuesThe consumer market segment consistsof televisions, set-top boxes, DVD playersand recorders, audio systems, console videogames, camcorders, digital cameras, personalnavigation devices, memory cards, appliances,and an almost bewildering arrayof miscellaneous products. The conversionto digital televisions—as well as thechange from CRT-based televisions toLCD- and plasma-based units—is drivingmuch of the IC unit and revenueincreases in the consumer IC market.TransportationIndustrialConsumerCommunicationsComputerIC Units by Application Segment201220070 20,000 40,000 60,000 80,000 100,000ICs (Million)Consumer IC units and revenue haveboth grown nearly 150 percent since 2001,and consumer IC revenue will likelyexceed communications IC revenue in2010. As a result, the consumer IC markethas become a subject of intenseinterest to semiconductor companies.The remaining segments of the ICmarket—industrial (including medical)and transportation (including defense)—contain an almost infinite variety ofmostly low-volume products. Whilethese markets continue to grow, thatgrowth is relatively small compared tothat seen in the computer, communications,and consumer IC markets.Plan Ahead for Growth and ChangeAs the IC market grows from 151 billionunits in 2007 to a projected 260 plusbillion units in 2012, the IC packagingindustry must be prepared to worktogether to keep pace with the expectedgrowth, as well as to meet customerrequirements for even more diversepackage types than exist today. i<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ August/September <strong>2008</strong> ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com]21

Trends in Wafer Level <strong>Chip</strong> <strong>Scale</strong> PackagingBy L. Nguyen, National Semiconductor Corp.; T. Tessier, Flip <strong>Chip</strong> International; H. Theuss, Infineon;R. Haas and K. Baker, California Micro DevicesT“ he best package is no package”is a simple but meaningfuldescription of the basic ideato fabricate a complete electrical componenton wafer level prior to dicing.In a Wafer Level <strong>Chip</strong> <strong>Scale</strong> Package(WLCSP), all packaging and interconnectionare done using wafer processes.Thus, cost-intensive sequential processeslike die and wirebonding are replaced.WLCSPs are shipped after electricaltesting and mounted directly onto aPCB using standard pick & place technology,preferably without underfill.Basic manufacturing is typically doneby dropping a preformed solder sphereonto an under bump metallization(UBM), which ensures electrical andmechanical contact of the solder ballsand simultaneously acts as a diffusionbarrier. Implementation of redistributionlayers expands the flexibility of the simpleBump on Pad versions even further.The applicability of WLCSPs boilsdown to the question: “How many solderballs can be placed underneath thechip and still satisfy requirements onease of end-user assembly, board levelreliability, PCB routing, and cost constraints?”Today, devices like analog,power management, integrated passivesand discretes with less than 25 I/Osclearly dominate the market. However,other specific applications take advantageof wafer level packaging, amongthem memory devices, power amplifiers,image sensors and controllers.Figure 1 depicts the breakdown ofWLCSP adoption in consumer marketsin 2007, and shows the growth projectedFigure 1. Breakdown of the various consumer markets using WLCSPs in 2007, and anticipated growthover a five-year span. (Prismark)by 2012. Today, wafer level packaging ina broader sense is not strictly limited tomanufacturing processes on semiconductorwafers. But it now includes fanoutapproaches (e.g., embedded waferlevel technologies) and various kinds ofstacking and SiP technologies.To get a status of WLCSP technology,the WLCSP Forum conducted an industry-widesurvey during the Spring andSummer of <strong>2008</strong>. The survey’s goal wasto establish a more comprehensive viewof WLCSP technologies, especially inthe area of reliability requirements. Thesurvey had two basic sections. Part 1covered questions on package form factor,bump count, solder alloy, preferredPCB finish, and need for underfill. Part2 dealt with qualification requirementsand criteria for WLCSP products.Technology Status ReportThe response from the Forum’s firstsurvey on the adoption of WLCSPs inthe industry and future trends wassomewhat disappointing with only 22companies responding. However, theresults that were gathered confirmedWLCSP Forum members’ impressionsrelated to current and future WLCSPtrends. Of the companies that participatedin the survey, 54% were integrateddevice manufacturers, 32% were fablessFigure 2. WLCSP with 10 x 10 full array bumpconfiguration. (Cambridge Silicon Radio)22<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ <strong>October</strong> <strong>2008</strong> ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com]

Table 1. Wafer Level and Board LevelQualification Criteria for WLCSPsCriteria% of RespondentsWafer Level Qual RequirementsMSL Level 1 Conditions 93%Autoclave Testing96 hours 36%168 hours 64%High Temperature Storage150°C for 1008 hours 93%Other Conditions 7%Shear TestingLow-Speed Shear Testing 85%High-Speed Shear Testing 25%Board Level Reliability TestingDrop Testing 90%JEDEC Drop Test Methodology 80%Other Drop Test Standard 20%Bend Testing 83%JEDEC Bend Test Methodology 88%Other Bend Test Standard 12%Temperature CyclingTemperature Profiles-40° to 125°C 78%-65° to 150°C 16%Other 6%Number of Cycles Required500 cycles 31%1000 cycles 58%1500 cycles 11%High Temperature Operating Life150°C / 504 hours 79%Other Conditions 21%semiconductor companies, and 14%were OEMs.Although only 55% of respondentswere currently using WLCSPs, allrespondents expected to be providing orusing WLCSPs before the end of 2009.Of those respondents who were activelyusing WLCSP technologies today, 36%were using 150 mm wafers, 45% wereusing 200 mm wafers, and 27% wereusing 300 mm wafers.These results confirmed a migrationof devices in WLCSP formats to largerwafer sizes including 300 mm. This trendis directly attributable to the need fordevices in WLCSP formats to leveragethe most advanced device technologies.WLCSP bump pitches of 0.5 mmremain the most common format,with 70% of currentWLCSP users working at thatpackage pitch. Sixty percent ofthe respondents are currentlyusing 0.4 mm pitch WLCSPs inproduction, with all respondentsexpecting to be using 0.4 mmWLCSPs within the next twoyears. Only 32% of respondentsare currently using or developing0.3 mm pitch WLCSP offerings.Due to the surface mountassembly limitations and constraintsof end users, the adoptionof 0.3 mm pitch WLCSPs isexpected to be gradual.Three main categories ofWLCSP bump structures arecommonly used in the industry:Bump on Pad, Repassivation andRedistributed (RDL) WLCSPs.The survey results indicated that41% of respondents are currentlyusing Bump on Pad structures,41% are using RepassivatedWLCSPs, and 59% are usingRDL WLCSP structures.High silver solder alloys havebeen the mainstay of WLCSPtechnologies in the past, withSAC405 (64%) and SAC305(9%) being used for applications wherethermal cycling performance requirementspredominate. A growing interest in SAC105and doped alloy variants of SAC105 solderalloys was detected in the surveyresults, with more than 27% of respondentscurrently using this solder alloyfor drop test sensitive applications.Although backside coatings are notwidely used in WLCSP offerings today,the survey results suggest a high interestlevel in backside coatings, primarily toprovide improved die strength and sawingquality. More than 54% of respondentsindicated their interest in using backsidecoatings for improved reliability. Thedesire of end-users to avoid underfillingWLCSPs continues, with more thanFigure 3. SEM photomicrograph of a 0.4mm pitchWLCSP wafer. (Flip<strong>Chip</strong> International)60% of respondents not willing to considerusing underfill.The factors cited as most importantfor driving the adoption of WLCSPsinclude minimal footprint, low profile,low cost and high quality. Penetrationof WLCSPs into cellular handset applicationshas been pervasive. Adoption ofWLCSPs in automotive and medicalapplications has been more gradual, butclear momentum in broadening theproliferation of WLCSPs into automotiveand other higher reliability applicationsis apparent. Some remaining hurdles toWLCSP adoption that were mentionedinclude wafer level burn-in, board levelreliability requirements for finer pitchWLCSPs and the impact of productdesign specifics on WLCSP reliability.A substantial portion of the surveycovered users’ qualification requirementsfor WLCSPs. Because more than 80% ofWLCSPs today are used in cellularhandset applications, drop and boardbending tests were considered by mostrespondents to be the most importantreliability requirements. Over the pastfew years, gains in drop test performancehave been achieved through alloy andUBM optimization efforts, largely at theexpense of thermal cycling performance.Interest in achieving a more balancedreliability performance between thermalcycling and mechanical robustness isemerging.The qualification requirements ofWLCSP providers and users were a key<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ <strong>October</strong> <strong>2008</strong> ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com] 23

Figure 4. WLCSP end users preference metrics.component of this survey. These resultsare summarized in Table 1, and highlightthat the reliability expectations ofWLCSPs are being standardized due tothe high level of adoption in the cellularhandset application space.In the case of drop and bend testing, theJEDEC specifications seem to predominate.However, it is widely known in the industrythat Nokia drives its own drop testingstandards, and Motorola has been championingbend test methodology changes.With respect to thermal cyclingrequirements, ongoing efforts areunderway to maintain the demandingqualification requirements described inTable 1 for ever-increasing array sizes.From the survey, it was determined thatarray sizes as large as 15 × 15 (225 I/O)are emerging, and that the average WLCSParray size is between 5 × 5 (25 I/O) and6 × 6 (36 I/O). Recent examples of WLCSPproducts are highlighted in Figure 2 andFigure 3.How do the end users prioritize themetrics for ranking their WLCSP technologies?When asked to rank order thefactors that they and their customersvalue most for wider adoption ofWLCSP in terms of importance on ascale of 1 to 5 (5 being the most important),the answers are displayed inFigure 4. Six factors were consideredimportant, but low cost and small footprintboth topped the other parameterssuch as low profile, board mount performance,manufacturing quality, andpackage reliability.The WLCSP ForumThe WLCSP Forum was formed inSeptember 2007, driven by the need tofacilitate discussion among WLCSPassembly and test suppliers, chip solutionsuppliers and customers. The group’sobjectives are to promote the adoptionof semiconductor devices using WLCSPs,to establish industry-sponsored “bestpractices” for their utilization and toestablish strategies for migration to finerpitch WLCSP products. Besides being asource of information, the Forum providesthe chance to create a commonunderstanding for reliability and handlingissues, qualification strategies androadmap development in the field ofWLCSPs. For details, including contactinformation, a list of current members,and a membership application form,refer to www.wlcspforum.org. iSuperButton and SuperSpring Contact ElementsHigh current, high frequency, low inductanceFlexible Design for All Your Engineering Needs • No NRE for Custom FootprintsSuperButton Connector TechnologySuperSpring Connector TechnologyBoard-to-Boardor Board-to-FlexCustom InterposersLand Grid ArrayPackage-to-BoardSocketsEngineering Programming & Test Sockets• Connector free—lengths down to 1.0mm• Array counts over 2,000• Pitches down to 0.5mm• Mating against BGA, LGA, QFN, CSP or flexsales@hcdcorp.com www.hcdcorp.com (408) 743-9700 x331Copyright © 2006 High Conection Density, Inc. All rights reserved. Information is subject to change without notice. “SuperSpring” and “SuperButton” are trademarks of High Connection Density, Inc.24<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ <strong>October</strong> <strong>2008</strong> ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com]

INDUSTRY NEWSIDC Finds Solid Growth for Applications and Media ProcessorsFramingham, Mass.—Applications processorsand media coprocessors experiencedanother year of solid growth in 2007 asthe chipset technology that enables multimediahas become more mature andchipset pricing has declined. This hasenabled multimedia capabilities toquickly spread from high-end mobilephones into a myriad of mobile andconsumer electronics (CE) devices,according to IDC. Multimedia functionalitycan now be found in most mid-rangeand even some entry-level phone segments,as well as devices ranging from PMPs,handheld gaming platforms, MIDs,toys, PNDs, and a variety of medicaland industrial devices.“While 2006 was the year multimediafunctionality gained traction on mobilephones, 2007 was the year when it hit fullstride and started expanding into otherdevices,” said Flint Pulskamp, programmanager for Wireless Semiconductors.“Application processor and mediacoprocessor suppliers must continue topursue multimedia processing opportunitiesemerging from consumer, medical,and gaming products, in order to maintaina healthy revenue run rate and hedgeBuffalo, N.Y.—NanoDynamics Inc.reported that Dr. Alan Rae, the company’svice president of technology, has contributeda chapter entitled “NanotechnologyOpportunities in Green Electronics” tothe recently published book, Green ElectronicsDesign & Manufacturing: ImplementingLead-Free and RoHS-CompliantGlobal Products (McGraw-Hill, <strong>2008</strong>).“The compilation of synthesis techniquesknown as nanotechnology presentsmany opportunities to reshape theelectronics industry from top to bottom,”said Dr. Rae. “As part of the book’soverall aim to shed light on the importanceof green electronics design andmanufacturing, and how to actuallyproceed with it, I’m excited to haveagainst the rapid integration of the mobilephone market.”Key findings from IDC’s analysis of theworldwide device applications processorand multimedia coprocessor industryreport revenues for 2007 reached $2.9billion, a 14% increase from the prioryear. The leading supplier was TexasInstruments, which captured 27% ofthe market, followed by Marvell andRenesas. These top three suppliers controlledover 50% of the market, withmore than 20 other suppliers competingfor the remainder of the market.Findings specific to the worldwidemobile phone semiconductor industryincluded revenue growth of 9% to $23.4billion in 2007 due to the continuedmigration from 2.5G to 3G/3.5G technologies.QUALCOMM and TexasInstruments ranked as the two largestmobile phone semiconductor suppliersagain in 2007; however, their positionsswitched, as QUALCOMM became theleading supplier last year. MediaTekemerged as the third largest mobilephone semiconductor supplier in 2007with 78% overall revenue growth fromin 2006. [idc.com]Dr. Alan Rae Contributes Chapter to Book on Green Electronics Designbeen able to contribute information onnanotechnology’s role in this endeavor.“Offering uniform and reactive particleswith unusual optical thermal andelectronic properties, as well as the possibilityfor nanostructure materials andself-assembly, the field of nanotechnologyprovides myriad potential inaddressing green electronics initiatives—fromstreamlining material needsto reducing the amount of energyrequired for production,” explained Rae.Green Electronics Design &Manufacturing is edited by Sammy G.Shina, P.E., the founder of the NewEngland Lead-Free Consortium and aprofessor of mechanical engineering atthe University of Massachusetts, Lowell.TechSearch StudyShows Solid Flip <strong>Chip</strong>and WLP GrowthAustin, Texas—The growth of flip chipand wafer level packaging is a brightspot in the electronics industry.TechSearch International’s new study,“<strong>2008</strong> Flip <strong>Chip</strong> and WLP MarketTrends and Forecasts,” projects a compoundgrowth rate of more than 14percent for FC units and 14 percent forWLPs between 2007 and 2012.The drivers for flip chip continue tobe performance and form factor. Theuse of flip chip for a variety of wirelessproducts will contribute to the growthin 2009. An increasing number of suppliersof ASICs, field programmablegate arrays (FPGAs), DSPs, chipsets,graphics, and microprocessors areexpanding their use of flip chip withsolder bumps and copper pillars inpackage (FCIP). Flip chip on board(FCOB) continues to be found in automotiveelectronics, hard disk drives, andwatch modules. Many companies areplanning to use micro bumps for futurethrough silicon via (TSV) products.The growth in WLPs is driven byincreased demand for thinner, lighterweightportable products, but WLPs areadopted for both form factor and performancereasons. WLPs have typicallybeen used for low pin count (≤50 I/O)small die size applications, includinganalog devices such as power amplifiersand battery management devices,MOSFETs, image sensors, controllers,and integrated passives. However, WLPsare an option for larger die with pincounts ≥100. [techsearchinc.com]The book brings together contributionsfrom experts across the electronics supplychain that illustrate the strategy,design, testing and implementationissues necessary to meet global environmentalregulations affecting the electronicsindustry of today and tomorrow.[nanodynamics.com]<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ <strong>October</strong> <strong>2008</strong> ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com] 25

INTERNATIONAL DIRECTORY OF WAFER PROBERS AND PROBE CARDSCompanyAddressb PhonePROBERSModel Name and Number➤ Automation Level ApplicationsWI=Intact Wafers; DW=Diced Wafers;WLP=WLP; KGD=KGD; MEMS=MEMS;DL=Die on Leadframes; DM=Discrete andMultiple Die; WP=Wafer Profiling;ET=Electrical and Parametric TestO=OtherPROBE CARDSC Card TypeB=Blade; C=Cantilever; E=Epoxy;MS=Micro Spring; MDUT=Multi-DUT;V=Vertical; O=Other Testing Temperature Range (°C) Contact Resistance (C Res )T Tip Diameter/Tip Length (mils)P Pad MaterialWeb Site❉ Customer Contact Additional OfficesNote: Information contained in the listings isprinted as submitted by the respective suppliers.Advertisers are shown in boldface type.CM = Consult ManufacturerAccretech (TSK)Mitaka, JapanSubsidiary of Tokyo Seimitsu Co.Tokyo 181-8515, JapanPROBERUF3000EX➤ Automated WI, DW, WLP, KGD, DM,MEMS, WP, ETPROBERUF2000➤ Automated WI, DW, WLP, KGD, DM,MEMS, WP, ETaccretech.jp Accretech USA Inc.3400 Waterview Pkwy. #109Richardson, TX 75080b 1.800.784.4875❉ Scott Shollenberger, Nat. Sales Mgr.shollenbergers@accretechusa.comb 1.214.250.6844Cascade Microtech Inc.2430 NW 206th Ave.Beaverton, OR 97006b 1.503.601.1000PROBERSM150 measurement platform➤ Manual CMSummit 12000 probe stationwith Pureline technology➤ Semi-automatic, automatic CMPROBE CARDP30 Pyramid Probeproduction probe cardC CM CM CMT CMP CMcascademicrotech.com❉ Cali Sartor, Marketing Communicationscali_sartor@cmicro.comElectroglas Inc.5729 Fontanoso WaySan Jose, CA 95138b 1.408.528.3000CMCMelectroglas.com❉ info@electroglas.comFormFactor7005 South Front Rd.Livermore, CA 94551b 1.925.290.4000CMCMformfactor.com❉ info@formfactor.comInternational ContactTechnologies Inc.Southbury, CTb 1.203.264.5757PROBE CARDC MDUT, V, O=RF andlarge matrix probing -50° to 150°C CMT CM (dependent on probe size)P Al, Au, CuPROBE CARDC B (ceramic, ceramic striplineand metal), E CM CMT CMP CMict-probe.com❉ John King, Sales Directorjohnking@ict-probe.comb 1.203.264.5757JEM America Corp.Subsidiary ofJapan Electronic MaterialsAmagasaki-Shi, Japanb 1.925.290.4000PROBE CARDSVS Series probe cards,VS Series probe cards imagesensor device testingC CM CM CMT CMP CMPROBE CARDVC-430 Series probe cards forone-touch 300mm wafer testingC CM CM CMT CMP CMjemam.com JEM America Corp.Fremont, CA 94538❉ sales@jemam.comb 1.510.683.9234Micromanipulator Co.1555 Forest WayCarson City, NV 90706b 1.800.972.4032PROBE CARDP300A Semi-Automatic 300mmProbing Station with NetProbesoftwareC Semi-automatic CM CMT CMP CMPROBE CARDP300J Motorized, JoystickControlled 300mm Probing StationC Manual CM CMT CMP CMmicromanipulator.com❉ sales@micromanipulator.com26<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ <strong>October</strong> <strong>2008</strong> ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com]

INTERNATIONAL DIRECTORY OF WAFER PROBERS AND PROBE CARDSCompanyAddressb PhonePROBERSModel Name and Number➤ Automation Level ApplicationsWI=Intact Wafers; DW=Diced Wafers;WLP=WLP; KGD=KGD; MEMS=MEMS;DL=Die on Leadframes; DM=Discrete andMultiple Die; WP=Wafer Profiling;ET=Electrical and Parametric TestO=OtherPROBE CARDSC Card TypeB=Blade; C=Cantilever; E=Epoxy;MS=Micro Spring; MDUT=Multi-DUT;V=Vertical; O=Other Testing Temperature Range (°C) Contact Resistance (C Res )T Tip Diameter/Tip Length (mils)P Pad MaterialWeb Site❉ Customer Contact Additional OfficesNote: Information contained in the listings isprinted as submitted by the respective suppliers.Advertisers are shown in boldface type.CM = Consult ManufacturerProbeLogic Inc.1885 Lundy Ave. #101San Jose, CA 95131b 1.408.416.0777PROBE CARDG-ProbeC CM CM

Probe Mark Analysis—A Critical Windowon Actual Probe Card PerformanceProbe mark analysis provides a critical window on actual probe performance, allowingengineers to optimize probing processes and realize substantial economic returns.By Darren James, Product Manager, Rudolph Technologies Inc. [rudolphtech.com]Probe mark analysis (PMA) providesa critical link between thedata collected by probe card analyzers(PCA) and the actual performance ofthe probe card in the test cell. Systematicdiscrepancies between probe card testdata and actual on-wafer performancecan be corrected to improve visibility ofthe probing process. Real-time feedbackon probe performance enables knowledgebasedmaintenance and repair, eliminatingunnecessary downtime and yieldlosses associated with fixed interval orrun-to-fail maintenance methodologies.Other applications for device manufacturersinclude evaluating probingprocess capability to support pad shrinkdecisions, correlating probe mark datawith bin sort data to identify probe-relatedyield loss, and accelerating developmentcycles for new products and probingprocesses. Similarly, probe card manufacturersuse PMA to assure productquality, develop new probe technologies,and facilitate the integration of theirproducts into their customers’ testenvironment.Analysis or Probe Mark InspectionPMA differs from probe mark inspection,which typically looks at 100% of marksand is intended to detect, and perhapsclassify, defective marks. In contrast, probemark analysis seeks to derive informationfrom probe marks that can be used toimprove the process and only looks atas many marks as required to ensurestatistical validity.PMA uses a high-resolution opticalmicroscope for imaging, and a fast,precise motorized stage to navigate todesignated probe marks. Confocalmicroscopy may also be used fordetailed three-dimensional analyses.Data RichProbe marks are rich in information.The average value and variability of theminimum distance between the probemark and the edge of the pad determinesthe probing process capabilityindex (C pk ), the critical considerationfor pad shrink decisions. The marklengths reflect the planarity of the contacts.The mark widths increase asprobe tips wear. Pad size variabilityreflects the stability of the etch process.Positions of individual marks indicatealignment errors of individual probes,while fixed offsets are caused by errorsin the prober step function. Variationsin mark position that correlate withlocation on the wafer may indicatedeflection under load, thermal expansion,prober stage tilt, and much more.Correlations between probe mark characteristicsand bin sort data can revealcauses of yield loss in the probing process.Knowledge-Based MaintenanceUsing PMA to control probe cardmaintenance can yield immediateeconomic returns. Probe cards requireperiodic maintenance to clean andrepair probe tips that contact the wafer.As manufacturers have moved to parallelPCA OTWafer Scrub EndPCA & ScrubCenter PositionWafer Scrub StartPCA NOTFigure 1. Measurement terminologytesting, simultaneously testing multipledie, the costs of the probe cards andtester downtime for maintenance haveincreased dramatically.Under a run-to-fail methodology,probe cards are removed for maintenancewhen they begin to contributesignificantly to yield loss. Although thismaximizes the maintenance intervaland minimizes downtime, costly yieldloss is unavoidable. Alternatively, cardsmay be removed for maintenance aftera fixed interval, where the length of theinterval is chosen to be less than theexpected time to failure. As a result,fully functional cards are removed prematurelyand total downtime increases.Knowledge-based maintenanceapplies standard statistical process controltechniques to probe mark data 1 toanticipate the need for maintenance.Trends in the data can be used to reliablypredict card failure and the cardcan be removed for maintenance justbefore it fails, thus minimizing bothyield loss and maintenance downtime.Closed-Loop AnalysisThe fundamental principle of processcontrol is that optimal performance can<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ <strong>October</strong> <strong>2008</strong> ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com] 29

e achieved by minimizing process variabilityand then repeating known goodprocesses. The central problem in controllingprobing processes is that theprobes cannot be observed in use; forexample, in contact with the wafer duringtesting.Probe card analysis evaluates theprobes before use. PMA evaluates themarks left by the probe during use.Although neither allows direct observationof the probes in use, they can beused together in a closed-loop analysisto provide detailed characterization ofthe probing process.PCA typically measure the undeflectedprobe position, corresponding to theno-over-travel (NOT) position at whichthe probe first contacts the wafer; andthe deflected probe position, correspondingto its over-travel (OT) positionafter it has scraped through the oxidizedpad surface to ensure good electricalcontact. To a first approximation, theNOT and OT positions predict thebeginning and end of the probe mark.However, several differences betweenthe analysis environment and the testcell introduce discrepancies in this correlation(Figure 1).Frictional forces between the probeand the test surface are different thanbetween the probe and the probe pad,and the test surface does not deform asthe pad surface does. The probe cardanalyzer cannot exactly reproduce allaspects of the mechanical and thermalbehavior of the probe card in the testenvironment, such as deflection underload or heat flows and temperature differentials.Still, probe marks contain awealth of information about probe performancein use.Closed-loop modeling 2 uses correctionsderived from PMA to improve thequality of performance predictionsbased on probe card analysis. Often theidentification of a systematic discrepancyoffers important clues about the underlyingphysical mechanism. The two caseMicronsOverTravelCenterScrubMicronsNoOverTravel3129272523211917152520151050-5-10-15-20PCAWafer and PCA Scrub LengthWafer ScrubPCA Scrubs vs. Wafer ScrubsWafer Scrub End@TempWafer Scrub EndPCA OTWafer Scrub Center@TempWafer Scrub CenterPCA CenterWafer Scrub Start@TempWafer Scrub StartPCA NOTFigure 2. Comparison of PCA and PMA data for Case Study 1studies that follow demonstrate significantimprovement in the correlationbetween predicted and actual probemark characteristics. In both studies,the array is less than 100mm in size andcontains approximately 4000 probes.Data CorrelationIn the first study (Figure 2), a comparisonof PCA and PMA data shows goodcorrelation (2.1µm @ 3σ) in the lateralposition (perpendicular to scrub direction).Measurements in the scrub directionshow some discrepancies. On theupper left of Figure 2, the actual marksare shorter than PCA NOT-OT. On theupper right, for larger probe diameters,PCA NOT starts earlier and actual markstarts later. On the lower left, uncorrectedlength data shows poor correlation. Onthe lower right, the correlation improvesafter correction.OTParallelNOTOTParallelNOTNo Overtravel Position (Microns)Over 20Travel1510CenterScrub 5Microns0-2-4-6-8-10-12-14-16250No -5OverTravel-10-15-20PCA NOT Edge Position vs. Wafer ScrubStart PositionPCA-NOTWafer Scrub Start-AmbientWafer Scrub Start-TempOTPredictive PCA Scrubs vs. Wafer ScrubsWafer Scrub EndPCA Predicted OTWafer Center ScrubPCA Predictive CenterWafer Scrub StartPCA Predictive NOTParallelNOTProbe Diameter“Skating” describes the tendency ofthe probe to slide over the pad surfacefor some distance before the markbegins, thus shortening the expectedmark length. As expected, the marks inthe data set begin beyond the NOT.However, the marks also terminatebeyond the OT position, resulting inmark lengths that are essentially equalto the NOT-OT distance and longerthan expected.The absence of shortening indicates adifference in over-travel between the PCAand the test cell. The PCA and PMA centerpositions show a correlation of 7.2µm@ 3σ in the scrub direction.An interesting relationship also existsbetween mark length and mark width.As a probe tip wears, its diameterincreases and so does the width of theprobe mark. The larger diameter alsoincreases the length of the probe markOTParallelNOT30<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ <strong>October</strong> <strong>2008</strong> ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com]

Could you bemakingADDITIONALMILLION$ fromyour Test Floor?Johnstech has developed a Test Floor AnalysisPresentation/Tool utilizing real-life ProductionTest Cell information to show how much:· Component Life and Spares Cost influence COO· Maintenance (Cleaning & Rebuilding) Ease and Frequency affect Test Timeand therefore Productivity/Efficiency· Even a 1% Yield Enhancement can change your entire profit picture· Increased Upbinning ability can push profits past the MILLION-DOLLAR markLearn how you could make ADDITIONAL MILLIONS from your Test Floor! Contact your JohnstechRepresentative TODAY and ask to see the Increase Profits from Test Presentation/Tool.(To find your Johnstech Representative, go to www.johnstech.com and click on the link at the upper right of the homepage.)The Increase Profits from Test Presentation will be given at ITC (InternationalTest Conference & Exhibition) on <strong>October</strong> 28, <strong>2008</strong>, between 2 & 4PM.Check it out and/or stop by Booth #502 for more information.High Performing Products.Superior Service.Exceptional Value.Your Partner-in-Test!

MicronsOverTravelCenterScrubNoOverTravelMicrons30282624222018161412102520151050-5-10-15-20-25-30PCA Probe Diameter vs. Wafer Scrub WidthProbe DiameterScrub WidthScrub Correlation: PWX vs. Wafer ScrubRadial PositionPCA Scrub OTWafer Scrub EndWafer Scrub End@TempWafer Scrub CenterPCA Probe CenterWafer Scrub Center@TempWafer Scrub Start@TempWafer Scrub StartPCA Scrub NOTFigure 3. Comparison of PCA and PMA data for Case Study 2calculated from the bottom of the probediameter at NOT to the top of the probediameter at OT.Increased tip diameter has the oppositeeffect on actual probe marks, as thebroader tip skates further and the markbegins later. Thus, worn tips make marksthat are wider and shorter. When correctionsfor overtravel differential andskating are applied to the PCA data, thecorrelation between the predicted (PCA)and actual (PMA) measurementsimproved to 2.6µm for mark position(a 2.7× improvement) and 3.7µm formark length (a 1.4× improvement).In the second study (Figure 3), thereis again good correlation between PCAand PMA lateral position data (2.2µm@ 3σ). In the scrub direction, there isgood correlation for position, but markOTParallelNOTMicronsOverTravel 10Center 0Scrub-5-10NoOverTravel-15Microns4035302520152520155-20-25Scrub Length vs. Radial Position in Probe ArrayPCA Predictive Scrub vs. Wafer ScrubPCA Predicted OTWafer Scrub EndPCA Predictive CenterWafer Scrub CenterPCA Predictive NOTWafer Scrub StartArray CenterPCA Wafer Scrub Wafer Scrub@Templengths are significantly shorter overall(11µm) and vary with distance from thecenter of the wafer (longer in the middle),and marks start much later (6µm) thanthe PCA NOT position. Mark widthsare 12µm less than the probe diametersmeasured by the PCA.Interestingly, mark lengths are alsoshorter by approximately the sameamount, leading to the conclusion thatthe optically measured PCA diameter(which reflects the diameter of the baseof the cone shaped tip) does not correspondto the effective mechanical diameterdetermined by the depth to whichthe tip penetrates the pad surface.In the upper left of Figure 3, PCAprobe diameter measurements aremuch larger than mark widths. In theupper right, the mark lengths vary withOTParallelNOTdistance from center of array, but PCAmeasurements do not. In the lower left,the uncorrected length data shows poorcorrelation. In the lower right, the correlationimproves after correction.Finally, PCA lengths show little or nodependence on distance from the wafercenter, but actual marks are significantlylonger near the center. The marks alsoexhibit a fairly constant offset betweenmeasurements made at ambient andelevated temperatures. When PCA dataare corrected for tip diameter and radialdistance, correlation between the predictedvalues and actual measurementsgoes to 2.3 for length (down from 11µm,a 4.7× improvement) and 1.5µm forcenter position (a 1.6× improvement).ConclusionPMA provides a critical window on actualprobe performance, allowing engineers tooptimize probing processes and realizesubstantial economic returns. Knowledgebasedmanagement of probe card maintenanceminimizes downtime and yieldloss. Closed-loop modeling allows betterpredictions of actual performance fromprobe card measurements and deliversoptimized probe cards to the test cell.Correlation of probe mark characteristicswith bin sort data can reveal causesof yield loss in the probing process. Preciseknowledge of probing process capabilityensures successful reductions in pad size.Ultimately, PMA can enable higher yieldsand shorter development cycles throughputthe probing process. iReferences1. Darren Coil, Statistical Process Control for theSort Area, IEEE Semiconductor Wafer Test Workshop<strong>2008</strong>, http://www.swtest.org/swtw_library/<strong>2008</strong>proc/PDF/S03_03_Coil_SWTW<strong>2008</strong>.pdf2. John Strom, Closing the Loop: Incorporationof Sort Floor Data to Improve Probe CardPerformance, IEEE Semiconductor Wafer TestWorkshop 2007, http://www.swtest.org/swtw_library/2007proc/PDF/S02_03_Strom_SWTW2007.pdf32<strong>Chip</strong> <strong>Scale</strong> <strong>Review</strong> ■ <strong>October</strong> <strong>2008</strong> ■ [<strong>Chip</strong><strong>Scale</strong><strong>Review</strong>.com]