1. xerox 560 computer system - The UK Mirror Service

1. xerox 560 computer system - The UK Mirror Service

1. xerox 560 computer system - The UK Mirror Service

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

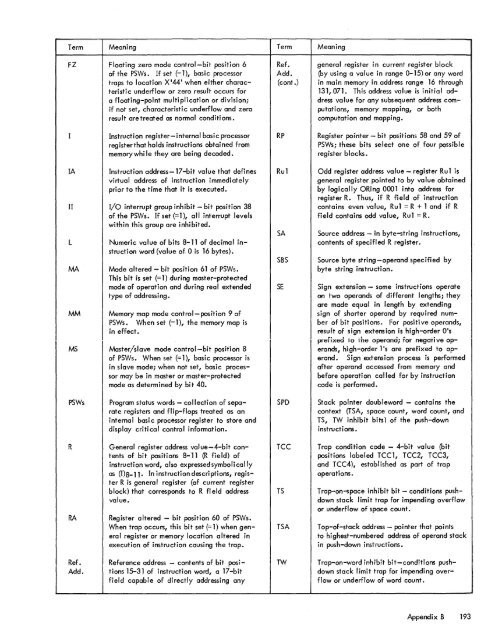

TermMeaningTermMeaningFZFloating zero mode control-bit position 6of the PSWs. If set (=1), basic processortraps to location X·44· when either characteristicunderflow or zero result occurs fora floating-point multiplication or division;if not set, characteristic underflow and zeroresu It are treated as normal conditions.Ref.Add.(cont .)general register in current register block(by using a value in range 0-15) or any wordin main memory in address range 16 through131,07<strong>1.</strong> This address value is initial addressvalue for any subsequent address computations,memory mapping, or bothcomputation and mapping.Instruction register-internal basic processorregister that holds instructions obtained frommemorywhile they are being decoded.RPRegister pointer - bit positions 58 and 59 ofPSWs; these bits select one of four possibleregister blocks.IAIILMAMMMSInstruction address- 17~bit value that definesvirtual address of instruction immediatelyprior to the time that it is executed.I/o interrupt group inhibit - bit position 38of the PSWs. If set (=1), all interrupt levelswithin this group are inhibited.Numeric value of bits 8-11 of decimal instructionword (value of. 0 is 16 bytes).Mode altered - bit position 61 of PSWs.This bit is set (= 1) during master-protectedmode of operation and during real extendedtype of addressing.Memory map mode control-position 9 ofPSWs. When set (=1), the memory map isin effect.Master/slave mode control-bit position 8of PSWs. When set (=1), basic processor isin slave mode; when not set, basic processormay be in master or master-protectedmode as determined by bit 40.Ru1SASBSSEOdd register address value - register Ru1 isgeneral register pointed to by value obtainedby logically ORing 0001 into address forregister R. Thus, if R field of instructioncontains even value, Ru 1 = R + 1 and if Rfield contains odd value, Ru1 = R.Source address - in byte-string instructions,contents of speci fi ed R reg ister.Source byte string-operand specified bybyte string instruction.Sign extension - some instructions operateon two operands of different lengths; theyare made equal in length by extendingsign of shorter operand by required numberof bit positions. For positive operands,result of sign extension is high-order O·sprefixed TO Tne operano; Tor negative operands,high-order l·s are prefixed to operand.Sign extension process is performedafter operand accessed from memory andbefore operation called for by instructioncode is performed.PSWsProgram status words - collection of separateregisters and flip-flops treated as aninternal basi c processor register to store anddisplay criti cal control information.SPDStack pointer doubleword - contains thecontext (TSA, space count, word count, andTS, TW inhibit bits) of the push-downinstructions.RRAGeneral register address value-4-bit contentsof bit positions 8-11 (R field) ofinstruction word, also expressedsymbolicallyas (I)8-1<strong>1.</strong> In instruction descri ptions, registerR is general register (of current registerblock) that corresponds to R fi eld addressvalue.Register altered - bit position 60 of PSWs.When trap occurs, this bit set (= 1) when generalregister or memory location altered inexecution of instruction causing the trap.TCCTSTSATrap condition code - 4-bit value (bitpositions labeled TCC1, TCC2, TCC3,and TCC4), established as part of trapoperations.Trap-on-space inhibit bit - conditions pushdownstack limit trap for impending overflowor underflow of space count.Top-of-stack address - pointer that pointsto highest-numbered address of operand stackin push-down instructions.Ref.Add.Reference address - contents of bit positions15-31 of instruction word, a 17-bitfield capable of directly addressing anyTWTrap-on-word inhibit bit-conditions pushdownstack limit trap for impending overflowor underflow of word count.Appendix B 193