Specman Based Verification Methodology for ... - CiteSeerX

Specman Based Verification Methodology for ... - CiteSeerX

Specman Based Verification Methodology for ... - CiteSeerX

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

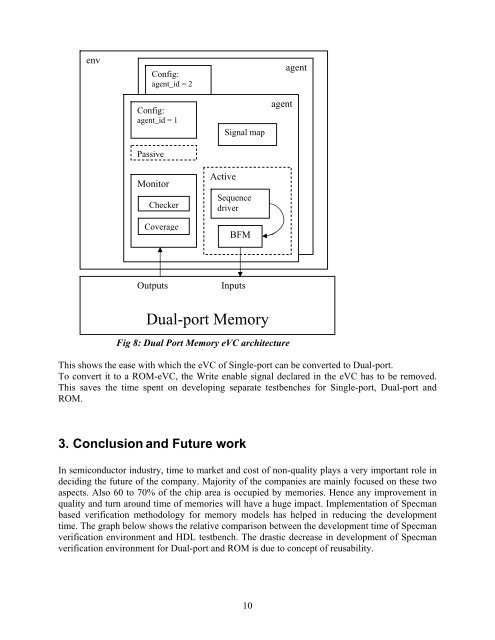

envConfig:agent_id = 2Config:agent_id = 1PassiveMonitorCheckerCoverageSignal map mapActiveSequencedriverBFMagentagentOutputsInputsDual-port MemoryFig 8: Dual Port Memory eVC architectureThis shows the ease with which the eVC of Single-port can be converted to Dual-port.To convert it to a ROM-eVC, the Write enable signal declared in the eVC has to be removed.This saves the time spent on developing separate testbenches <strong>for</strong> Single-port, Dual-port andROM.3. Conclusion and Future workIn semiconductor industry, time to market and cost of non-quality plays a very important role indeciding the future of the company. Majority of the companies are mainly focused on these twoaspects. Also 60 to 70% of the chip area is occupied by memories. Hence any improvement inquality and turn around time of memories will have a huge impact. Implementation of <strong>Specman</strong>based verification methodology <strong>for</strong> memory models has helped in reducing the developmenttime. The graph below shows the relative comparison between the development time of <strong>Specman</strong>verification environment and HDL testbench. The drastic decrease in development of <strong>Specman</strong>verification environment <strong>for</strong> Dual-port and ROM is due to concept of reusability.10