- Page 1 and 2:

Intel ® 945G/945GZ/945GC/ 945P/945

- Page 3 and 4:

Contents 1 Introduction ...........

- Page 5 and 6:

4.2.11 C0DRC1—Channel A DRAM Cont

- Page 7 and 8:

6.1.16 DMICESTS—DMI Correctable E

- Page 9 and 10:

9.4.5 SMM Space Decode and Transact

- Page 11 and 12:

11.3 DC Characteristics ...........

- Page 13 and 14:

Revision History Rev Description Da

- Page 15 and 16:

Intel ® 82945G/82945GZ/82945GC/829

- Page 17 and 18:

1 Introduction Introduction The Int

- Page 19 and 20:

Figure 1-2. Intel ® 945GZ/82945GC

- Page 21 and 22:

1.1 Terminology Term Description Ac

- Page 23 and 24:

Term Description TOLM Top Of Low Me

- Page 25 and 26:

Introduction � Supports four bank

- Page 27 and 28:

Introduction 1.4 Graphics (Intel ®

- Page 29 and 30:

1.5 Analog and SDVO Displays (Intel

- Page 31 and 32:

2 Signal Description Signal Descrip

- Page 33 and 34:

2.1 Host Interface Signals Signal D

- Page 35 and 36:

Signal Name Type Description HREQ[4

- Page 37 and 38:

2.3 DDR2 DRAM Channel B Interface S

- Page 39 and 40:

Signal Description 2.6 Analog Displ

- Page 41 and 42:

2.8 Direct Media Interface (DMI) Si

- Page 43 and 44:

2.10 Power and Ground Name Voltage

- Page 45 and 46:

Interface Signal Name I/O System Me

- Page 47 and 48:

Interface Signal Name I/O State Dur

- Page 49 and 50:

3 Register Description Register Des

- Page 51 and 52:

Register Description Note: A physic

- Page 53 and 54:

3.3 Configuration Mechanisms Regist

- Page 55 and 56:

3.4 Routing Configuration Accesses

- Page 57 and 58:

3.4.2.2 DMI Configuration Accesses

- Page 59 and 60:

Bit Access & Default 10:8 R/W 000b

- Page 61 and 62:

Host Bridge/DRAM Controller Registe

- Page 63 and 64:

4.1 Device 0 Configuration Register

- Page 65 and 66:

4.1.4 PCISTS—PCI Status (D0:F0) P

- Page 67 and 68:

4.1.7 MLT—Master Latency Timer (D

- Page 69 and 70:

4.1.12 EPBAR—Egress Port Base Add

- Page 71 and 72:

Host Bridge/DRAM Controller Registe

- Page 73 and 74:

Host Bridge/DRAM Controller Registe

- Page 75 and 76:

Host Bridge/DRAM Controller Registe

- Page 77 and 78: 4.1.19 PAM1—Programmable Attribut

- Page 79 and 80: 4.1.21 PAM3—Programmable Attribut

- Page 81 and 82: 4.1.23 PAM5—Programmable Attribut

- Page 83 and 84: 4.1.25 LAC—Legacy Access Control

- Page 85 and 86: Host Bridge/DRAM Controller Registe

- Page 87 and 88: 4.1.29 ERRSTS—Error Status (D0:F0

- Page 89 and 90: 4.1.31 SKPD—Scratchpad Data (D0:F

- Page 91 and 92: Host Bridge/DRAM Controller Registe

- Page 93 and 94: Host Bridge/DRAM Controller Registe

- Page 95 and 96: 4.2.7 C0DCLKDIS—Channel A DRAM Cl

- Page 97 and 98: 4.2.9 C0DRT1—Channel A DRAM Timin

- Page 99 and 100: Bit Access & Default 6:4 R/W 000b 3

- Page 101 and 102: Host Bridge/DRAM Controller Registe

- Page 103 and 104: 4.2.24 PMSTS—Power Management Sta

- Page 105 and 106: 4.3.1 EPESD—EP Element Self Descr

- Page 107 and 108: 4.3.3 EPLE1A—EP Link Entry 1 Addr

- Page 109 and 110: Host-PCI Express* Bridge Registers

- Page 111 and 112: Address Offset Host-PCI Express* Br

- Page 113 and 114: 5.1.3 PCICMD1—PCI Command (D1:F0)

- Page 115 and 116: 5.1.4 PCISTS1—PCI Status (D1:F0)

- Page 117 and 118: 5.1.7 CL1—Cache Line Size (D1:F0)

- Page 119 and 120: 5.1.12 IOBASE1—I/O Base Address (

- Page 121 and 122: 5.1.15 MBASE1—Memory Base Address

- Page 123 and 124: Host-PCI Express* Bridge Registers

- Page 125 and 126: 5.1.20 INTRLINE1—Interrupt Line (

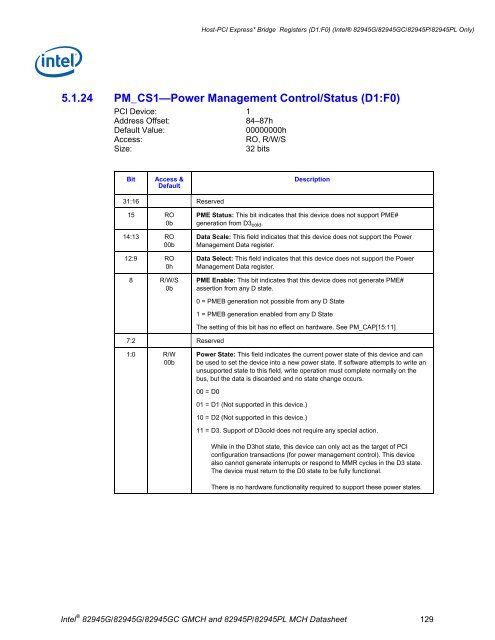

- Page 127: Bit Access & Default 2 R/W 0b 1 R/W

- Page 131 and 132: Host-PCI Express* Bridge Registers

- Page 133 and 134: 5.1.29 MA—Message Address (D1:F0)

- Page 135 and 136: 5.1.33 DCAP—Device Capabilities (

- Page 137 and 138: 5.1.35 DSTS—Device Status (D1:F0)

- Page 139 and 140: 5.1.37 LCTL—Link Control (D1:F0)

- Page 141 and 142: 5.1.39 SLOTCAP—Slot Capabilities

- Page 143 and 144: 5.1.41 SLOTSTS—Slot Status (D1:F0

- Page 145 and 146: 5.1.43 RSTS—Root Status (D1:F0) P

- Page 147 and 148: Host-PCI Express* Bridge Registers

- Page 149 and 150: Host-PCI Express* Bridge Registers

- Page 151 and 152: Host-PCI Express* Bridge Registers

- Page 153 and 154: 5.1.56 ESD—Element Self Descripti

- Page 155 and 156: Host-PCI Express* Bridge Registers

- Page 157 and 158: 5.1.61 CESTS—Correctable Error St

- Page 159 and 160: Host-PCI Express* Bridge Registers

- Page 161 and 162: Direct Media Interface (DMI) RCRB 6

- Page 163 and 164: 6.1.3 DMIPVCCAP2—DMI Port VC Capa

- Page 165 and 166: 6.1.6 DMIVC0RCTL—DMI VC0 Resource

- Page 167 and 168: 6.1.9 DMIVC1RCTL—DMI VC1 Resource

- Page 169 and 170: 6.1.13 DMILSTS—DMI Link Status MM

- Page 171 and 172: 6.1.15 DMIUEMSK—DMI Uncorrectable

- Page 173 and 174: Integrated Graphics Device (D2:F0)

- Page 175 and 176: Integrated Graphics Device (D2:F0)

- Page 177 and 178: 7.1.4 PCISTS2—PCI Status (D2:F0)

- Page 179 and 180:

7.1.7 CLS—Cache Line Size (D2:F0)

- Page 181 and 182:

7.1.11 IOBAR—I/O Base Address (D2

- Page 183 and 184:

Integrated Graphics Device (D2:F0)

- Page 185 and 186:

7.1.20 MINGNT—Minimum Grant (D2:F

- Page 187 and 188:

Integrated Graphics Device (D2:F0)

- Page 189 and 190:

Integrated Graphics Device (D2:F0)

- Page 191 and 192:

Integrated Graphics Device (D2:F1)

- Page 193 and 194:

8.1.3 PCICMD2—PCI Command (D2:F1)

- Page 195 and 196:

8.1.5 RID2—Revision Identificatio

- Page 197 and 198:

Integrated Graphics Device (D2:F1)

- Page 199 and 200:

Integrated Graphics Device (D2:F1)

- Page 201 and 202:

Integrated Graphics Device (D2:F1)

- Page 203 and 204:

8.2 Device 2 - PCI I/O Registers In

- Page 205 and 206:

9 System Address Map System Address

- Page 207 and 208:

Figure 9-1. System Address Ranges 4

- Page 209 and 210:

Compatible SMRAM Address Range (A_0

- Page 211 and 212:

9.2 Main Memory Address Range (1 MB

- Page 213 and 214:

9.3 PCI Memory Address Range (TOLUD

- Page 215 and 216:

9.3.6 PCI Express* Graphics Attach

- Page 217 and 218:

9.4.1 SMM Space Definition System A

- Page 219 and 220:

9.4.5 SMM Space Decode and Transact

- Page 221 and 222:

9.4.12 Legacy VGA and I/O Range Dec

- Page 223 and 224:

10 Functional Description This chap

- Page 225 and 226:

Interleaved Mode Functional Descrip

- Page 227 and 228:

667 MHz (PC 5300) (82945G/82945GC/8

- Page 229 and 230:

10.2.2.2 System Memory Supported Co

- Page 231 and 232:

Functional Description Table 10-5.

- Page 233 and 234:

10.3 PCI Express* (Intel ® 82945G/

- Page 235 and 236:

Figure 10-2. SDVO Conceptual Block

- Page 237 and 238:

Figure 10-3. Concurrent SDVO / PCI

- Page 239 and 240:

10.5 Integrated Graphics Device (In

- Page 241 and 242:

10.5.3 4X Faster Setup Engine Funct

- Page 243 and 244:

10.5.4 Texture Engine Functional De

- Page 245 and 246:

10.5.4.8 Pixel Shader Functional De

- Page 247 and 248:

Functional Description to determine

- Page 249 and 250:

10.5.6 2D Engine Functional Descrip

- Page 251 and 252:

10.5.8.1 Cursor Plane Functional De

- Page 253 and 254:

Functional Description device is in

- Page 255 and 256:

10.6.2 Digital Display Interface Fu

- Page 257 and 258:

10.6.2.1.5 Control Bus Functional D

- Page 259 and 260:

Figure 10-7 illustrates the various

- Page 261 and 262:

11 Electrical Characteristics Elect

- Page 263 and 264:

11.1.1 Power Characteristics Table

- Page 265 and 266:

Signal Group Electrical Characteris

- Page 267 and 268:

11.3 DC Characteristics Table 11-5.

- Page 269 and 270:

Symbol Signal Group Electrical Char

- Page 271 and 272:

Ballout and Package Information 12

- Page 273 and 274:

Ballout and Package Information Fig

- Page 275 and 276:

12.2 Ballout Table Ballout and Pack

- Page 277 and 278:

Ballout and Package Information EXP

- Page 279 and 280:

Ballout and Package Information HA2

- Page 281 and 282:

Ballout and Package Information HD6

- Page 283 and 284:

Ballout and Package Information RSV

- Page 285 and 286:

Ballout and Package Information SDM

- Page 287 and 288:

Ballout and Package Information SDQ

- Page 289 and 290:

Ballout and Package Information SDQ

- Page 291 and 292:

Ballout and Package Information VCC

- Page 293 and 294:

Ballout and Package Information VCC

- Page 295 and 296:

Ballout and Package Information VCC

- Page 297 and 298:

Ballout and Package Information VSS

- Page 299 and 300:

Ballout and Package Information VSS

- Page 301 and 302:

Ballout and Package Information VSS

- Page 303 and 304:

Ballout and Package Information VSS

- Page 305 and 306:

12.3 Package § Ballout and Package

- Page 307 and 308:

Ballout and Package Information Int

- Page 309 and 310:

13.2 XOR Test Mode Initialization T

- Page 311 and 312:

13.4 XOR Chains Testability Table 1

- Page 313 and 314:

Table 13-5. XOR Chain 2 Pin Count B

- Page 315 and 316:

Table 13-8. XOR Chain 5 Pin Count B

- Page 317 and 318:

Table 13-11. XOR Chain 8 Pin Count