DATA SHEET - Glyn High-Tech Distribution

DATA SHEET - Glyn High-Tech Distribution DATA SHEET - Glyn High-Tech Distribution

HX8346-A(T)240RGB x 320 dot, 262K color, TFT Mobile Single Chip DriverD ) Timing Format of GRAM- Data ReadDATA SHEET V01SCL InputNCSStartEndSDI(Iutput)Start byteSDO(Output)Dummy read(8 bits)GRAM read 1 GRAM read 2 GRAM read 3 GRAM read 4Note:A RAM data read operation follows 8 bits dummy read operations .Note: This figure is specified transfer format (multi read)Figure 5. 18 Data Read Timing in Serial Bus System InterfaceHimax ConfidentialThis information contained herein is the exclusive property of Himax and shall not be distributed, reproduced, or disclosedin whole or in part without prior written permission of Himax.-P.47-July, 2007

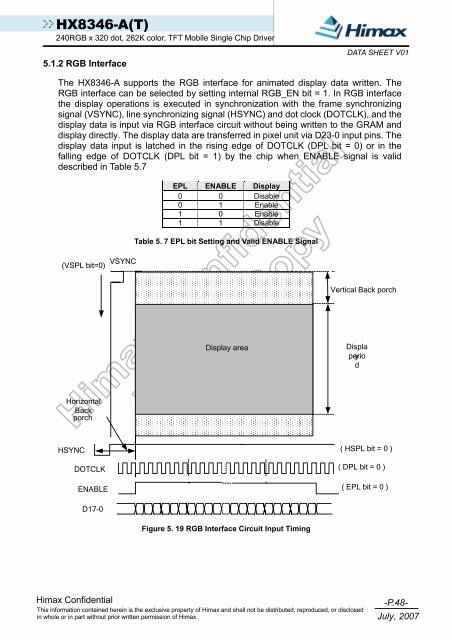

HX8346-A(T)240RGB x 320 dot, 262K color, TFT Mobile Single Chip Driver5.1.2 RGB InterfaceDATA SHEET V01The HX8346-A supports the RGB interface for animated display data written. TheRGB interface can be selected by setting internal RGB_EN bit = 1. In RGB interfacethe display operations is executed in synchronization with the frame synchronizingsignal (VSYNC), line synchronizing signal (HSYNC) and dot clock (DOTCLK), and thedisplay data is input via RGB interface circuit without being written to the GRAM anddisplay directly. The display data are transferred in pixel unit via D23-0 input pins. Thedisplay data input is latched in the rising edge of DOTCLK (DPL bit = 0) or in thefalling edge of DOTCLK (DPL bit = 1) by the chip when ENABLE signal is validdescribed in Table 5.7EPL ENABLE Display0 0 Disable0 1 Enable1 0 Enable1 1 DisableTable 5. 7 EPL bit Setting and Valid ENABLE Signal(VSPL bit=0)VSYNCVertical Back porchDisplay areaDisplaperio ydHorizontalBackporchHSYNCDOTCLKENABLE( HSPL bit = 0 )( DPL bit = 0 )( EPL bit = 0 )D17-0Figure 5. 19 RGB Interface Circuit Input TimingHimax ConfidentialThis information contained herein is the exclusive property of Himax and shall not be distributed, reproduced, or disclosedin whole or in part without prior written permission of Himax.-P.48-July, 2007

- Page 1 and 2: DATA SHEET( DOC No. HX8346-A(T)-DS

- Page 3 and 4: HX8346-A(T)240RGB x 320 dot, 262K c

- Page 5 and 6: HX8346-A(T)240RGB x 320 dot, 262K c

- Page 7 and 8: HX8346-A(T)240RGB x 320 dot, 262K c

- Page 9 and 10: HX8346-A(T)240RGB x 320 dot, 262K c

- Page 11 and 12: HX8346-A240RGB x 320 dot, 262K colo

- Page 13 and 14: HX8346-A(T)240RGB x 320 dot, 262K c

- Page 15 and 16: HX8346-A(T)240RGB x 320 dot, 262K c

- Page 17 and 18: HX8346-A(T)240RGB x 320 dot, 262K c

- Page 19 and 20: HX8346-A(T)240RGB x 320 dot, 262K c

- Page 21 and 22: NO.1NO.302PADA1PADB1DUMMYR1DUMMYR2P

- Page 23 and 24: HX8346-A(T)240RGB x 320 dot, 262K c

- Page 25 and 26: HX8346-A(T)240RGB x 320 dot, 262K c

- Page 27 and 28: HX8346-A(T)240RGB x 320 dot, 262K c

- Page 29 and 30: HX8346-A(T)240RGB x 320 dot, 262K c

- Page 31 and 32: HX8346-A(T)240RGB x 320 dot, 262K c

- Page 33 and 34: HX8346-A(T)240RGB x 320 dot, 262K c

- Page 35 and 36: HX8346-A(T)240RGB x 320 dot, 262K c

- Page 37 and 38: HX8346-A(T)240RGB x 320 dot, 262K c

- Page 39 and 40: HX8346-A(T)240RGB x 320 dot, 262K c

- Page 41 and 42: HX8346-A(T)240RGB x 320 dot, 262K c

- Page 43 and 44: HX8346-A(T)240RGB x 320 dot, 262K c

- Page 45 and 46: HX8346-A(T)240RGB x 320 dot, 262K c

- Page 47: HX8346-A(T)240RGB x 320 dot, 262K c

- Page 51 and 52: HX8346-A(T)240RGB x 320 dot, 262K c

- Page 53 and 54: HX8346-A(T)240RGB x 320 dot, 262K c

- Page 55 and 56: HX8346-A(T)240RGB x 320 dot, 262K c

- Page 57 and 58: HX8346-A(T)240RGB x 320 dot, 262K c

- Page 59 and 60: HX8346-A(T)240RGB x 320 dot, 262K c

- Page 61 and 62: HX8346-A(T)240RGB x 320 dot, 262K c

- Page 63 and 64: HX8346-A(T)240RGB x 320 dot, 262K c

- Page 65 and 66: HX8346-A(T)240RGB x 320 dot, 262K c

- Page 67 and 68: HX8346-A(T)240RGB x 320 dot, 262K c

- Page 69 and 70: HX8346-A(T)240RGB x 320 dot, 262K c

- Page 71 and 72: HX8346-A(T)240RGB x 320 dot, 262K c

- Page 73 and 74: HX8346-A(T)240RGB x 320 dot, 262K c

- Page 75 and 76: HX8346-A(T)240RGB x 320 dot, 262K c

- Page 77 and 78: HX8346-A(T)240RGB x 320 dot, 262K c

- Page 79 and 80: HX8346-A(T)240RGB x 320 dot, 262K c

- Page 81 and 82: HX8346-A(T)240RGB x 320 dot, 262K c

- Page 83 and 84: HX8346-A(T)240RGBx320 dots, 262,144

- Page 85 and 86: HX8346-A(T)240RGBx320 dots, 262K co

- Page 87 and 88: HX8346-A(T)240RGBx320 dots, 262K co

- Page 89 and 90: HX8346-A(T)240RGBx320 dots, 262K co

- Page 91 and 92: HX8346-A(T)240RGBx320 dots, 262K co

- Page 93 and 94: HX8346-A(T)240RGBx320 dots, 262K co

- Page 95 and 96: HX8346-A(T)240RGBx320 dots, 262K co

- Page 97 and 98: HX8346-A(T)240RGBx320 dots, 262K co

HX8346-A(T)240RGB x 320 dot, 262K color, TFT Mobile Single Chip Driver5.1.2 RGB Interface<strong>DATA</strong> <strong>SHEET</strong> V01The HX8346-A supports the RGB interface for animated display data written. TheRGB interface can be selected by setting internal RGB_EN bit = 1. In RGB interfacethe display operations is executed in synchronization with the frame synchronizingsignal (VSYNC), line synchronizing signal (HSYNC) and dot clock (DOTCLK), and thedisplay data is input via RGB interface circuit without being written to the GRAM anddisplay directly. The display data are transferred in pixel unit via D23-0 input pins. Thedisplay data input is latched in the rising edge of DOTCLK (DPL bit = 0) or in thefalling edge of DOTCLK (DPL bit = 1) by the chip when ENABLE signal is validdescribed in Table 5.7EPL ENABLE Display0 0 Disable0 1 Enable1 0 Enable1 1 DisableTable 5. 7 EPL bit Setting and Valid ENABLE Signal(VSPL bit=0)VSYNCVertical Back porchDisplay areaDisplaperio ydHorizontalBackporchHSYNCDOTCLKENABLE( HSPL bit = 0 )( DPL bit = 0 )( EPL bit = 0 )D17-0Figure 5. 19 RGB Interface Circuit Input TimingHimax ConfidentialThis information contained herein is the exclusive property of Himax and shall not be distributed, reproduced, or disclosedin whole or in part without prior written permission of Himax.-P.48-July, 2007